引言

变频调速技术广泛应用于工业领域。随着电力电子控制技术及元器件的不断发展,变频调速系统的集成度、智能化程度越来越高,硬件构成也越来越紧凑、简单。DSP(数字信号处理器)+IPM(智能功率模块)就是变频调速系统最新的发展方向之一。

在DSP+IPM构成的变频调速系统中,充分利用了DSP高速运算、配置丰富及IPM控制信号接口简单、保护完善的特点,使得系统元器件数大为减少、结构紧凑,而性能及可靠性却大为提高,缩短了产品开发周期,提高了产品的竞争力。

笔者为某设备所做的一个变频调速子系统就采用了DSP+IPM的结构。下面介绍该系统的硬件设计方法。

硬件设计

DSP和IPM

该系统工况为24小时连续工作制。要求受上位机控制,控制两路电机的启动、停止、转速及加速度,同时将掉电及故障信号反馈给上位机。系统要求结构紧凑、体积小、保护功能完善、稳定可靠。系统输入电压为3Φ 200VAC。控制的两路电机功率分别为180W。根据以上要求,我们采用了DSP+IPM的硬件结构。

因为系统要求实时控制两路电机的运行,我们选用了TI公司的专为电机控制设计的TMS320L2407A型DSP。该DSP采用了高性能静态CMOS 技术,时钟频率可达40MHZ,指令周期仅为25ns,可实现3.3V低功耗设计,满足实时控制要求。尤其值得一提的是该DSP具有用于电机控制的专用外围配置―两个事件管理模块EVA和EVB,每个模块包括:两个16位通用定时器;8个16位PWM通道;三个外部事件的时间标记捕获单元;可编程的死区时间以防止直通故障;在片位置编码器接口电路;同步A./D转换器等,可方便地实现对两路电机的控制。另外,该型DSP还有多达40个可单独编程的复合通用输入/输出引脚、多达5个外部中断等配置,对实际应用带来很大方便。

因为该系统输入电压为3Φ 200VAC,控制的两路电机功率均为180W,考虑适当裕量,我们选用了三菱公司第三代DIP- IPM PS21563(10A/600V)。三菱DIP-IPM是面向AC100~200V级小容量电机变频驱动、采用传递型封装结构、将功率电路和驱动保护电路集成于一体的小型智能功率模块,具有以下特点:

·3相AC变频输出电路搭载三菱第5代平面型IGBT和CSTBT(Carrier Stored Trench-gate Bipolar Transistor:具有载流子蓄积层的沟槽型门极构造双极晶体管)功率芯片,实现更低损耗。

·采用自举电路结构,可实现单电源驱动。

·内置有IGBT驱动电路,具有过载保护、控制电源欠压保护功能。P侧具有UV(控制电源欠压)保护功能,但不输出故障信号F。N侧具有UV及SC(过载)保护功能,同时输出故障信号F。

·内置专用HVIC(高压600VIC),无需隔离绝缘电路(如光耦),可由DSP或3V级单片机直接驱动。

·输入接口电路采用高电平驱动逻辑,消除了旧产品低电平驱动方式对电源投入和切断时的时序要求,增强了模块自保护能力。

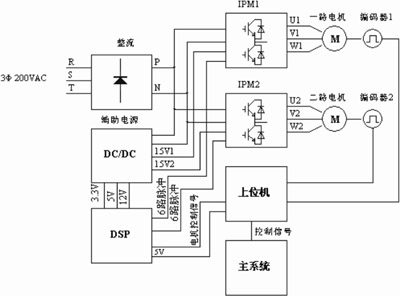

系统输入为3Φ 200VAC,经三相全桥整流为约270VDC供给IPM,并由270V进行DC/DC转换产生辅助电源,为DSP、上位机及IPM 模块提供控制电源。上位机接受主系统控制,对DSP发出2路电机起停、4级加速度及8级速度的控制信号,DSP根据上位机的控制信号产生两组6路脉冲分别控制两个IPM模块,从而控制两路电机的起停、加速度及转速。两路电机的转速通过轴编码器反馈回上位机。IPM的故障信号反馈给DSP,DSP将故障信号及掉电信号反馈回上位机。系统框图如图1所示。

图1 系统原理框图

自举电路

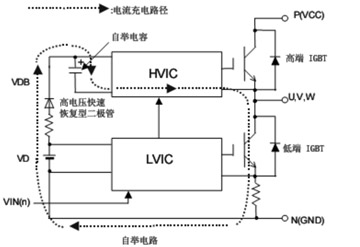

一般逆变电路中,因上臂3个IGBT的触发脉冲的参考地是悬浮的,故上臂触发脉冲需3组相互隔离的电源供电。下臂3个IGBT的触发脉冲是共参考地的,只需一组供电电源。故共需多达4组相互隔离的电源。而三菱公司的DIP-IPM采用自举电路结构,可方便地实现单电源驱动。具体工作原理如下:当 DIP-IPM起动时,先给下臂IGBT发出足够的充电脉冲数或足够宽的单个脉冲,开通下臂(N侧)的IGBT,使下臂的供电电源通过IPM的内部充电路径使上臂的3个自举电容完全充电,从而给上臂的3个IGBT的触发脉冲供电。然后才开始发出PWM控制脉冲。自举电路充电路径及工作时序图如图2所示。

图2 自举电路充电路径及工作时序图

自举电容C1的容值计算公式为C1=IBS X T1/△V,式中T1为上臂IGBT的最大通态(ON)脉宽,IBS为IC的驱动电流(考虑温度和频率特性),△V为允许的放电电压。注意,用该式计算出的自举电容容值应是最小值,实际选择时应增加一定裕量。

自举电阻R2的阻值选择应满足下述条件:时间常数R2 X C1能使放电电压(△V)在下臂IGBT的最小导通脉宽(T2)内被充电到C1上。即 R2={(VD-VDB) X T2}/(C1 X △V),式中VD为电源电压,VDB为自举电容C1上电压。

自举二极管选择:对3Φ 200VAC电路,若电源输入电压波动范围取±30%,则三相全桥整流后直流电压 VD=200 X 1.3 X 1.35=351(V),取最小裕量为1.5,则自举二极管耐压应为351 X 1.5=526.5(V),取600V。故自举二极管额定电压最小应为600V,因为PWM载波频率较高(最大为20KHZ),推荐选用快恢复二极管(反向恢复时间小于100nS)。

硬件设计要点

根据笔者设计该系统的经验,硬件设计应注意以下方面,以提高系统抗干扰性,使之在强干扰的现场工业环境中能可靠稳定运行。

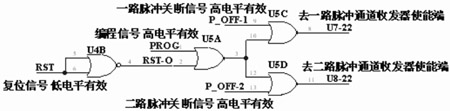

·虽然DIP-IPM模块可由DSP直接驱动,但实际调试时发现,在上电及对DSP进行flash编程过程中,DSP的引脚有时会出现不确定状态,产生干扰脉冲导致IPM的上、下臂IGBT直通引起短路保护动作。故我们在DSP到IPM的两组触发脉冲通道中分别加了一个八通道、双电源3态门转换收发芯片74LVC4245,该芯片的输出使能端由一个简单的逻辑门电路控制,如图3所示。以确保在上电及对DSP进行flash编程时不会有干扰脉冲误触发 IPM。

图3 控制触发脉冲通道通、断的逻辑门电路

·为防止信号振荡,应在各输入端加RC退耦电路。对两组触发脉冲来说,RC电路一来可滤掉干扰脉冲,二来还可限制输入脉冲的最小脉宽。RC容量的选择要和PWM的载波频率匹配,使得既能滤掉干扰信号,又不对触发脉冲造成畸变。因为DIP-IPM输入部分IC内置2.5KΩ(min)下拉电阻,故RC中 R阻值的选择应注意使分压后的信号值满足DIP-IPM的输入电平阈值要求。

·DIP-IPM还有一个很实用的功能:短路保护。在本系统的软件调试过程中,该功能多次发挥作用,可靠地保护了模块,使本系统样机调试过程中IPM模块无一损坏。但要使该功能可靠发挥作用,应注意以下两点:

1)外部电流检测电阻的信号回路必须设置RC滤波电路,以免短路保护误动作。RC时间常数的选择要考虑IGBT的硬中断能力,一般推荐为 1.5~2μS,最大不超过6μS。时间常数过短可能引起短路保护误动作,过长则可能超出IPM模块的耐受能力,不能有效保护IPM模块。

2)外部电流检测电阻应为无感电阻,该电阻及其信号引线到IPM模块对应引脚的布线应尽可能短,以免由引线电感干扰引起短路保护误动作。

·PCB布板时应注意采取以下抗干扰措施:

1)强电(功率部分)和弱电(控制部分)从区域上分开。

2)数字地(控制地)和模拟地(功率地)分开布局,只能在一点相接。一定要注意避免功率地线上的电流流经控制地线,以免引入地线干扰。

3)PCB上IPM模块相邻触发脉冲引脚间可开槽,避免相互干扰。

4)电流检测电阻及其信号线、触发脉冲信号及所有电容到IPM模块的布线要尽可能短,尽量降低其引线电感引起的干扰。

结语:

该系统已批量生产上千台,投入现场连续运行三年多。实际运行表明,该系统运行稳定,工作良好。可以预计,DSP+IPM模式将是紧凑型变频调速系统的发展方向之一。

参考文献:

[1] TMS320LF2407A DSP controller,TI,2002

[2] DIP-IPM version3 应用技术资料,三菱电机株式会社,2003