摘 要:近年来,随着FPGA电路在军工和航天领域的广泛应用,用户对FPGA 电路的可靠性要求也越来越高。在集成电路的可靠性*估试验中,动态老化试验是最重要的试验之一,FPGA 动态老化技术的实现可以提高FPGA 电路的可靠性。文章通过研究FPGA 电路内部结构和功能模块,讨论FPGA 电路加载配置过程的原理和流程,通过对动态老化和静态老化的对比试验和结果分析,研究出FPGA 电路动态老化试验方法,并在工程实践中得到了成功实现和应用。

1 引言

FPGA 是现场可编程门阵列(Field ProgrammingGate Array)的缩写,用户可以编写程序对FPGA 内部的逻辑模块和I/O 模块重新配置,以实现芯片的逻辑功能。近年来,FPGA芯片以其大规模、高集成度、高可靠性、投资少、保密性好、开发方便、使用灵活、可在线编程等优点得到了广泛的应用。随着FPGA 电路在军工和航空航天领域的应用,其高可靠性尤为重要,为了提高电路的可靠性,最好的方法是对电路进行筛选,其中老化试验就是筛选过程中最为重要的环节之一。

考虑到FPGA 电路的工作模式比较复杂,外部需要存储器或者FLASH 对其进行配置,FPGA 才能动态工作,因此国内一般的FPGA 老化技术都采用了静态老化试验方法。这种静态老化试验方法存在着一定的缺陷,电路在老化过程中并没有受到真正的应力,因此并不能真正剔除掉早期失效的产品,其可靠性得不到保证。对FPGA 电路动态老化的研究,提高老化试验条件的严酷度,即可保证电路的高可靠性要求。

2 动态老化试验

集成电路的动态老化理论上要求电路在其最高温度工作条件下完全模拟实际工作状态,电路内部的逻辑单元都有机会得到翻转,对于一般数字集成电路都需要外部提供功能测试码来驱动电路工作。

对于FPGA 电路的动态老化试验来说,功能测试码是存储在外部存储器中的配置程序,将程序配置到FPGA 电路内部,使内部的门阵列全部工作起来,实现高覆盖率的逻辑节点的翻转,让其按照规定的功能工作。因此本研究工作的关键在如何进行FPGA电路的程序配置。

3 FPGA设计流程

完整的FPGA 设计流程包括逻辑电路设计输入、功能仿真、综合及时序分析、实现、加载配置、调试。FPGA 配置就是将特定的应用程序设计按FPGA设计流程转化为数据位流加载到FPGA 的内部存储器中,实现特定逻辑功能的过程。由于FPGA 电路的内部存储器都是基于RAM 工艺的,所以当FPGA电路电源掉电后,内部存储器中已加载的位流数据将随之丢失。所以,通常将设计完成的FPGA 位流数据存于外部存储器中,每次上电自动进行FPGA电路配置加载。

4 FPGA配置原理

以Xilinx公司的Qpro Virtex Hi-Rel系列XQV100电路为例,FPGA的配置模式有四种方案可选择:MasterSerial Mode,Slave Serial Mode,Master selectMAPMode,Slave selectMAP Mode。配置是通过芯片上的一组专/ 复用引脚信号完成的,主要配置功能信号如下:

(1)M0、M1、M2:下载配置模式选择;

(2)CLK:配置时钟信号;

(3)DONE:显示配置状态、控制器件启动;

(4)PROG_B:初始化引出端;

(5)INT_B:配置延迟控制,配置错误显示;

(6)DOUT:菊花链中的配置数据输出。

(7)DIN:串行数据输入;

FPGA 电路在选定模式下的配置过程包括四个主要阶段:

(1)清除FPGA 电路内部配置存储器;

(2)初始化FPGA 电路配置逻辑功能;

(3)加载FPGA 电路配置数据流;

(4)FPGA 电路配置完成,启动电路就绪序列。

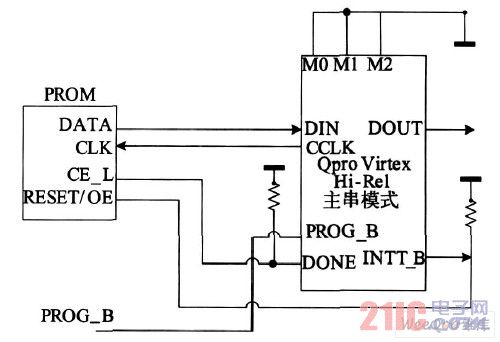

主串模式电路连接图见图1。

图1 FPGA 配置主串模式连接图

系统或芯片上电后,信号引脚PROG_B被拉低,FPGA的配置RAM存储器清空;同样,PROG_B上的逻辑低电平将会复位配置逻辑,并使FPGA 保持在清空配置存储器状态。只要PROG_B 引脚保持低电平,则FPGA 将继续清空它的配置RAM存储器,并使INIT_B 信号保持为低电平以表明配置在被清空。

当PROG_B被释放时,FPGA将继续使INIT_B保持低电平,直到完成清空所有的配置存储器。FPGA 在INIT_B信号的上升沿检测其模式引脚M0、M1、M2。

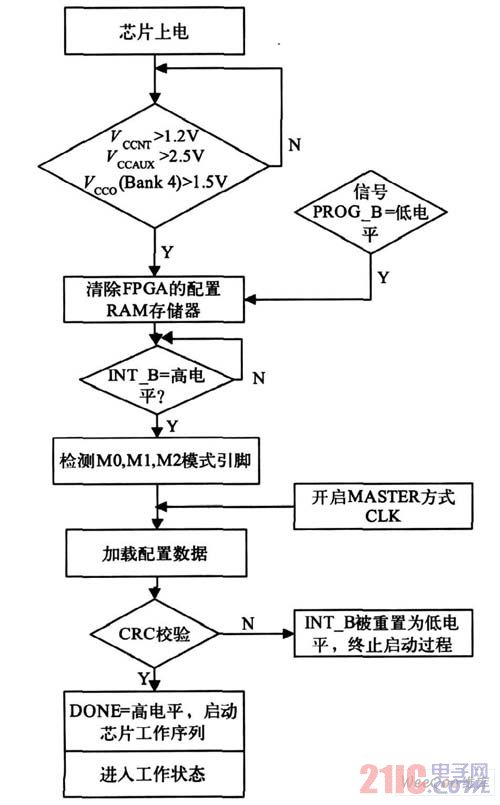

INIT_B 信号变为高电平后,配置就可以开始了,不需要额外的暂停或等待周期。但是,配置过程不必在INIT_B 变化之后就立即开始。配置逻辑只有当位流的同步字被载入时才开始处理数据。当上电清除配置RAM存储器后,INIT_B信号引脚变高电平,可以开始载入配置数据:标准的位流首先是引入空闲字FFFFFFFFh,其次是同步字AA995566h,然后是一些配置控制信息,紧跟其后的才是真正的位流数据帧和相关的CRC;位流的最后是CRC 校验和启动芯片进入工作态。FPGA 电路配置流程图如图2 所示。

图2 FPGA 电路配置流程图

5 FPGA动态老化板的设计

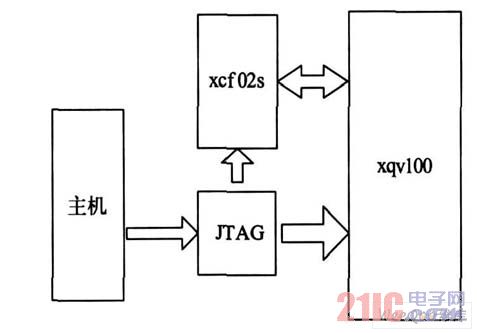

根据以上讨论的配置原理,我们设计了XQV100型FPGA 电路动态老化板,如图3 所示。配置模式采用主串方式(Master Serial Mode),这种配置模式有利于简化PCB 的设计,并且主串模式的配置时钟源于FPGA内部,不需要外部另外再提供。为了使FPGA电路工作在主串模式,电路的M1、M2、M3 引脚都应接地。同时,该模式下的外部配置存储器需要选用串行数据传输的存储器,在这里我们选用Xilinx公司的xcf02s 存储器,内部存储容量最大可达2 Mbit。

FPGA电路动态老化板采用400mm×400mm的双层PCB 板,在设计老化板时采用去耦及高、低频RC滤波,对直流电源和信号源采取限流措施。每块老化板上设计4 个老化工位,为了便于在线调试电路,每个工位由一个XCF02S、一个JTAG 接口、一个XQV100 组成。FPGA 芯片动态配置的逻辑程序放置于xcf02s Flash存储器中。FPGA动态老化的配置程序采用VHDL 语言编写,采用ISE(V9.1)工具进行综合,利用ModelSim(V6.0)进行功能模拟,其具体功能是把全部输入、输出管脚分五组,每组都实现32 分频功能,每组由外部提供一个1MHz 的方波信号作为输入。计算机通过Xilinx 专用的JATG 下载线将编译过的配置程序下载到xcf02s 电路中。当FPGA电路上电时,xcf02s 中的配置程序自动按照串行的方式下载到FPGA 的内部RAM存储器中,FPGA 按照程序的功能运行。每个电路选择一个输出端口,输出频率在1Hz 左右,在外部连接一个LED 灯作为输出监控,在老化的过程中可通过该灯观察电路是否正常工作。

图3 FPGA 电路动态老化板原理图

6 结果与分析

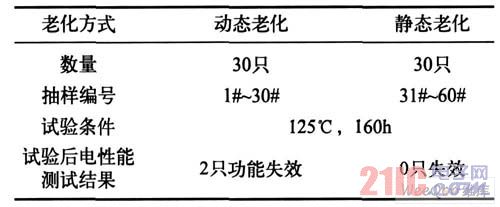

我们以XQV100 型FPGA电路为例,进行动态老化和静态老化对比试验,试验条件选择温度为125℃,时间160h。随机抽样60 只常温测试合格电路,各取30 只分别按照动态老化试验方法和静态老化试验方法进行老化。在动态老化通电时,确保每只电路都有输出;静态老化试验时,确保电源电压输入正确。每1h 记录一次,确认是否有老化异常情况。

电路在经过26h 后,其中有1 只(6#)电路LED不闪烁,初步怀疑已经失效,但并没有立即取出,和其他电路一样经过160h 老化,经过126h 后21# 电路的LED 不闪烁,同样继续陪试。在老化试验结束后96h内完成了所有电路的常温电测试,发现6# 和21# 电路功能失效,其余电路都合格,具体情况详见表1。

表1 动态老化和静态老化比对试验结果

动态老化试验方法和静态老化试验方法相比,动态老化试验在通过外围配置电路的程序驱动,使电路的内部功能模块一直处于高速的工作状态,相反静态老化时虽然有电压加载,但没有配置程序驱动电路工作,内部模块并一直处于空闲状态,因此FPGA 电路在动态老化时,所受到的应力条件更加严酷,更容易暴露电路本身潜在的缺陷,从而提高了电路本身的可靠性。

7 结束语

目前,国内进行FPGA 电路的老化大部分还是采用静态老化试验方法。特点是电路老化时不工作,内部门阵列不翻转,老化过程中无法判断电路是否有异常。FPGA电路动态老化试验方法的实现解决了这些问题,增加了输出监测点,保证了电路老化过程无异常,从而提高了电路的可靠性。

本文通过对FPGA 电路加载配置过程的流程和原理进行研讨,设计了FPGA 电路动态老化的试验方法,并在工程实践中得到了成功的实现和运用。

虽然这里设计的电路和配置过程针对Xilinx 公司的Qpro Virtex Hi-Rel 系列XQV100电路,但是对其他系列和其他公司FPGA 的动态配置也有参考作用。本方法虽然实现了动态老化的目的,但还是存在着缺陷:现有FPGA电路的内部门数已经超过了100万门,一般的配置程序只能占用FPGA 电路的部分内部资源,并且用到的D 触发器多了,则移位寄存器就少,通常是顾此失彼,因此要做到100%的动态老化试验还存在着一定的困难。