CPLD" title="CPLD">CPLD是复杂的PLD,专指那些集成规模大于1000门以上的可编程逻辑器件。它由与阵列、或阵列、输入缓冲电路、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多时钟驱动、内含ROM或FLASH(部分支持在系统编程)、可加密、低电压、低功耗以及支持混合编程技术等突出特点。而且CPLD的逻辑单元功能强大,一般的逻辑在单元内均可实现,因而其互连关系简单,电路的延时就是单元本身和集总总线的延时(通常在数纳秒至十数纳秒),并且可以预测。所以CPLD比较适合于逻辑复杂、输入变量多但对触发器的需求量相对较少的逻辑型系统。

MAX7000" title="MAX7000">MAX7000系列产品与高速数据采集系统的要求相符,十分适合于高速设计。由MAX7000系列CPLD设计的高速数据采集系统已经应用在电力系统某精确故障定位系统中。

1 高速数据采集系统的硬件结构

对于一般的高速数据采集系统而言,除了采用高速的A/D转换器、高速存储器等高速器件之外,还要解决如何高速寻址、如何控制总线逻辑、如何进行高速存储以及如何方便地与PC机交换数据等问题。这些问题都是设计一个高速数据采集系统所要共同面对的问题。兼顾这些共性问题,笔者设计了一套以精确故障定位为目的的高速数据采集系统。

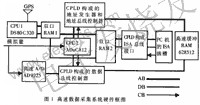

该系统的硬件框图如图1所示。在没有故障发生的时候,输入的模拟量通过高速AD芯片AD9225(其转换速率可达到25MSPS,分辨率为12位)转换成数字量,然后通过CPLD构成的数据总线控制器,以高4位和低8位的形式分别存储在两片横向并联的缓冲RAM 628512(存储时间为70ns)中。存储地址由CPLD构成的地址发生器产生,地址发生器产生的地址范围可由存储器的容量决定。地址产生器循环计数,数据循环存储。此间的运行完全不需要CPU控制,系统硬件可自动完成高速数据采集,使硬件的高速性能得到充分运用。CPU2采用AD公司的AduC812,它本身就是全集成的高性能12位数据采集系统,内部集成了1个12位的ADC。当其检测到输入的模拟量发生了突变时,再经过预定的持续采集时间后,给出触发信号到数据总线控制器和地址总线控制器,由CPU2取得数据总线和地址总线控制权,然后通过双口RAM2以及CPLD构成的ISA总线接口,将缓冲RAM 628512中的数据传入PC机。再联合由GPS、CPU1和双口RAM1构成的精确授时系统,就可用于精确故障定位或故障录波了。

2 MAX7000系列CPLD及其开发平台介绍

由于高速数据采集系统的特殊要求,在众多的CPLD器件中,选择了ALTERA公司的MAX系列器件。MAX系列的高性能和高密度是基于它先进的MAX(Multiple Array Matrix--多重阵列矩阵)架构,因此为高速应用提供了非常高的性价比。MAX7000系列还提供了业界速度最快的可编程逻辑解决方案。它基于CMOS EEPROM工艺,传播延迟最小为3.5ns,可以实现速度高于200MHz的计数器,并且为高密度的器件提供了非常宽的选择余地,十分适合高速设计时应用。该公司的MAX+plusII软件是一款易于使用的开发工具,其界面友好,集成化程度高,兼容工业标准,支持FLEX\MAX\ACEX 1K等系列产品。并且为大学提供了学生版软件,在功能上与商业版类似,仅在可使用的芯片上受限制。由于MAX7000系列的这些优点,以下的设计都基于MAX7000系列产品。

3 CPLD在高速寻址中的应用

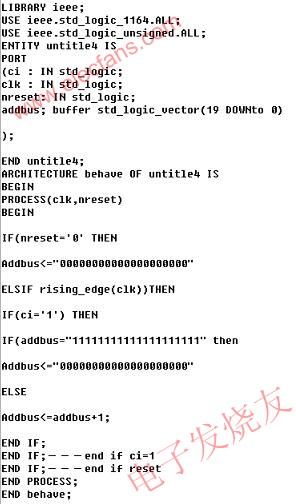

一般的数据采集均需由CPU将A/D转换的结果读入,然后再转存到片外的存储器中,这样至少需要4个机器周期。如果按照一般一个机器周期为1μs,那么最高采样率只能达到250kHz,绝难满足高速采样的需要。在本系统中,直接将采样数据存到高速缓冲RAM中,而存储器寻址则采用ALTERA公司的EPM7032LC44-6构成的地址发生器来完成。写信号可采用A/D转换的时钟信号,但需经过一系列分频及逻辑组合,也可另由电路产生或放在地址发生器中。EPM7032LC44-6构成地址发生器的基本原理是采用5片级联的74161组成20位的同步计数器,第20位接在高速缓冲RAM的片选线上,用来切换缓冲存储器组。用CPU2的P1.7控制计数允许端,异步清零,则20位地址线输出保持同步。其具体的实现可以采用图形编辑输入或者文本编辑输入的方法。下面给出其VHDL语言程序。

其仿真结果如图2所示。

4 CPLD构成数据总线控制器

在这个高速数据采集系统中,为了提高数据传输和寻址的速度,在正常采样期间,其数据总线和地址总线并不需要CPU控制,数据存储是由系统硬件自动完成的。但当CPU2监测到输入模拟量的突变时,再经过预定的一段持续采样时间后,就会发出控制信息给地址发生器和数据总线控制器,停止继续存储采样数据和自动产生地址,而由CPU2取得总线的控制权,对处在高速缓冲RAM中的故障前后数据进行操作。为避免总线冲突,就需要一块数据总线的控制器处理好系统总线和局部总线的关系。

EPM7064可以很好地解决这个问题。在EPM7064的内部,用三态门将CPU2的读写控制线、8根数据总线以及AD9225的12根数据线及一根溢出线与控制高速缓冲RAM的读写控制线和数据线隔离开来,由CPU2的P1.7作为CPU2或高速A/D控制总线的控制信号线,这样就能方便地实现缓冲RAM数据线访问控制权的切换。考虑篇幅,不再详细给出实现程序。地址总线控制逻辑实现方法类似,不再介绍。

5 CPLD构成的ISA总线接口

在PC系列机中,I/O空间是独立的,共有1KB(地址编号为000H~3FFH)。由于I/O接口一部分分布在主机母板上,另一部分分布在扩展槽上,所以I/O的1024个口地址也分成两个部分,其中前512个由母板上的接口控制器使用,后512个供扩展槽内的接口控制卡使用。而且由于后512个地址中的一部分已经被配置成系统资源的接口,所以真正能被用户设计开发的I/O端口为数不多,而且不连续。这样就不能采用常规的用PC机提供的地址总线来寻址双口RAM的方法,因为这种方法只能寻址其中为数不多而且不连续的一些单元。所以这是一个难点。为此,采用用PC机的数据线来寻址双口RAM的方式,只需占用三个I/O端口,就能寻址整个4K的RAM区。

欢迎转载,本文来自电子发烧友网(www.elecfans.com)

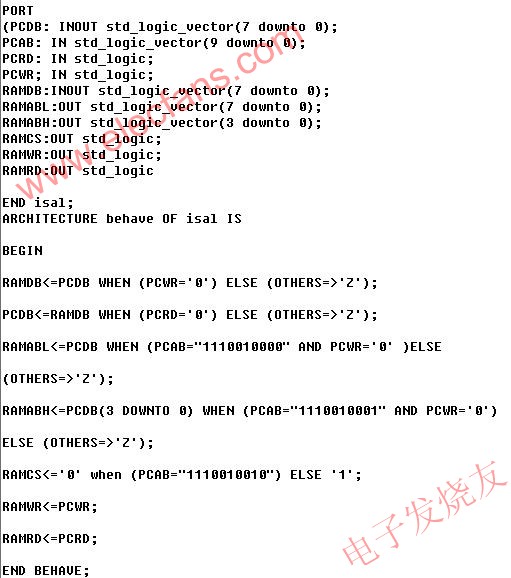

ISA总线接口电路逻辑框图如图3所示。

采用了ISA插槽中的8位数据线、10位地址线、读写控制线IOW和IOR以及电源线,并假设使用390H、391H、392H三个端口。当PC机要访问某一地址单元时,首先通过390H端口将低8位地址送到数据总线上。此时由PC-AB送出的390H信号和IOW信号经解码电路输出一个锁存脉冲到锁存器(L),将此低8位地址锁存;然后通过391H端口将高4位地址送到数据总线上,此时由PC-AB送出的391H信号和IOW信号经解码电路输出一个锁存脉冲到锁存器(H),将此高4位地址锁存;最后通过392H端口进行读写,只要PC-AB上出现392H信号,解码电路就输出一个低电平到双口RAM的/CS,再根据相应的读写控制信号就能进行读写操作。

用ALTERA公司的EPM7064SLC84-5实现这一接口的VHDL文件如下:

仿真结果表明此电路设计完全可以实现上述功能。PC机使用端口392H读取双口RAM中的数据时的仿真图如图4所示。

CPLD是现代电子工程领域的一门新技术,它提供了基于计算机和信息技术的电路系统设计方法,提高了设计电路的集成度和可靠性。笔者在将ALTERA公司推出的MAX7000系列产品应用于高速数据采集方面做了尝试,具体使用EPM7032和EPM7064设计了地址发生器、数据总线控制器和ISA总线的接口,目前已经将其应用在电力系统某精确故障定位系统中。