基于龙芯2F的车载和便携设备系统设计

摘要: 基于龙芯2F(LOONGSON-2F )处理器的车载和便携设备设计方案主要面向车载娱乐、超移动设备(UMD)、移动Internet 设备(MID)等高性能、低功耗嵌入式领域从事开发和生产的公司企业。该方案采用龙芯2F(LOONGSON-2F )处理器为控制核心,根据车载和便携设备工作环境和特点,采用SM502 [3]多功能显示控制芯片,它能够支持多种媒体格式,可实现上网、看电视、录制和播放音乐等功能;板载FLASH 和DDR2 内存,可独立引导系统内核工作,利用串口作为系统终端。也可通过板载的通用PCI 和LOCAL BUS 总路线接口进行系统扩展,方便用户进行二次开发,加之CPU 使用国产芯片,具有功耗低、价格低廉的特性,该设计方案具有较高的应用和参考价值。

Abstract:

Key words :

近年来,车载和便携式多媒体播放设备倍受人们追捧,竞相推出多种设计方案。基于龙芯2F(LOONGSON-2F )处理器的车载和便携设备设计方案主要面向车载娱乐、超移动设备(UMD)、移动Internet 设备(MID)等高性能、低功耗嵌入式领域从事开发和生产的公司企业。该方案采用龙芯2F(LOONGSON-2F )处理器为控制核心,根据车载和便携设备工作环境和特点,采用SM502 [3]多功能显示控制芯片,它能够支持多种媒体格式,可实现上网、看电视、录制和播放音乐等功能;板载FLASH 和DDR2 内存,可独立引导系统内核工作,利用串口作为系统终端。也可通过板载的通用PCI 和LOCAL BUS 总路线接口进行系统扩展,方便用户进行二次开发,加之CPU 使用国产芯片,具有功耗低、价格低廉的特性,该设计方案具有较高的应用和参考价值。

1. 龙芯2F 处理器的功能与特点

本系统采用的龙芯2F(LOONGSON-2F )处理器,是中国科学院计算技术研究所最新发布的一款64 位MIPSⅢ指令集的通用RISC 微处理器。该处理器在国内首个采用了90nmCMOS 设计工艺,面积为35nm2,典型工作频率800MHz 下实测功耗为4"5W ,最高工作频率可达1G;最高浮点运算速度为每秒40/80 亿次双/单精度浮点运算,片内集成了PCI/PCIX 等IO 控制器,并集成片上二级CACHE、DDR2 内存控制器,非常适合高端嵌入式领域。

2. 系统硬件结构设计

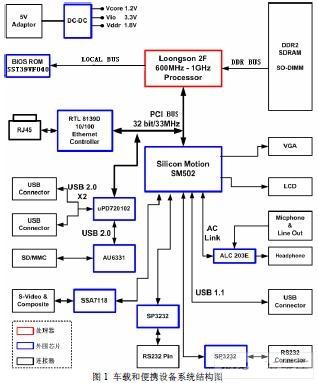

系统的结构框架如图1 所示。

龙芯2F(LOONGSON-2F )处理器为整个系统的控制中心,并承担所有数据的处理任务。系统通过ICS950220 时钟合成器产生主板上各芯片所需的时钟,同时该芯片带有看门狗功能。系统内存是通过处理器内部集成的DDR2 控制器扩展,考虑到PCB 印制板的面积和访存更高的带宽需求,采用4 片16bit 位宽的内存颗粒方案,内存容量取决于采用颗粒的容量,最大可支持1GB 内存,其工作频率为300MHz 。通过处理器提供的LOCAL BUS 扩展512KB Flash ROM 用于系统BIOS 存储。

2.1 系统电源

无论是车载还是便携设备均需需采用直流电源供电,因此,节能和和高效是电源设计的主题。图1 的电源模块可见,本系统主板采用了+5V 的直流适配器作为供电电源,供给CPU 使用的1.2V 和供给接口电路使用的3.3V 直流电源由于通过的电流比较大,均采用效率较高的开关电源。按照常规设计,供给DDR2 和SM502 使用的1.8V 电源由3.3V 电源引入,分别由两个线性电源(LDO)产生,本系统均改成效率较高的开关电源实现,提高了整个系统的效率,实测整个系统的功耗控制在10W 以内。

2.2 系统接口

1、系统通过多功能显示控制芯片SM502 驱动各种接口,SM502 可通过PCI BUS 直接与处理器相连,支持2D 显示加速,可提供:AC97 标准音频接口(通过ALC203 芯片控制)、一个UBS1.1 接口、一个标准RS232 串口和一个调试串口(均由SP3232 芯片控制)、VGA 和LCD 显示接口、ZV 视频接口(由SSA7118 芯片控制)。

2、系统通过PCI BUS 采用RTL8139D 作为以太网控制芯片,提供10/100M 以太网接口。

3、系统通过PCI BUS 采用uPD720102 作为USB 控制器芯片,提供三个USB2.0 接口。其中一路USB接口通过AU6331 读卡机控制器芯片,提供一个SD/MMC 接口。

3. 系统软件

本系统运行在LINUX DEBIAN4.0 操作系统下,其内核为LINUX 2.6.21。将Bootloarder–PMON2000 烧制在板载的BIOS ROM 中,加电后自动完成处理器、缓存、内存控制器、网络控制器等初始化工作。同时PMON2000 拥有少量行命令集,用于启动后对内存的读写校验、板载Flash 的擦写、IP设置、串口设置以及跟主机之间进行数据通信,包括上传、下传文件、接收主机下达指令等等。通过PMON2000的内部命令将LINUX 2.6.21 内核装入内存。

在内存条上有一个ROM,里面保存着内存大小、行地址数、列地址数、内存的bank 数等信息,这些信息可以通过I2C 总线来访问到。作为一种通用设计方案,要求能支持各种不同类型的内存条。而在系统的调试过程中,我们发现SM502 芯片的I2C 逻辑有bug 。因此采用SM502 的gpio 来模拟I2C 时序,实现对内存(DIMM)条信息的读取。并利用读取到的信息对龙芯2F 处理器的DDR2 控制器进行配置,收到良好的效果。经测试,目前该系统支持市场上的所有类型的内存条。

4.信号完整性设计

由于整个系统模块电路体积较小,而电路的工作频率较高,因此整个设计对信号的完整性有严格的要求。龙芯2F 处理器的DDR2 内存总路线工作频率高达300MHz ,这部分电路是高速电路设计的一个瓶颈,对这部分电路仿真的结果基本上可以反映出整个电路信号传输的效果。下面以DDR2 控制信号为例,描述该问题采取的设计方法和流程。

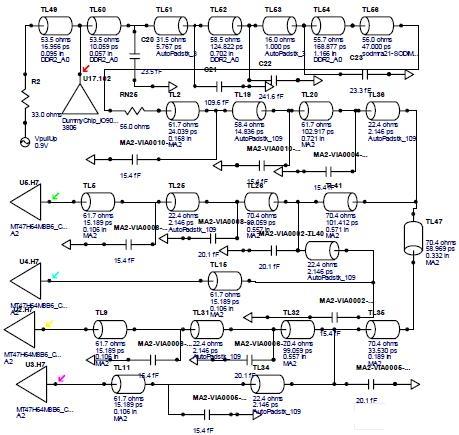

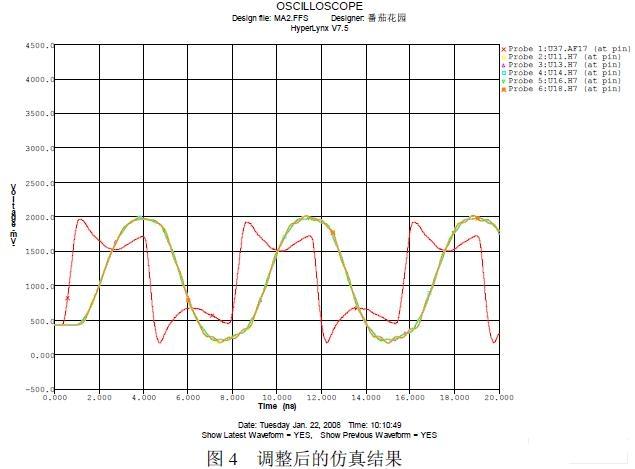

在实际设计中,首先利用龙芯2F 的IBIS 模型和仿真工具[4]预先确定关键信号的走线拓扑结构和匹配方式,由此来制定PCB 布线的约束。先提取PCB 布线前的仿真模型,通过观察对应的仿真结果波形,可确定获得较好信号质量的走线拓扑结构和匹配电路参数。完成PCB 布线后,再提取实际拓扑进行仿真,提取后的拓扑见图3 所示。此时模型已包括PCB 板的叠层和阻抗控制信息,并对实际过孔进行了建模。通过调整走线并观察仿真结果可获得最终最佳的走线。图4 给出了调整后的仿真结果,可以观察到在receiver 端获得了较好的信号质量,同时driver 端的过冲现象也在可接受的范围内。最后在实际板极调试中再测量实际信号波形,通过调整匹配元件进行微调来确保实际信号质量的可靠性。实践表明,基于这种方法和流程能减少信号完整性带来的设计风险,降低调试难度。本文稿中所有仿真IC modeling 参数为typical,driver 的激励信号为133MHz 周期信号。

5.小结

本文介绍了基于龙芯2F 处理器的车载和便携设备系统设计过程,主要对系统硬件结构、软件系统、信号的完整性设计、提高整机效率等关键技术进行了阐述。该系统结构紧凑,既能独立工作又提供了灵活的扩展接口,具有很大的应用前景。

此内容为AET网站原创,未经授权禁止转载。