0 引 言

随着计算机与微电子技术的发展,电子设计自动化EDA领域已成为电子技术发展的主体,数字系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。推动该潮流发展的引擎,就是日趋进步和完善的CPLD(Complex Programmable Logic Device)设计技术。而电子设计自动化,是近几年迅速发展起来的将计算机软件、硬件、微电子技术交叉运用的现代电子设计学科,其中EDA设计语言中的 VHDL语言是一种快速的电路设计工具,功能涵盖了电路描述、电路合成、电路仿真等三大电路设计工作。该数字电压表的电路设计,正是用VHDL语言完成的。此次设计主要应用美国Altera公司自行设计的一种CAE软件工具,即Max+PlusⅡ软件。

1 数字电压表的构成及工作原理

数字电压表是诸多数字化仪表的核心与基础。以数字电压表为核心扩展成的各种数字化仪表,几乎覆盖了电子电工测量、工业测量、自动化系统等各个领域。

1.1 数字电压表

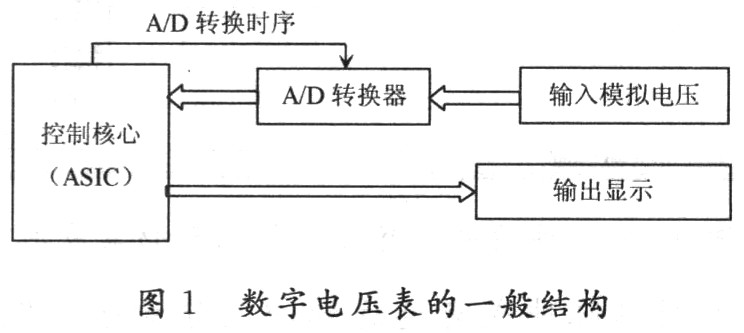

数字电子系统通常由ASIC芯片和外围硬件设备组成,具有灵活性不强等缺陷。如图1所示的数字电压表,A/D转换器在控制ASIC所提供的时序信号作用下,对输入模拟信号进行转换,控制核心再对转换结果进行运算和处理,最后驱动输出装置显示数字电压信号。由于系统功能由ASID硬件结构决定,其功能难以更新和扩展。如果用EDA方法设计,即以可编程逻辑器件CPLD代替ASIC芯片,用硬件描述语言决定系统功能,就可在硬件不变的情况下修改程序以更新和扩展功能,使其灵活性显著提高。基于此考虑,用EDA方法设计了一个简易数字电压表控制电路,旨在研究提高数字电子系统灵活性的设计方法。

1.2 数字电压表的工作原理

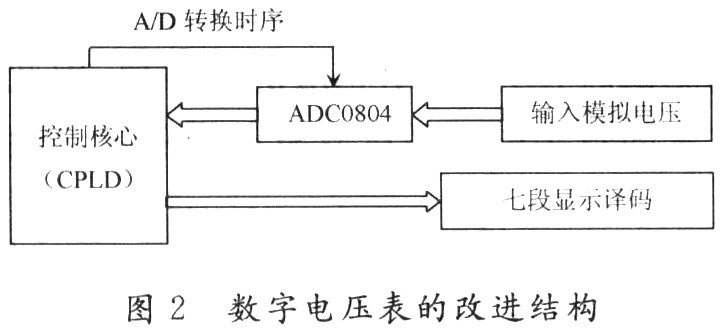

数字电压表的改进结构如图2所示,它的硬件包括三个部分,其中转换器ADC0804的作用是将模拟电压信号转换成数字电压值,并送到CPLD以待运算和处理;七段数码显示器的作用是接收CPLD转换后的BCD数据并显示;CPLD兼有处理和协调作用,包括控制A/D转换动作、接收A/D转换结果及编码、驱动显示等作用。因此,CPLD可分为三个功能模块,即控制模块、计算模块和显示驱动模块。

2 CPLD设计

由以上分析,数字电压表的CPLD设计,适合于顶层电路与三个底层模块相结合的设计方法,其中显示驱动模块有标准的七段显示VHDL子程序可供调用。下面仅论述其余两模块的设计。

2.1 控制模块的设计

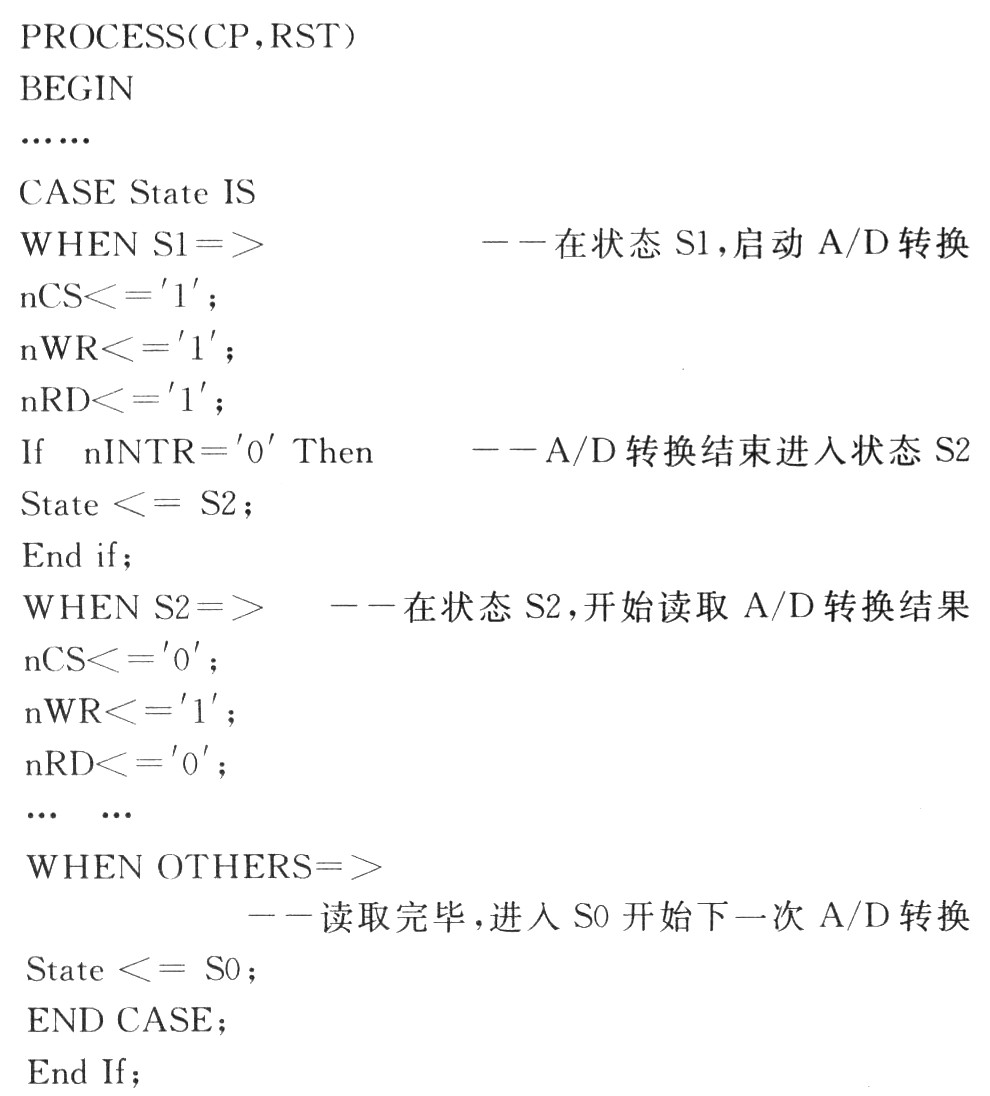

该模块的任务是,控制ADC0804的工作时序,可分为S0~S3四个连续的步骤或状态。任务分别是:使ADC0804准备转换(状态S0)、转换(状态 S1)、CPLD准备读取转换结果(状态S2)、读取转换结果(状态S3)。各状态由CPLD输出脚CS、WR、RD的不同电平组合确定,主要的VHDL 语句为:

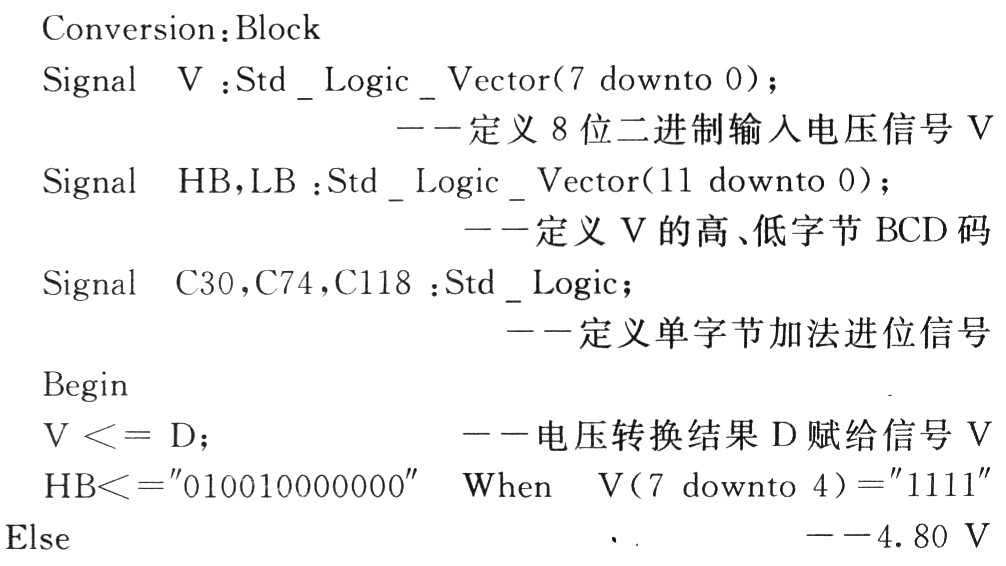

2.2 计算模块

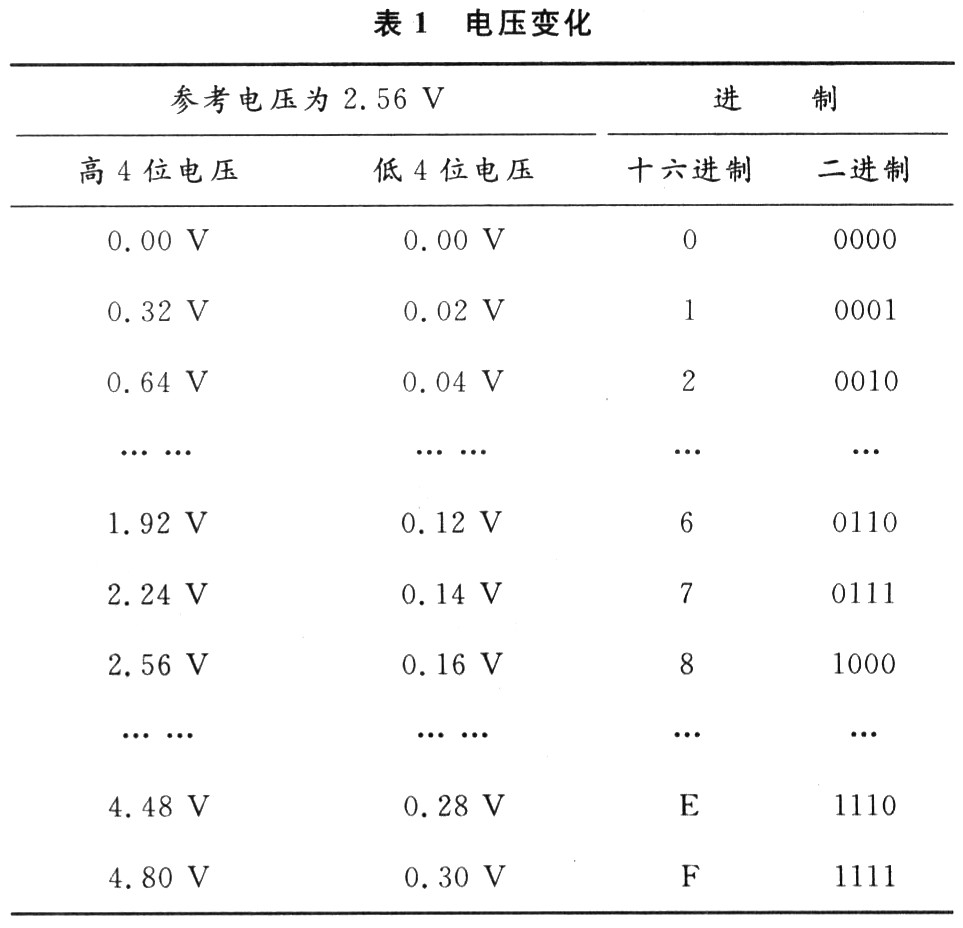

该模块将A/D转换结果分为高低4位,查表依次得到其BCD码后再进行计算,计算结果与A/D转换器的位宽和参考电压Vref均有关。本文选用8位转换器 ADC0804,参考电压为5.12 V,故能输出从0~5.12 V按照0.02 V步进变化的256(28)个离散值。如表1所示。

电压离散值可用8位二进制(或2位十六进制数)表示,表1中列出了输出数字电压高4位及低4位可能出现的16个值。如果CPLD从ADC20804接收到信号01101000B(即68H),对照表1高4位0110B是1.92 V,而低4位1000B是0.16 V,则最后的电压输出结果是1.92+0.16=2.08 V。

本文要求精确到两位小数0.01 V,故将输出电压表示成12位的BCD码形式。如上述的1.92 V是(000110010010)BCD,0.16 V是(000000010110)BCD,相加结果2.08 V是(001000001000)BCD。同理,若CPLD转换数据01110000B(即70H),则计算结果2.24 V是(001000100100)BCD。因此计算模块的设计主要包括一个12位的加法器及与之对应的存储器。

主要VHDL语句如下:

3 仿真结果

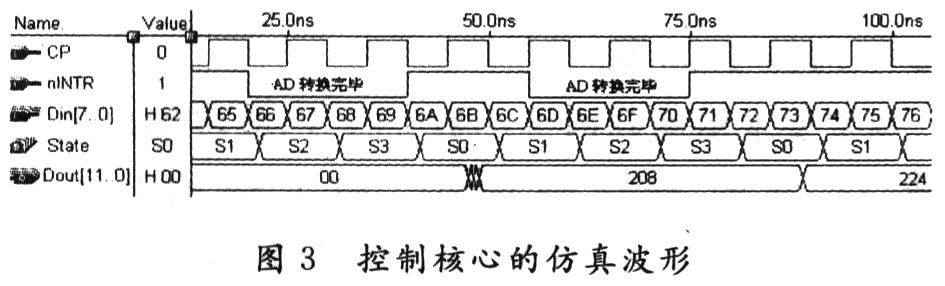

CPLD设计完成后,用Max+Plus II软件编译和仿真,波形如图3所示。由图3可知,CPLD工作时,先启动控制模块,它对模数转换的一次控制由四个状态组成。在状态S0,选定 ADC0804,为模数转换做准备;在状态S1,使ADC0804进行转换,当CPLD的INTR信号端由高电平转为低电平时,模数转换结束进入下一状态 S2,为读取转换结果做准备;在状态S3,CPLD读取模数转换结果。接着,CPLD的计算模块工作,求出二进制模数转换数据的12位BCD码。最后启动显示驱动模块,用数码管显示有两位小数的数字电压值。例如,模数转换结果即CPLD的输入信号Din[7..0]若为68H,则输出电压 Dout[11..0]是2.08 V,Din[7..0]为70H时,输出电压Dout[11..0]是2.24 V,符合设计要求。

4 结 语

本文数字电压表的功能由VHDL程序决定,用Max+Plus II软件编译、仿真和逻辑综合后,下载到CPLD芯片EPF10K10LC84-4。CPLD工作主频为100 MHz,逻辑综合占用了174个逻辑单元,资源利用率为30%。本文所设计的数字电压表电路板已通过硬件测试,能测量和显示0~5 V的弱电压信号,准确度为0.02 V,并已在我校EDA工程实训中心测试成功。保持CPLD芯片不变,将输入信号改为温度信号、湿度等信号分别测试时,均能显示相应的数字值,因此,基于这种设计方法的数字电子系统具有很强的灵活性。