模拟电路设计常常用到电压基准和电流基准。这些基准受电源、温度或者工艺参数的影响很小,为电路提供一个相对稳定的参考电压或者电流,从而保证整个模拟电路稳定工作。目前已经出现的高性能带隙基准,能够实现高精度、低温漂和低功耗,但这些电路中一般都有运放,调试难度较大;电路结构复杂,原理不便理解。在一般的应用中,如果对带隙基准电压的要求不是特别高的情况下,完全可以采用一种更为简洁的电路结构。因此,这里介绍一种简易可行的带隙基准电压的设计,利用PTAT电压和双极性晶体管发射结电压的不同的温度特性,获取一个与温度无关的基准电压。

1 低温漂低功耗带隙基准电压设计

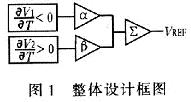

带隙基准电压的设计目标,就是建立一个与电源和温度无关的直流电压VREF。进一步将该目标分为2个设计问题:设计与电源无关的偏置,获取能抵消温度影响的电压值。图1为其整体设计框图。

1.1 与电源无关的偏置

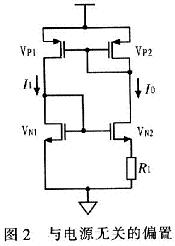

首先设计与电源无关的偏置。考虑采用2个NMOS管和电阻做近似的电流镜做偏置,并充分利用电流镜的“电流复制”特点,设计一个简单的电流产生电路,如图2所示。在这个电路中,因为栅漏短接的MOS管都是由一个电流源驱动,所以I0和I1几乎与电源电压无关。同时,2条支路的电流关系是确定的,只要已知I0,便可由宽长比得到左边支路电流的大小。忽略沟道长度调制效应的影响,支路电流的比值和MOS管宽长比的比值成正比。为了唯一确定电流,加入电阻R1。则有:VGS1=VGS2+I0R1,忽略体效应,有:

![]()

由式(1)可见,输出电流与电源电压无关,但仍与工艺和温度有关。

1.2 与温度无关的基准

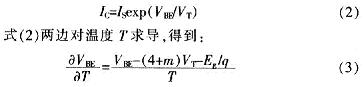

带隙基准的核心,就是将有着正负相反温度系数的电压以适当的系数加权,得到零温度系数的电压量。本设计中用到的负温度系数电压,是PN结的正向电压,也就是BJT的发射结正偏电压。双极型晶体管的集电极电流和基极发射极电压的关系:

式中,Is是双极型晶体管的饱和电流,Eg是硅的禁带宽度。当VBE≈0.75 v,T=300 K时,![]() 。注意,该温度系数本身与温度有关,可能会引起误差。

。注意,该温度系数本身与温度有关,可能会引起误差。

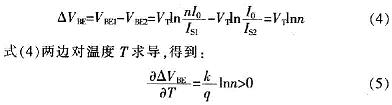

相同的双极型晶体管在不等的电流密度下工作,它们的基极发射极电压差值与绝对温度成正比,利用这个关系,建立一个带正温度系数电压。假设BJT的饱和电流,Is1=Is2=Is,集电极电流分别为nI0和I0,那么:

根据以上分析,完全可以利用这2种带有相反温度系数的电压设计一个零温度系数的电压基准。假设![]() ,已知

,已知![]() ,取α=1,则只需βlnn≈17.2,即可满足

,取α=1,则只需βlnn≈17.2,即可满足![]() ,实现了零温度系数基准电压VREF。

,实现了零温度系数基准电压VREF。

1.3 参数确定

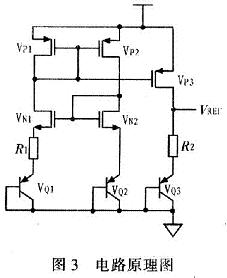

电路整体设计如图3所示。

其输出电压的表达式:

![]()

式中,n是VQ1的BJT并联数,m是流经R2和R1的电流比值,等于Vp3和Vp1的宽长比。

在调试电路时应该注意,Vp1、Vp2、VN1、VN2和电阻组成提供偏置的电流源,因此Vp1和Vp2、VN1和VN2应该尽量匹配,对称设计,且管子尺寸稍大。同时,使VN1和VN2的源极电压值尽可能相等。

在原理设计中,多次进行理性化估计,实际测试中存在的误差在所难免。为了达到最优效果,必须在测试中不断修正电路参数,然后再做测试。同时也应意识到,任何一个电路的各个指标都是相互影响相互制约的,应根据需要调整,以保证整体设计效果。

2 仿真结果

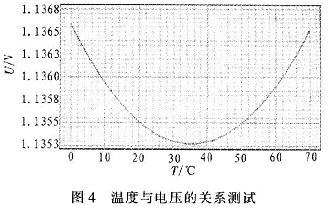

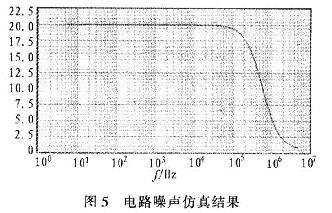

采用0.35μm BiCMOS工艺模型对电路进行仿真,输出电压随温度变化曲线如图4所示。当电压提供5 V供电,温度从O~70℃变化时,电压始终在1.135 32~1.136 56 V范围内变化,测得温漂系数为16.4 ppm/℃。当电源电压从5~6 V变化时,输出电压变化量为1.3 mV,电源抑制比达57.7 dB。噪声分析如图5所示,用软件对曲线进行积分,可得到电路总的输出噪声为140.3μV。同时,电路总电流控制在60μA左右,功耗为300.6 μW。

3 结束语

介绍了一种结构简易,原理清晰的带隙基准电压源的设计过程。采用不受电源影响的串联电流镜做偏置,利用PTAT电压和基极发射极电压的相反温度系数特性构造输出电压。0~70~C范围内,温漂系数为16.4 ppm/℃。供电从5~6 V变化时,电源抑制比达57.7 dB。总输出噪声为140.3μV,功耗为300.6μW。参数达到预定目标,能基本满足要求。该带隙基准电压电路简单,主要部分只用5个MOS管、3个BJT和2只电阻,避开了通用的带运放设计,大大简化调试难度,而且设计思路简洁明了,便于入门级人员短时间内掌握。