入门:FPGA设计硬件语言Verilog中的参数化

2022-12-31

来源:FPGA开源工作室

1 参数化

FPGA 设计的硬件语言Verilog中的参数化有两种关键词:define 和 paramerter,参数化的主要目的是代码易维护、易移植和可读性好。

Parameter关键词类似于C语言中的形参可在其他模块调用时实例化参数,这个参数在运行过程中不能修改,在编译时就已经确定好了。

示例:

模块引用如下:

方式一:

方式二:

第一种方式必须按照顺序,而第二种方式可以顺序颠倒。所以在参数化比较多的情况下,尽量采用第二种方式,以避免顺序的错乱。

Define关键词类似于C语言中的define 。主要用于本地模块的一些定义,例如状态机。

示例:

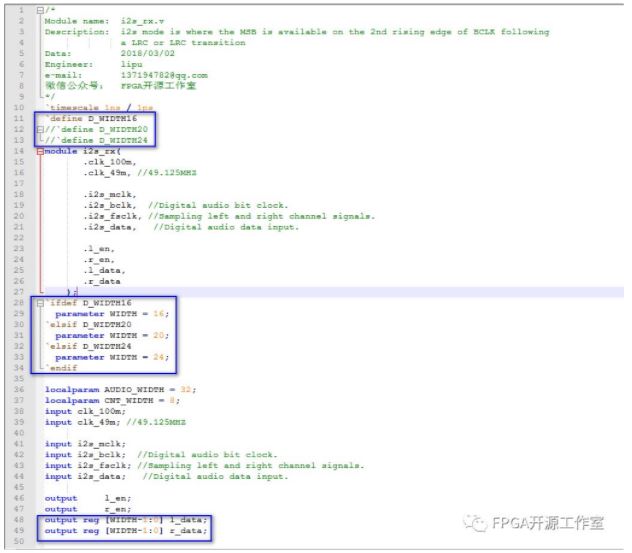

2 条件编译

一般情况下,Verilog HDL源程序中所有的行都将参加编译。但是有时希望对其中的一部分内容只有在满足条件才进行编译,也就是对一部分内容指定编译的条件,这就是“条件编译”。

有时,希望当满足条件时对一组语句进行编译,而当条件不满足是则编译另一部分。

条件编译命令有以下几种形式:1) `ifdef 宏名 (标识符)程序段1`else程序段2`endif

2) `ifdef 宏名 (标识符)程序段1`endif

示例:

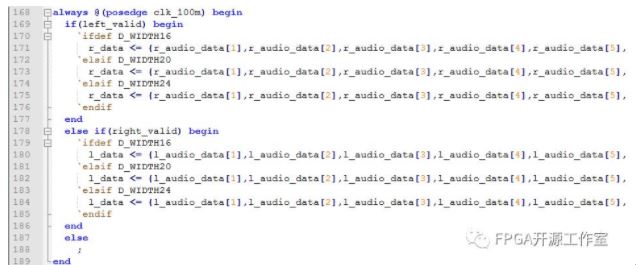

如上所示我们在写I2S的时候会遇到不同位宽的I2s数据,这就意味着对于不同的数据模块我们就要写一个文件。

如果采用条件编译就可以只写一个文件。当需要修改时只需要修改`define D_WIDTH16

//`define D_WIDTH20

//`define D_WIDTH24

就可以完成不同i2s数据位宽的修改。

更多信息可以来这里获取==>>电子技术应用-AET<<

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。