FPGA教学——ADC内部原理

2022-11-01

来源:电子技术应用专栏作家 FPGA开源工作室

01

前言

用了这么久ADC,从没细看过ADC的内部原理和如何获得最佳精度,今天看到一篇ST的官方文档讲的不错,这里整理分享给大家。

02

SAR ADC内部结构

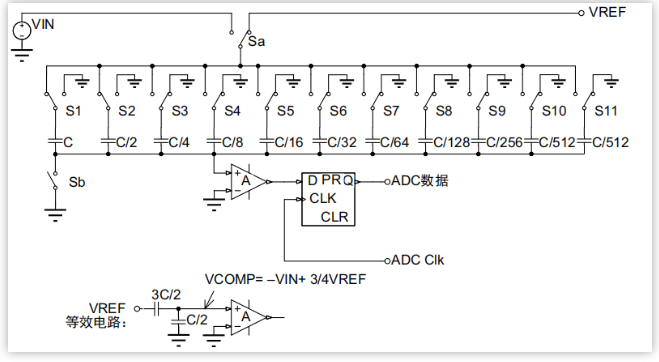

STM32微控制器中内置的ADC使用SAR(逐次逼近)原则,分多步执行转换。转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。

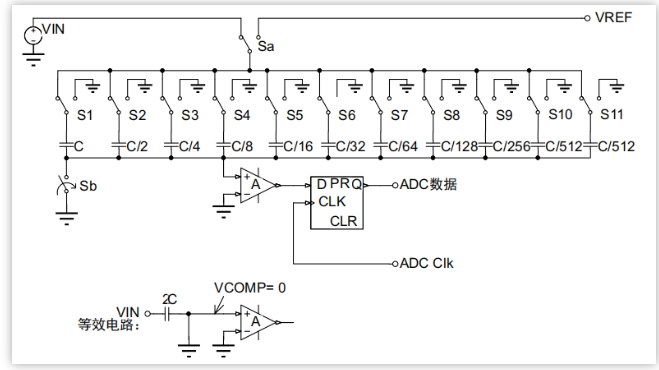

下面的图介绍了ADC的工作原理。下面的示例仅显示了逼近的前面几步,但 是该过程会持续到LSB为止

SAR切换电容ADC的基本原理(10位ADC示例)

带数字输出的ADC基本原理图

采样状态

采样状态:电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合

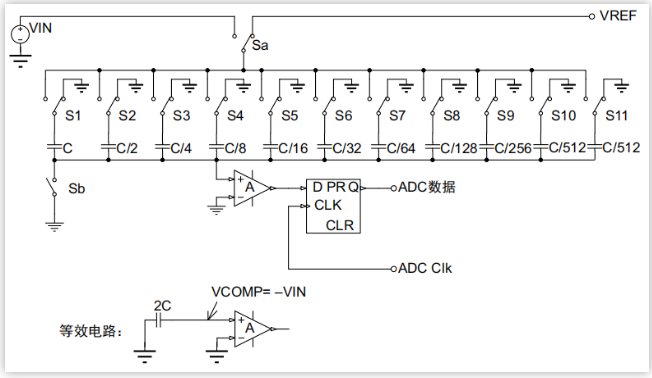

保持状态

保持状态:输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地且Sa切换至VREF。

逐次逼近

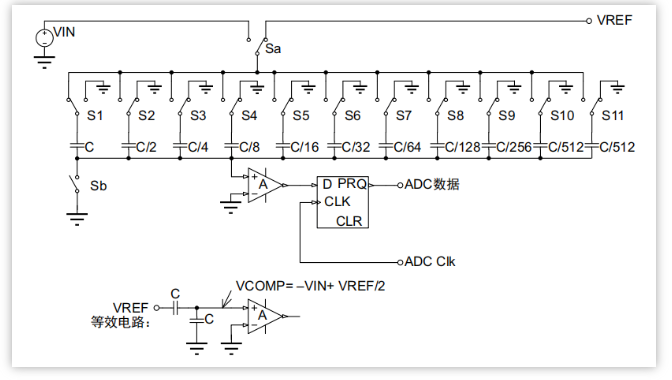

1、第一个逼近步骤。S1切换至VREF。VIN与VREF/2比较

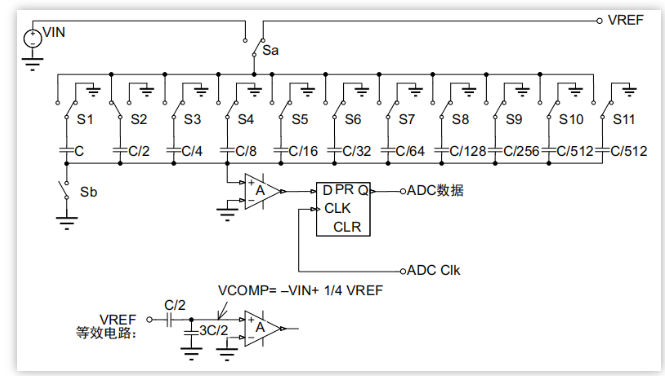

2、如果MSB = 0,则与?VREF进行比较,S1切换回接地。S2切换至VREF。

3、如果MSB = 1,则与?VREF进行比较,S1保持接地。S2切换至VREF。

重复如上步骤,直到LSB为止。可以简单理解为二分法逐次进行输入电压与参考电压的比较。首次于VREF/2比较,下次比较根据上次比较结果决定,如果MSB=1则与?VREF比较。如果MSB=0则与?VREF比较。后面决定与1/8VREF 3/8VREF、 5/8VREF、 7/8VREF之一做比较。循环直到输出LSB为止。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306116;邮箱:aet@chinaaet.com。