不会用示波器的Verilog码农不是一个好码农(LVDS与SpaceWire接口)

2022-10-21

来源:FPGA之家

在FPGA调试过程中,除了逻辑代码本身的质量之外,FPGA板子上PCB走线、接插件质量等因素的影响也非常重要。在刚上板调试不顺利的时候,不妨拿示波器看一下信号的质量,比如时钟信号的质量、差分信号的质量、高速串行信号的质量等等,这是上板调试之前首先要做的一步。没有高质量的FPGA外围管脚信号的输入,再好的代码风格和规范都无济于事。所以,调试FPGA之前一定要上示波器看一下关键信号的质量。

LVDS信号线间串扰问题

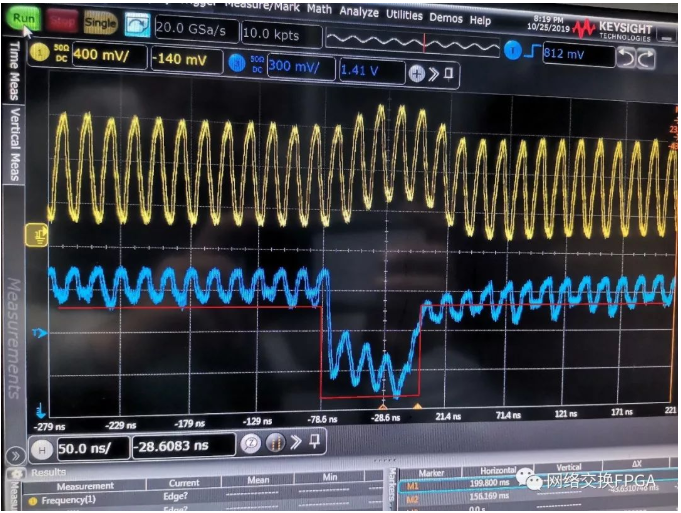

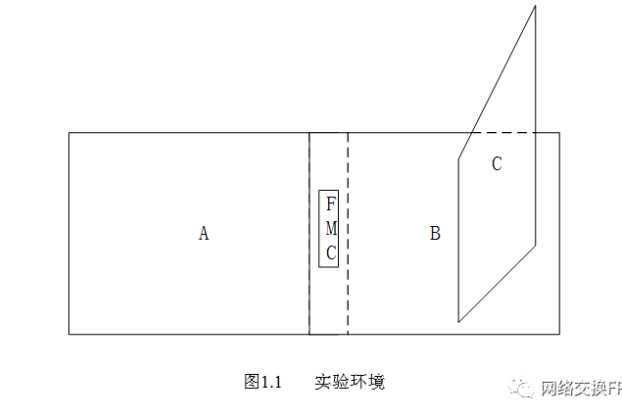

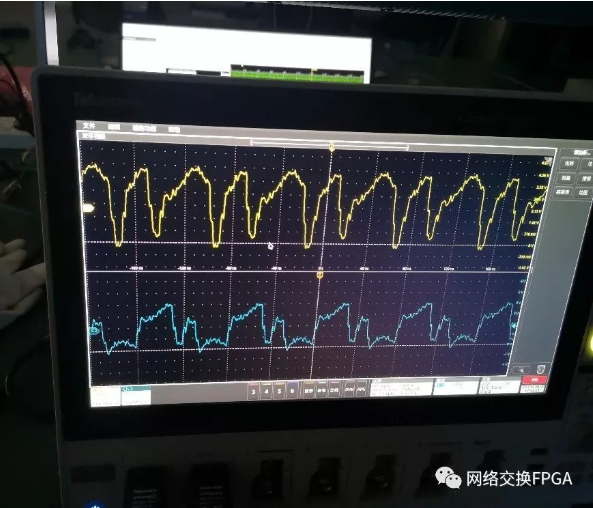

近日,在300Mbps的LVDS接口的调试过程中,出现了部分接口无法正确接收数据的现象,动用了一系列手段都无法使其老实下来踏踏实实接收数据,实可谓顽固不化。而在实验室老师的建议和要求下,经过一番折腾之后,我们终于见到了经过LVDS驱动芯片解差分后输入到FPGA的单端信号的真容。它是这样的:

(上图只抓了一位数据信号和一位时钟信号,其实是通过两位数据信号并行传输实现300Mbps的)

蓝色的波形是时钟吧,反正在上面数据信号不变化的时候还是时钟,频率也对,150MHz的……但是后面怎么就放飞自我了,这跟我们说好的不一样呀……

在此之前,有必要介绍一下我们这边调试所用硬件的情况,项目要接好多个LVDS接口,多到一个板子根本放不下,但是接口最终都是要连到一块FPGA上的,显然一块FPGA只能放在一块板子上,那这么多接口怎么办呢,不怕,反正还有别的板子,索性就把剩余接口都放在别的板子上吧。那接口需要的LVDS32和31的收发芯片怎么办,也没法都放在FPGA所在的那块板上,那就也都散开吧,LVDS接口收到的信号直接在接口旁边的LVDS32驱动芯片上解差分,单端信号通过各个板子间的接插件传到FPGA板上;发送则相反。所使用的接插件大概就类似于下面这种:

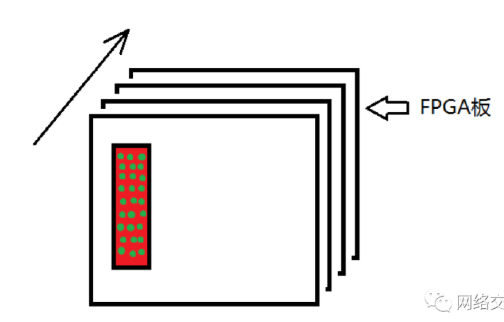

当然接插件上相邻信号线间的间隔没有这么大就是了,而且是三排一起。一共用了四块板子(别的板子还有CPU啥的实现其他功能)相互叠在一起,如下图:

绿点就表示接插件上的信号线,板间的这个接插件顺着箭头方向一直穿透到最后的FPGA板上,实现接口LVDS芯片和FPGA之间单端信号的传输。

硬件情况就是这样了,我们在测试中发现无法正确接收数据的接口全部集中在距离FPGA板最远的两块板子上,当把时钟降频之后,例如降频到60MHz时,所有的接口都可以正确接收数据,这基本排除了FPGA代码逻辑的问题。

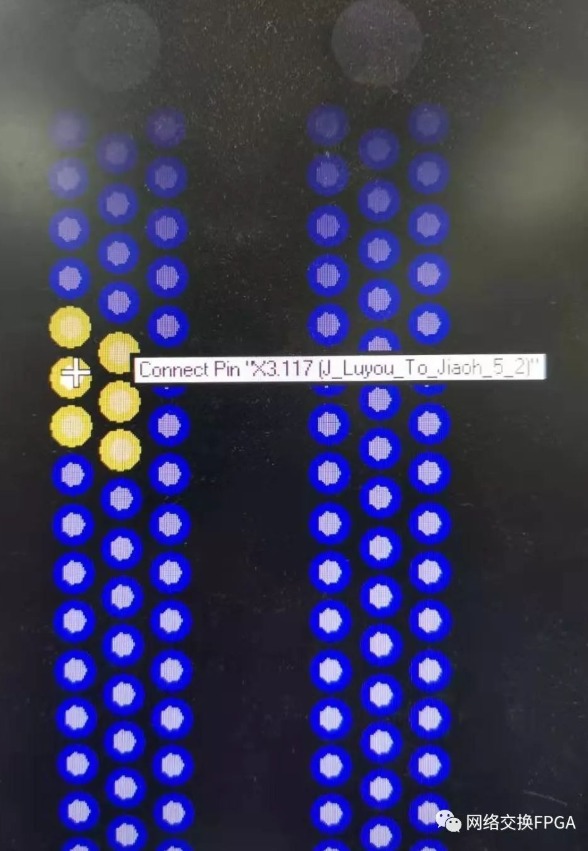

然后在与实验室老师交流了情况之后,了解到可能是硬件这边线间串扰的问题,然后想办法找了从最远的板子某个接口传到FPGA板上单端信号的接插件管脚图,并使用示波器帮助我们对传输的数据和时钟信号进行了检测:

上面就是板子接插件的管脚图,上面点亮的每一列的三个信号就对应着LVDS芯片恢复出来的一位单端时钟和两位单端数据信号,可以看到它们是相邻的,并且相距很近,可知硬件设计上并没有考虑线间串扰的问题。

然后我们就使用示波器对上述管脚的信号进行了检测,就看到了开头的那个画面……

自从上了研主要工作变成了写代码之后,感觉自己已经很久没有接触过硬件这块的东西了。这次的情况花费了我们不少的时间与精力,同时我们也明白了搞FPGA开发终归还是要对硬件有些许了解的,于是接下来我们就找了找资料,了解了一下什么是线间串扰。

线间串扰是电磁干扰的一种主要形式,当多条较长并且距离很近的导线平行传输信号时,其中每一条导线上的信号变化都会对其他导线的信号传输产生电磁干扰。

串扰的强弱受相邻电路分布电容、互感和电路本身的阻抗影响。线间串扰对受干扰电路的影响来源于电路间的分布式电容和分布式电感引起的电磁耦合:由于每一条线路都对地存在寄生电容和电感,使得线路之间存在不同程度的耦合,当其中一条线上存在电流或者电压变化时,相邻线路上就会产生电磁感应或静电感应,这就是线间串扰。线间串扰有电容耦合和电感耦合两种形式。

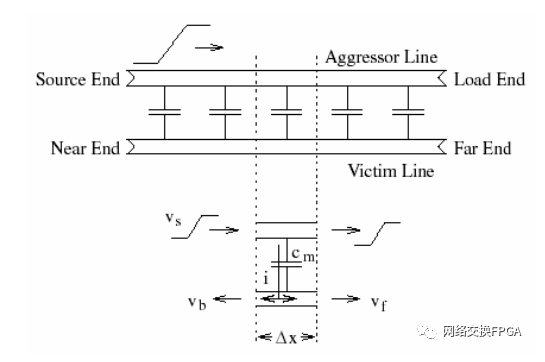

顾名思义,电容耦合是由于电子器件或线路之间存在的分布式电容,而产生电磁干扰的一种现象。导电传输线相互靠近时会存在一定大小的容抗,使得两边可以形成一个导电通路,一条传输线上的电压变化会通过两边传输线之间的互容将能量耦合到另一边,使其电位受到影响,具体影响效果如图:

当干扰传输线上升沿信号Vs通过时,会在受干扰线上产生一个前向的耦合电压Vf和后向的耦合电压Vb,其中前向电压产生的脉冲传向受干扰线的远端,后向电压产生的脉冲传向受干扰线的近端。

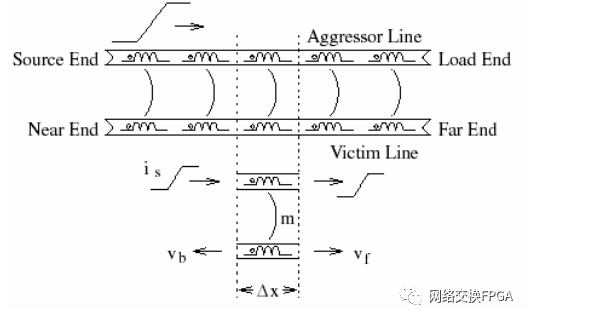

电感耦合则是由于电磁感应,一条传输线上的电流变化产生的磁场在另一条被干扰的传输线上引起感应电压导致的电磁干扰。相对于电容耦合而言,电感耦合产生的前向电压和后向电压极性是相反的,效果如图:

干扰信号在上升沿时间通过电感耦合在受干扰线上产生一个正的后向电压和一个负的前向电压。

其中电容耦合和电感耦合产生干扰的宽度和幅度变化是相似的,其脉冲宽度近似等于信号上升沿宽度,幅度与电压(电流)变化斜率成正比。

电容耦合和电感耦合一般都是同时发生的,而对于非理想地平面或微带传输线,电感耦合的影响要大于电容耦合。

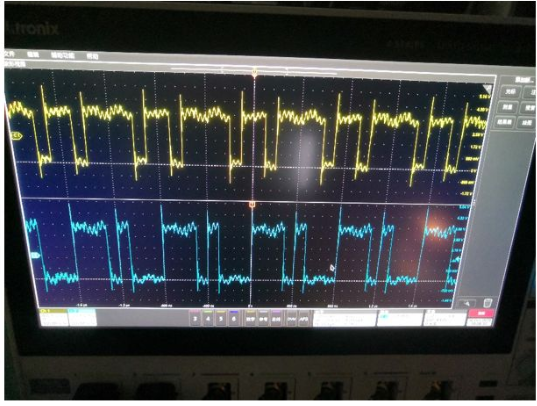

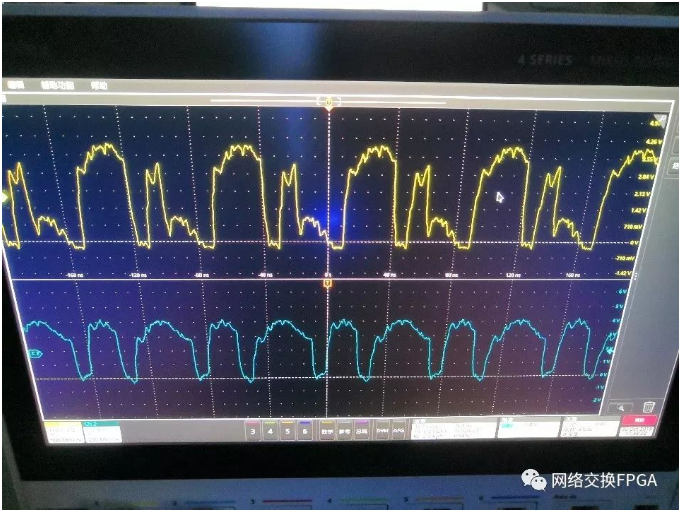

在了解了这些之后,再结合我们这边的情况来看,从示波器的波形中我们可以看到时钟和数据信号相互的干扰情况(为使观察更清晰,这里以60M时钟下波形为例)

上图中下方蓝色信号为数据信号波形,实际理想波形应如画出的红线所示,为一个整齐的方波,但是由于紧邻时钟信号线,受到时钟信号串扰后数据波形上一直存在着幅度较小的与时钟同频的信号波动;而当数据信号变化自身产生较大起伏时,时钟信号也受到影响出现了电压的偏移。

根据时钟和数据各自受到的影响来看,当对方电压信号上升时,自身电压信号便会下降,可知在该板间接插件中进行信号传输时,主要是电感耦合在串扰中起作用。

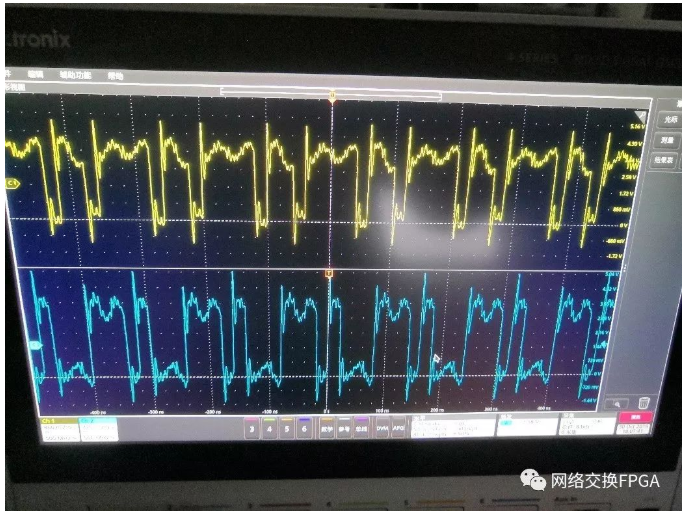

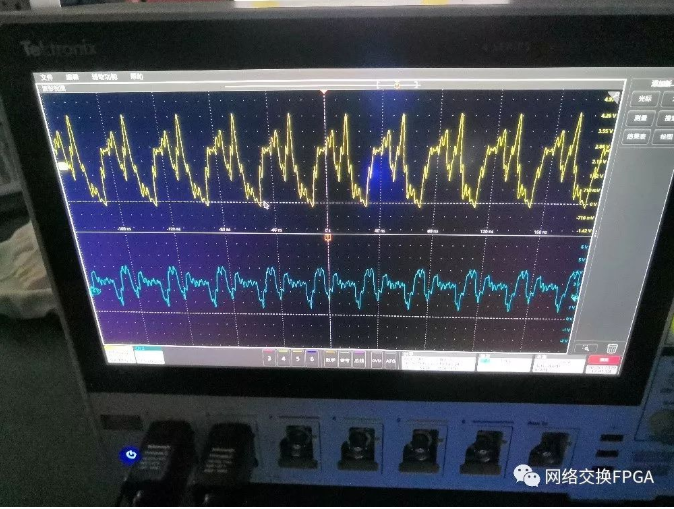

如果说上图中时钟频率为60MHz时还能正常对数据信号进行采样,但时钟频率增加到150MHz以上就无法正确采样了。如下图为时钟频率为150MHz时数据与时钟的波形,已经全部乱掉了。

经过查找资料,可以用一些措施来减少线间串扰:

1. 布置电子装置内部信号线时,尽量将其靠近接地底板,增大对地电容,从而减小串扰。

2. 在允许的空间范围内,应尽量加大信号线与其他线之间的距离,减少线间耦合(3W原则:传输线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰)。

3. 尽量缩短平行线长度,增加线间距离,如果可以,在信号线间加布隔离地线。

4. 机箱内板间的信号线越短越好。

5. 端子线进入印制板,可以在入口处增加RC去耦合电路,以便消除长线的传输串扰。

参考资料

https://wenku.baidu.com/view/401a805d312b3169a451a4ca.html

https://wenku.baidu.com/view/44c1d0cd27fff705cc1755270722192e453658ae.html?rec_flag=default

SpaceWire接口信号质量问题

SpaceWire总线协议支持2~200M之间速率传输,但是笔者在测试中目前无法实现200M进行跨板传输,因此通过示波器观察在200M下D、S信号的质量,从而进一步确定到底是代码质量存在问题,还是当前板卡的硬件质量问题。

1、实验环境

本文采用的实验环境如图1.1所示,该环境共有三块板卡构成。其中A、B板卡共同构成地检,实现将普通的以太网接口转换为专用的SpaceWire接口,C板卡为另外一块SpaceWire板卡。三块板卡通过接插件互相连接。

2、实验过程

由于SpaceWire在链路建立的过程中会自动发送NULL字符,因此只需将板卡上电下载代码即可进行观察传输信号的质量。为了更具有说服力,本次实验选用10M、50M、100M、200M四种传输速率进行对比,由于是同一套代码通过在线手动设置vio中寄存器的配置值实现不同的传输速率(使用VIVADO中VIO模拟CPU接口进行在线寄存器读写调试(附源代码)),因此实验结果具有可对比性。

2.1 10M传输速率

如图2.1所示,当采用10M传输速率时,D、S信号质量很好,传输中可以正常检测。

2.2 50M传输速率

如图2.2、2.3所示,当传输速率为50M时,信号的质量有下降的表现,但对于FPGA来说,该信号质量仍然很不错,能够正确的采样。

图2.2 A板给C板发送的DS信号

图2.3 C板给A板发送的DS信号

2.3 100M传输速率

将发送和接收速率设置为100M时,可得如图2.4和2.5所示结果。其中图2.4为A板给C板发送的DS信号,2.5为C板给A板发送的DS信号。可以看出,当前信号质量已经较差,但仍能正确识别与传输。

图2.4 A板给C板发送的DS信号

图2.5 C板给A板发送的DS信号

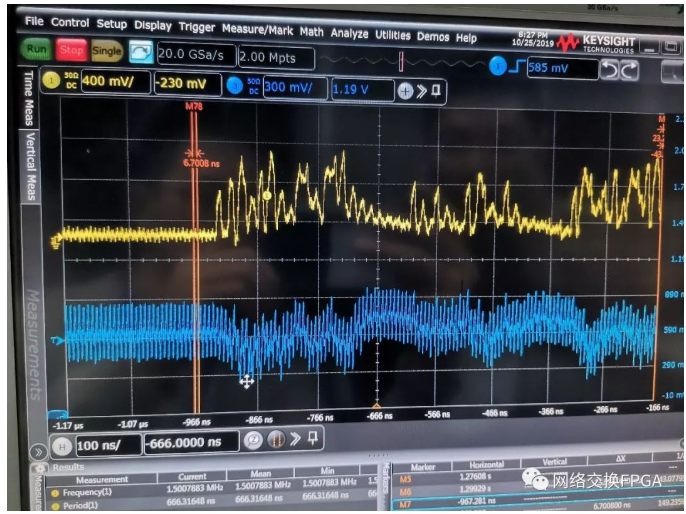

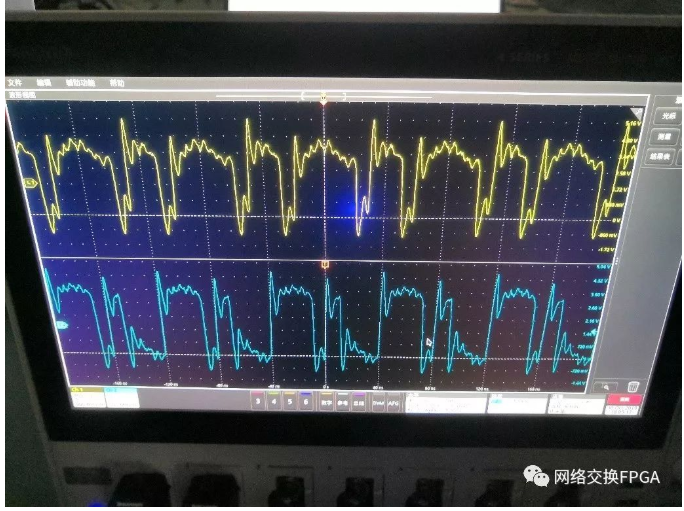

2.4 200M传输速率

在本文的实验环境下,C板内部自己产生数据源,速率为200M时,可以正确接收、解析,此时通过示波器观察到的D、S如图2.6所示,可以看出此时的信号质量已经很差了。

图2.6 C板自环200M下D、S信号采集结果

但是当通过A、B板和C板进行通信时,链路始终建立不成功,此时示波器观察不到对应的D、S信号。

3、 实验结果

通过上述对比可以发现,当传输速率为200M时,链路中信号质量很差,经分析显然不是前面例子中如串扰造成的,但应该是硬件的原因造成的。具体猜测有可能有以下几点原因造成:1、A板通过FMC接插件和B板相连,此处的走线会对信号质量产生较大的影响;2、FPGA程序中对于输入、输出管脚的时序约束仍有缺失;3、FPGA接收时钟采用的是D、S异或得到的时钟,这部分时钟的约束缺失。欢迎看到本文的大牛告知真正的原因。

更多信息可以来这里获取==>>电子技术应用-AET<<