FPGA教学——FPGA双向IO使用之三态门说明

2022-10-20

来源:FPGA之家

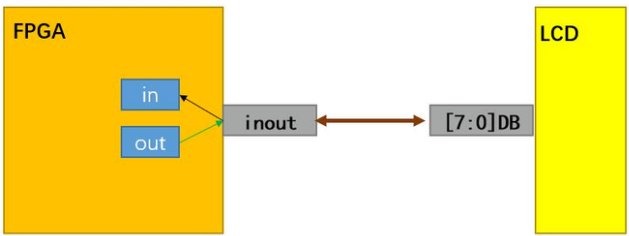

在FPGA设计中,双向IO(输入输出引脚)是一个比较麻烦的东西,但是信号线用作总线等双向数据传输时就要用到inout类型。

以下用液晶的的数据线用作双向IO示例:

说是双向IO端口,其实输入和输出不是同时进行的,需要有一个控制信号out_en来控制端口什么时候为输出,什么时候为输入。

那这里就需要引入一个三态门结构电路。

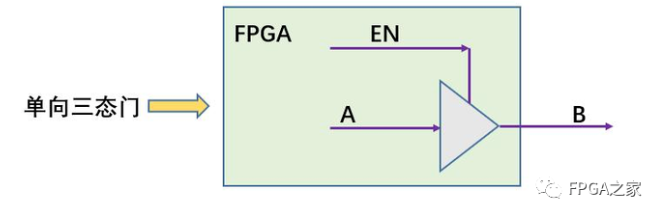

三态门结构

那么三态门的结构是怎样的呢?

三态门电路的输出结构和普通门电路的输出结构有很大的不同,因为它在电路中增加了一个输出控制端EN。

由上图看出,在单相三态门中,当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系,即A可以输出到B。当EN= 0时,电路内部的所有输出与外部将处于一种关断状态。

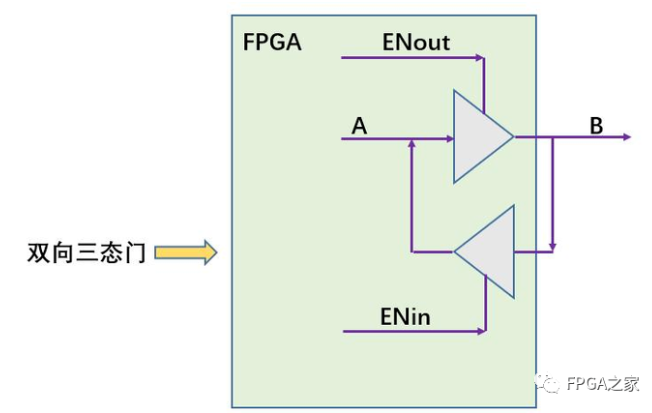

因此,当FPGA的信号线存在双向IO时,可以有两个三态门来控制,一个控制输出,一个控制输入,结构如下:

当ENout=1,ENin=0时,双向三态门的电路传输方向是A->B;

当ENout=0,ENin=1时,双向三态门的电路传输方向是B->A;

模型分析

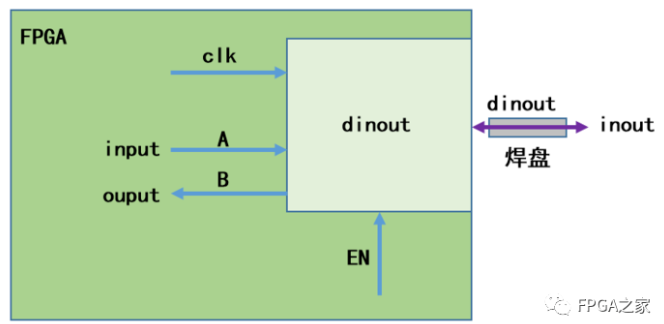

下面简单做个简易模型来说明双向IO如何分别实现作为输入端口和输出端口的功能,模块图如下:

模型引脚定义

(1)输入口A定义:当双向端口dinout作为输出口时,我们将A端口输入数据传到模块中,让数据从dinout口出来。

(2)输出端口B定义:当当双向端口dinout作为输入口时,我们将dinout端口输入数据传到模块中,让数据从B口出来。

(3)EN控制信号定义:当EN=1时,开通三态门,将dinout作为输出口使用,当EN=0时,把三态门置为高阻态,这时dinout作为输入口用。

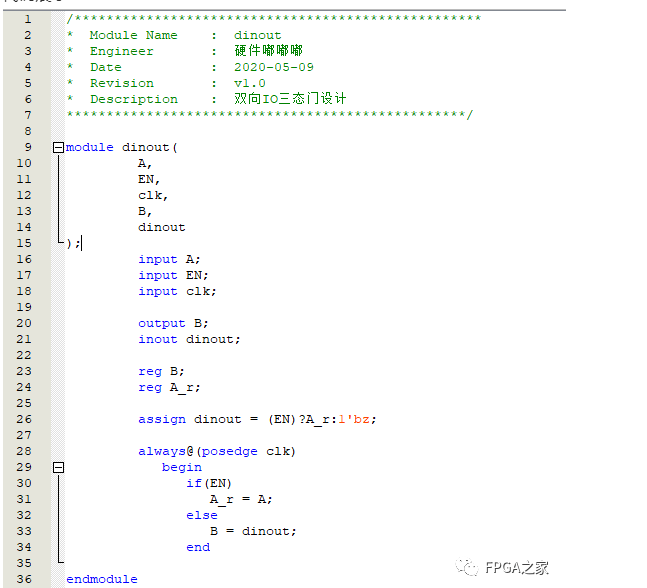

代码展示

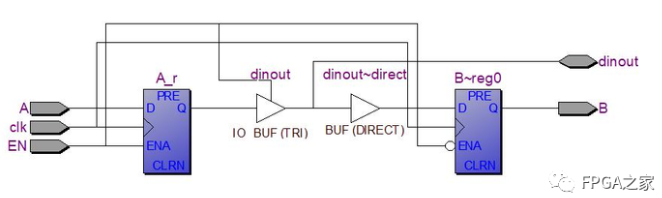

编译分析后查看RTL视角逻辑电路,符合原有模型设计。

总结说明

(1)FPGA内部不允许传递双向IO信号,只有FPGA对外部才能定义为双向IO端口,即只有在顶层输出的信号才可以被赋值为高阻态。

(2)在结构化建模的过程中,一个模块一个功能的建模,当涉及到内部模块的端口是双向IO端口时,然后根据一个双向IO对应一个输入,一个输出和一个使能控制,把模块中双向IO的输出用输出端口代替,双向IO的输入用输入端口代替,引出使能信号,并把对应assign中赋值的高阻态z根据实际情况给出0或1,来解决FPGA内部双向IO连接问题。

更多信息可以来这里获取==>>电子技术应用-AET<<