优化信号链的电源系统 — 第3部分:RF收发器

2021-12-07

作者:Pablo Perez, Jr.,高级应用工程师 | John Martin Dela Cruz,应用工程师

来源:ADI公司

简介

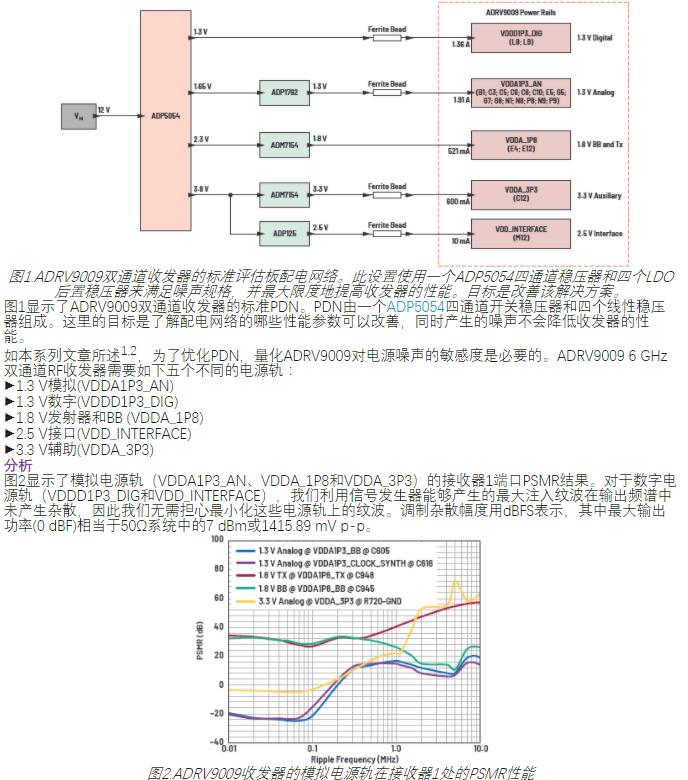

本信号链电源优化系列文章的第1部分讨论了如何量化电源噪声以确定其影响信号链器件的哪些参数。通过确定信号处理器件可以接受而不影响其所产生信号的完整性的实际噪声限值,可以创建优化的配电网络(PDN)。在第2部分中,该方法被应用于高速模数和数模转换器,证明将噪声降低到必要水平并不一定要提高成本、增加尺寸、降低效率。这些设计参数实际上可以在一个优化的电源解决方案中满足。

本文重点关注信号链的另一部分——RF收发器。本文将探讨器件对来自各电源轨的噪声的敏感度,确定哪些器件需要额外的噪声滤波。本文提供了一种优化的电源解决方案,并通过将其SFDR和相位噪声性能与当前PDN(当连接到RF收发器时)进行比较来进一步验证。

优化ADRV9009 6 GHz双通道RF收发器的电源系统

ADRV9009是一款高集成度射频(RF)、捷变收发器,提供双通道发射器和接收器、集成式频率合成器以及数字信号处理功能。这款IC具备多样化的高性能和低功耗组合,可满足3G、4G和5G宏蜂窝时分双工(TDD)基站应用要求。

对于VDDA1P3_AN电源轨,测量是在收发器板的两个不同分支上进行。请注意,在图2中,PSMR在<200kHz纹波频率时低于0 dB,表示这些频率下的纹波产生更高的相同幅度调制杂散。这意味着在200 kHz以下,接收器1对VDDA1P3_AN电源轨产生的最小纹波也非常敏感。

VDDA_1P8电源轨在收发器板上分为两个分支:VDDA1P8_TX和VDDA1P8_BB。VDDA1P8_TX电源轨在100 kHz时达到最小PSMR,约为27 dB,对应于100kHz纹波的63.25 mV p-p,产生2.77 mV p-p的调制杂散。VDDA1P8_BB在5 MHz纹波频率时测量约11 dB的最小值,相当于0.136 mV p-p的注入纹波产生的0.038 mV p-p杂散。

VDDA_3P3数据显示,在大约130 kHz及以下,PSMR低于0 dB,表示接收器1处的RF信号对来自VDDA_3P3的噪声非常敏感。该电源轨的PSMR随着频率提高而上升,在5 MHz达到72.5 dB。

总之,PSMR结果表明,在这些电源轨中,VDDA1P3_AN和VDDA_3P3电源轨噪声最令人担忧,贡献了ADRV9009收发器最大部分的耦合到接收器1的纹波量。

测试

图4显示了VDDA1P3_AN电源轨的杂散阈值,以及LTM8063 µModule®稳压器不同配置的实测噪声频谱。 如图4所示,在禁用展频(SSFM)的情况下,使用LTM8063为电源轨直接供电,在LTM8063的基波工作频率和谐波频率处产生超过阈值的纹波。具体说来,纹波在1.1 MHz时超过限值0.57 mV,表明需要后置稳压器和滤波器的某种组合来抑制开关稳压器的噪声。

如果仅增加LC滤波器(无LDO稳压器),则开关频率处的纹波刚刚达到最大允许的纹波——可能没有足够的设计裕量来确保收发器性能最佳。增加ADP1764 LDO后置稳压器并开启LTM8063的展频模式,可以降低整个频谱上的基波开关纹波幅度及其谐波,以及SSFM在1/f区域中引起的噪声峰值。 通过开启SSFM并增加LDO稳压器和LC滤波器,可以实现最佳效果,降低开关动作所引起的剩余噪声,给最大允许纹波留下约18 dB的裕量。

展频将噪声扩散到更宽频带上,从而降低开关频率及其谐波处的峰值和平均噪声。这是通过3 kHz三角波上下调制开关频率来做到的。这会在3 kHz处引入新的纹波,LDO稳压器会进行处理。

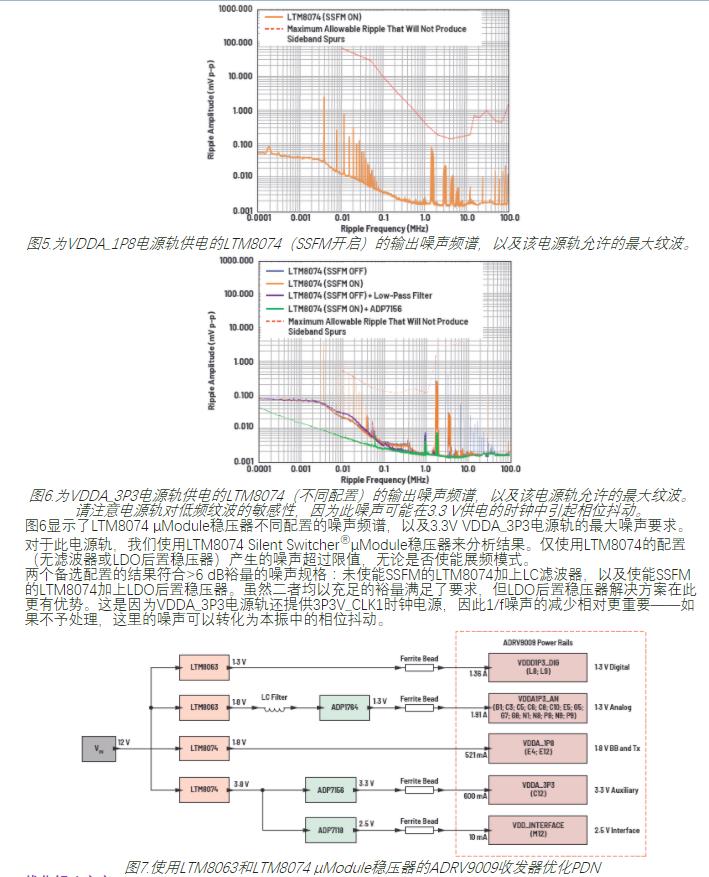

使能SSFM后,由此产生的低频纹波及其谐波在图5和图6所示的VDDA_1P8和VDDA_3P3输出频谱中显而易见。如图5所示,使能SSFM时LTM8074的噪声频谱为VDDA_1P8电源轨的最大允许纹波提供最小约8 dB的裕量。因此,满足此电源轨的噪声要求不需要后置稳压器滤波。

优化解决方案

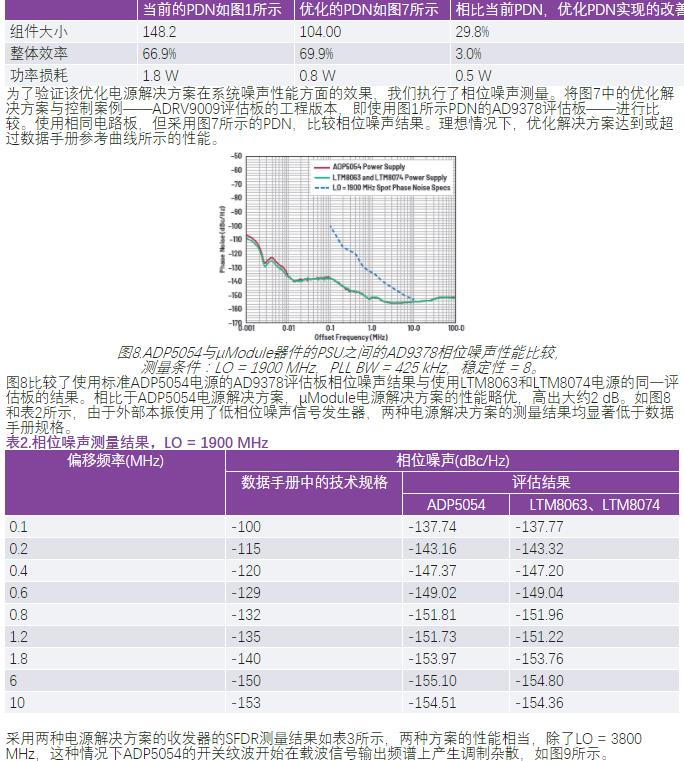

基于上述测试结果,图7显示了一种优化解决方案,当用在ADRV9009收发器板上时,它能提供>6 dB的噪声裕量。

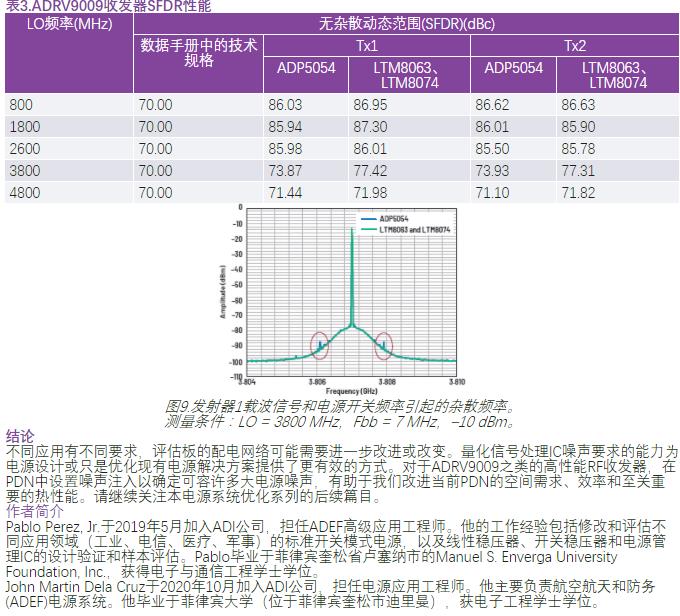

表1显示了优化PDN与标准PDN的对比。组件大小减小29.8%,效率从66.9%提高到69.9%,整体节能0.5 W。

表1.ADRV9009优化PDN与当前PDN的比较

ading_kwvj1giw" src="//www.ninimall.com/manager/static/ueditor/themes/default/images/spacer.gif" title="正在上传..."/>