文献标识码:A

DOI:10.16157/j.issn.0258-7998.2016.08.044

中文引用格式:牛少平,史嘉涛,索高华,等. 一种1394总线分析逻辑电路的设计与实现[J].电子技术应用,2016,42(8):175-178.

英文引用格式:Niu Shaoping,Shi Jiatao,Suo Gaohua,et al. Design and implementation of a 1394 bus analysis logic circuit[J].Application of Electronic Technique,2016,42(8):175-178.

0 引言

IEEE1394总线标准是一种具有高速、灵活和扩展性好的数据传输标准,是目前有效的数据传输方式之一,广泛应用于视频传输、工业控制中,也越来越多地应用在航空领域总线系统中。为确保新一代航空1394总线系统和设备功能的正确性、稳定性,需要一个完善的总线测试环境对系统进行充分测试。

本文结合航空1394系统应用研制中遇到的各种情况,从总线系统的相关需求入手,根据总线设备研制规范,提出了一种航空1394总线分析逻辑电路。该逻辑电路可内嵌于1394总线分析设备硬件中,能进行1394总线数据和状态的监控、分析与存储,支持发起多种总线行为和发送总线消息数据,可以为航空领域1394总线系统的研制和测试提供有效支持。

1 设计与实现

1.1 硬件结构

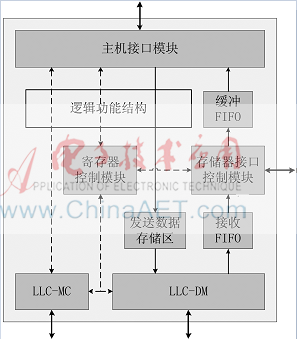

本文提出的1394总线分析逻辑电路内嵌于如图1所示1394总线分析设备中。其中,外围硬件主要通过专用芯片实现1394物理层、链路层功能、数据存储功能以及主机接口功能;逻辑电路作为整个设备的功能核心,主要实现总线信息的监控以及解析功能。

图1 1394总线分析设备结构

1.2 逻辑电路

作为1394总线分析设备的功能核心,分析逻辑电路主要由下面几个功能模块组成,其功能结构如图2所示。

图2 逻辑功能结构

(1)主机接口控制模块:实现了逻辑电路与硬件部分主机接口芯片之间的交互功能,包括响应主机发起的命令、解析命令信息,以及将读取数据进行封包发送等功能。

(2)存储接口控制模块:一方面实现对片外存储器进行数据读写的接口功能,将内部提供的数据写入片外存储器或从片外存储器读取数据;另一方面完成数据信息写入、读出操作的调度控制,其工作模式可通过寄存器控制模块中相应的功能寄存器进行配置更改。

(3)链路层接口控制模块[1]:LLC-DM模块实现通过链路层数据接口进行消息数据收发的功能;LLC-MC模块实现链路层控制寄存器的访问配置功能。主要完成链路层工作模式配置或获取链路层状态信息等。

(4)寄存器控制模块:实现用于逻辑功能控制的控制寄存器、用于标识总线状态的状态寄存器,以及收发消息的计数寄存器等。初始化、启动使能、发送帧周期等控制及参数信息均经由主机访问并操作相关控制寄存器位实现。

(5)其他模块:包括基于异步FIFO的接收缓冲模块、基于DPRAM的发送数据存储模块,以及不同时钟域模块之间的信号同步模块。

1.3 关键设计

1.3.1 存储结构及存取调度机制

在消息数据和状态信息的存储控制方面,采用了如下优化设计:

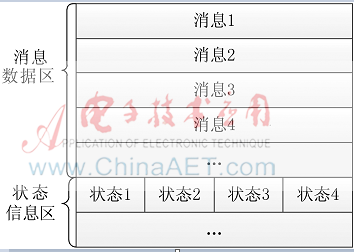

首先,存储结构。这里将数据信息与状分析信息进行分区存储,存储结构如图3所示。数据区域按每条消息数据占用2 KB空间划分,分析信息区域按每条消息占用8 B空间划分,数据消息与分析信息一一对应。采用这种数据存储结构,可让存取操作时的寻址更加规律准确,降低误操作的概率。

图3 消息数据存储结构

其次,存取调度机制。存储操作时先存数据信息,后存状态信息;读取操作时先读状态信息,后读数据信息。存储调度流程是因为状态信息是完整分析一条数据信息后才产生的。读取调度流程是便于软件从状态信息开始进行解析。

1.3.2 数据获取机制

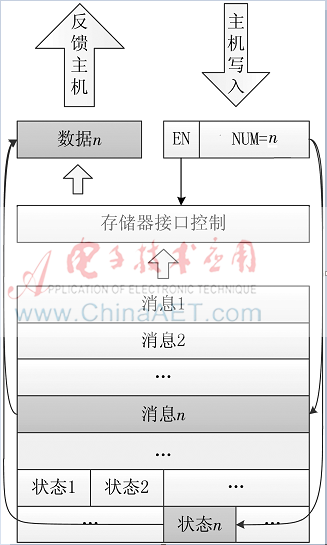

上层主机获取存储器中的数据信息时,一般采用直接寻址读取的方式,而采用这种方式在获取大量数据时往往需要发起多次多操作,很大程度上影响获取数据的效率。针对本文设计中的存储结构,这里采用一种新的数据获取机制,如图4所示。

图4 数据获取机制

主机以消息条目为输入,对逻辑内部消息读取控制寄存器发起一次写操作,读取控制寄存器根据指定条目信息直接调度读取该条信息完整数据并反馈输出给主机。采用这种机制,主机只需发起一次操作,便可读取一条消息的数据,这样一方面可提高数据获取效率,另一方面提高应用软件的同步解析效率。

1.3.3 链路模式自动配置

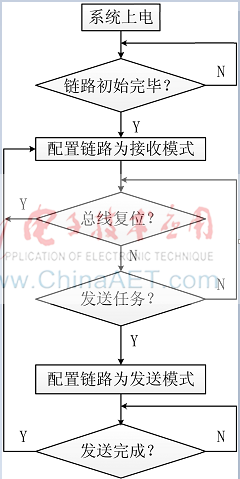

1394总线状态分析需要链路工作在正确的模式下,系统上电后,收发消息数据时,链路的工作模式就需要进行配置或调整,采用主机直接配置无疑会影响效率,甚至有可能影响正常的总线行为。

针对这种问题,本文在逻辑电路的LLC-MC模块中实现链路工作模式的自动配置机制。如图5所示,系统上电后,LLC-MC模块检测等待链路初始化完成后进行默认的接收模式配置。当主机启动发送任务时,根据链路状态适时配置链路切换到发送模式,等待发送完成后再迅速配置切换回接收模式。

图5 链路自动配置过程

2 仿真与测试

本文首先对1394总线分析逻辑电路功能进行了虚拟仿真验证。

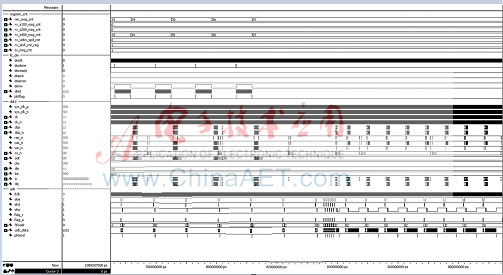

如图6所示,链路层数据接口llc_dm负责完成消息数据的接收,每接收一条消息,消息记录计数器rec_cnt_reg计数递增1,S400速率消息计数器计数递增1,标识着逻辑电路接收了一条速率为S400的消息数据;llc_dm接口接收完一条消息数据后,存储器接口DDR2将接收消息数据写入片外存储器暂存;最后由主机通过USB接口[2,3]进行数据请求,每请求一次,逻辑通过DDR2接口取出一条消息数据交给USB回传给主机。

图6 逻辑功能验证结果

其次,通过嵌入该逻辑电路的1394总线分析设备进行了实践测试。

如图7所示,总线分析设备在连接到1394总线系统时,总线复位行为引起了各总线节点设备的响应,分析设备监控到了多次的总线复位行为(Bus Reset)以及各节点发出的S100的物理层自标识消息(PhySelfD0)。

图7 1394总线分析设备实测结果

由于本文提出的1394总线分析逻辑电路主要针对航空1394总线系统的开发,因而与国内外现有通用1394总线设备相比,其具有更好的适用性、更高的效率以及较低的成本。

3 结论

通过试验表明,本文所述1394总线分析逻辑电路支持1394总线上不同速率、不同类型的消息数据收发,有效完成总线行为监控和数据分析,同时可内嵌用于多种1394总线仿真设备或用于总线异常分析的测试设备,具有良好的航空系统设备适用性,对于当今航空1394总线系统的研制与开发具有重要的应用价值。

参考文献

[1] 刘光远,张涛,郑伟波.基于FPGA的数据采集系统IEEE1394接口设计[J].仪表技术与传感器,2009(12):46-48.

[2] Cypress.EZ-USB FX2 Technical reference manual[EB/OL].(2001)[2016].http://www.cypress.com.

[3] 许永和.EZ-USB FX2系列单片机USB外围设备设计与应用[M].北京:北京航空航天大学出版社,2002.