文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.09.003

中文引用格式: 张德智,曾星星, 胡倩. 基于并行处理技术的宽带直扩信号捕获方法[J].电子技术应用,2016,42(9):10-13.

英文引用格式: Zhang Dezhi,Zeng Xingxing,Hu Qian. Wideband DS-Signal capture scheme based on parallel processing technology[J].Application of Electronic Technique,2016,42(9):10-13.

0 引言

扩频信号以其隐蔽性好、抗干扰性强的特点,在各类通信、导航、数据链传输体制中得到广泛应用[1]。常用扩频信号(如GPS)伪码速率不超过10.23 Mcps,伪码长度不超过1 023,扩频增益较低、信号带宽较窄,抗干扰和保密能力有限。随着飞行器通信频段由传统的L、S频段向更高的Ku、Ka频段迈进,用户信道资源日趋丰富,带宽达数百兆赫兹的宽带扩频体制逐步得到应用,宽带扩频信号频谱更隐蔽保密性更高,抗干扰能力更强,具有良好的应用前景。

同窄带扩频信号相比,宽带扩频信号带宽更宽,AD采样速率要求高达数百兆赫兹,超出大多数后端器件直接处理能力[2]。目前主流的扩频快捕算法均针对10 Mbps以下的窄带扩频信号,而对于宽带扩频信号尚未发现有效的捕获方法。为解决此问题,本文设计一种基于并行信号处理技术的快捕算法,在不降低前端采样率的情况下,使得后端处理器件在可承受的时钟频率下实现宽带扩频信号的快速捕获。

1 捕获算法顶层设计

1.1 指标需求

某项目宽带扩频信号为零中频形式,速率为153.45 Mcps,信息速率10 kbps,伪码周期15 345(内外码相乘的复合码形式,内码长15,码率153.45 M,外码长1 023码率10.23 M,相位相干对齐),信号体制为PCM-DS(直接序列扩频)-BPSK(载波相位调制),多普勒动态范围±90 kHz,最大变化率±2.4 kHz/s,载频为S频段。

1.2 硬件架构设计

考虑射频滤波器矩形系数,信号采样率至少应大于1.2 GHz,为降低对AD器件及后端处理器件压力,应选用正交采样形式,这样双通道AD采样速率600 MHz即可满足低通采样要求。后端信号处理FPGA(现场可编程逻辑门阵列)采用XC5VFX100T,根据器件特性无法直接工作于600 MHz处理采样数据,因此需采用并行信号处理技术,实现以面积换速度。

1.3 软件功能设计

解调算法整体结构如图1所示,功能上可划分为串并转换、并行下变频、并行伪码NCO、并行载波NCO、并行伪码生成器、捕获处理模块、跟踪处理模块等。

串并转换模块将AD输入的高速串行数据拼接、转换成8路并行的I、Q数据,供后续并行处理。AD器件自带1分2 DEMUX,将I、Q通道的数据速率降低至300 MHz(如图1所示,I0、I1、Q0、Q1速率为300 MHz),这样后端FPGA串并转换处理时钟仅需300 MHz。对I0、I1(同理Q0、Q1)分别再进行1分4的串并转换,并按照采样时间的先后顺序重新排列拼接,最终将600 MHz的10 bit采样数据,1分8串并转换成80 bit的拼接数据。这样后续信号处理工作时钟降为75 MHz,易于FPGA实现。

输入信号含有载波多普勒,I、Q数据经串并转换模块后变成8路并行数据,需要经并行下变频模块进行去多普勒处理。并行下变频模块由并行载波NCO驱动,中心频率受捕获模块和跟踪模块控制字控制。

针对并行处理后的I、Q数据,本地伪码生成器同样采用并行模式,由并行码NCO驱动。NCO的频率控制字由捕获模块和跟踪模块控制,实现本地伪码滑动。输入数据和本地伪码解扩后进捕获模块,完成载波和伪码捕获,调整伪码和载波NCO到近似对齐的相位和频率上。捕获完成后转入跟踪环节。

1.4 捕获参数设计

速率为153.45 Mcps,信息速率10 kbps,伪码周期15 345,因此积分清零时间选定为0.1 ms。根据码多普勒和载波多普勒比例关系,fdchip为伪码多普勒,Rc为伪码速率,fc为载波频率,fdop为载波多普勒。

当载波多普勒达到±90 kHz时,伪码多普勒可达fdchip=6.818 kHz,积分清零时间为0.1 ms,则积分清零周期内伪码会漂移0.68个码片,因此一次滑动半个码片是不可行的,需要在频域上分段搜索以降低码多普勒影响。

因此本设计采用频率分段+内码滑动相关+外码匹配滤波的捕获方式,滑动相关找到内码相位,对内码进行积分累加后,再对外码进行匹配滤波,滤波器长度只需要1 023,资源占用较少。

2 核心模块设计

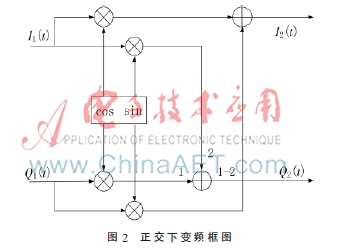

2.1 正交下变频设计

本方案中AD采样信号是下变频后的零中频基带信号,AD输入含有I、Q两个支路,因此本地产生的数字下变频需要采取特殊设计。将输入I、Q信号定义如下:

用复信号表示为:

由此可得正交下变频器的结构如图2所示。

2.2 基于并行载波NCO的下变频实现

本地NCO的采样率应与输入信号采样率一致为600 MHz,如此高采样速率的NCO无法直接在器件中实现,需要采样并行设计。根据DDS原理,本地载波信号频率可表示为式(9),fs为信号采样率,这里为600 MHz,fc为希望得到的频率,N为量化位数,K为频率控制字,可根据fs、fc、N求出。

fc=fs·K/2N(9)

如果系统时钟为600 MHz,则1个NCO可在8个时钟周期内得到8个载波相位,记为Ph1,…,Ph8,通过查表可得到相应载波幅度值,这样在1/75 MHz(8个600 MHz时钟周期)时间内得到8个连续的载波采样点。

当系统时钟为75 MHz时,若采用8个载波NCO同时工作,则在1/75 MHz时间内同样可得到8个相位值P1,…,P8,分别查表得到8个载波幅值,这样在1/75 MHz时间内同样得到8个载波采样点。通过调整各NCO的步进值,可使得P1,…,P8与Ph1,…,Ph8等效,从而实现与600 MHz的载波NCO等效。

NCO具体设计方式如下,设任一时刻8个NCO的相位累加器值为Pi,i=1,…,8,则Pi表达式如式(10)所示,其中P0为上一个时钟周期第8个累加器的相位值,K与式(9)一致,这样P1,…,P8与Ph1,…,Ph8等效。

Pi=P0+K·i,i=1,…,8(10)

在一个时钟周期内8个累加器可以得到P1,…,P8共8个相位值,通过查找8块同样的查找表,可以得到等效在600 MHz采样率下连续的8个载波值cos(n+1),…,cos(n+8),sin(n+1),…,sin(n+8)。

这样数字化后的并行下变频的结果I3(n+k)、Q3(n+k),k=1,…,8表达式如式(11)、式(12)所示:

I3(n+k)=I2(n+k)·cos(n+k)+Q2(n+k)·sin(n+k)(11)

Q3(n+k)=Q2(n+k)·sin(n+k)-I2(n+k)·cos(n+k)(12)

其中I2(n+k)=Q2(n+k)为串并转换后的采样数据,为降低后续处理资源消耗,将下变频后的输出截位至12 bit,则8路并行后的输出为96 bit。

2.3 并行本地伪码产生

扩频信号的捕获需要本地产生与发端一致的伪码序列,由本地码NCO推动码生成器产生,对于本设计伪码速率高达153.45 Mcps,采样率为600 MHz,同样只能采用并行的伪码生成方式。根据式(9),fs为信号采样率,这里为600 MHz,fc为码率153.45 Mcps,N为量化位数取N=36,则可求出频率控制字K。

与2.2节类似,伪码时钟由8个独立的码NCO模块产生。定义75 MHz主时钟下的并行码钟为pn_clk[clk1,clk2,…,clk8],clki,i=1,...,8代表在600 MHz采样频率下的连续8个伪码时钟,1个主时钟内共有8个采样点。clki可由式(13)得出,Pc0为上一个时钟周期第8个相位累加器的相位值,Pci(i=1,...,8)为8路码NCO模块的36位累加器相位值。

{clki,Pci}=Pc0+K·i(13)

本设并行计伪码的产生由ROM查表实现,将复合码的内码、外码的一个周期序列存储到ROM中,通过不同的查找地址得出相应伪码。由于伪码速率和主时钟非整数倍关系(2.046),可知在1个75 MHz时钟周期内(等效8个600 MHz时钟)最多同时存在3个内码码片(2个完整码片,1个不完整码片)。因此选用了3个深度为15,宽度为1 bit的ROM用于存储内码,ROM_B中的内码相位比ROM_A滞后1个码片,ROM_C中的内码相位比ROM_B滞后1个码片。

外码的产生于内码类似,在1个75 MHz主时钟内最多存在2个内码,因此需要两个深度为1 023宽度为1 bit的ROM用于存储外码。

并行伪码产生的仿真结果如图3所示, clk为75 MHz主时钟,pn_clk为8路并行码时钟,0、1交替的位置表示一个码片的起止位置。以pn_clk=[01111000]为例,在此主时钟周期内存在8个600 MHz时钟采样点,前一码片的最后一个采样点在bit7结束,bit6-bit3为当前码片的起止位置,bit2-bit0为下一个码片的前3个采样点位置。伪码输出记为pn_out[pn1,pn2,,...pn8],其中pni,i=1...8代表在该75 MHz时钟内,由600 MHz时钟对伪码进行采样,得到的8个采样数据。

2.4 捕获方案设计

根据前述分析,本方案采用频率分段+匹配滤波器的捕获方式,该方式操作简单,具有最快的捕获速度,但资源消耗较大,但对于XC5VFX100T系列平台影响较小。

扩频信号的快捕包括载波和伪码两个层面,载波捕获采用分段搜索的策略,在每个频段内搜索伪码相位,并对伪码进行辅助,降低载波多普勒的影响。考虑到跟踪模块锁频环的有效牵引范围为±1/4T,T为积分清零时间0.1 ms,因此对于本设计多普勒分段间隔不应超过5 kHz。本设计多普勒搜索范围要求±90 kHz,变化率2.4 kHz/s,分段间隔过窄会导致捕获时间变长,综合考虑后这里取分段间隔为2.4 kHz,共划分为81个分段,多普勒搜索范围可达±96 kHz,捕获完成后多普勒补偿精度可达±1.2 kHz。

由于输入伪码的复合码特性,可以将伪码捕获分为外码捕获、内码捕获两个过程,内码周期很短只有15,故可以采用滑动相关的方式,一次步进半个码片,滑动一个完整内码周期后进行积分清0,积分周期为一个外码码片的周期即0.1/1 023 ms。

这样积分清0后的伪码速率从153.45 Mcps降到10.23 Mcps,再进入1 023长的匹配滤波器,连续1 023个积分值进入后(即一个完整外码周期)可得到相关峰值。当内码滑动到对齐位置时,外码匹配滤波器的输出一定会出现最大相关峰。采用这种方式只需要设计1 023长的匹配滤波器,可以节省设计资源。为了提高捕获灵敏度,可以对匹配滤波结果作非相干累加,非相干累加10次后,信噪比可提高约7 dB。匹配滤波器的工作频率只需10.23 MHz,不再需要并行信号处理[4]。

由于码多普勒存在,当分段间隔为2.4 kHz时,经载波辅助后,当前频带内的最大码多普勒为:

fdchip=1.2k153.45/2 325=79.2 Hz(14)

复合码周期为0.1 ms,累加10次后用时1 ms,在此期间内码片偏移0.079 2个码片,若内码按照1/2码片滑动,则滑动一次后实际变化0.5-0.079 8=0.42个码片,则为了保证能遍历所有内码相位,内码滑动次数应至少为15/0.42=36次。

捕获流程为:捕获环节开始后,首先从多普勒分段1开始滑动内码相位,外码同时作匹配滤波,内码遍历结束后可得到36个相关峰值;多普勒分段切换至分段2,重复上述过程,当所有81频率分段均遍历完成后,可得2 916个相关峰,记最大相关峰为peak1,记录对应的外码序号和内码序号;由于遍历过程用时较长,在此期间多普勒会发生动态变化,因此还需在peak1所在频率分段的相邻3个段内重新搜索码相位,此过程的最大相关峰为peak2,当相关峰peak2与peak1可比拟,且对应外码、内码序号与peak1位置接近时,认为捕获完成。将peak2所在多普勒分段信息补偿载波NCO,实现频率捕获,根据内码和外码序号置伪码生成器,实现伪码粗对准,随后转入跟踪环节。

3 仿真结果及性能分析

3.1 仿真结果

由Simulink产生采样率为600 MHz,C/No=90 dB/Hz(等效信号电平-80 dBm),多普勒为50 kHz的复合码扩频信号作为仿真输入。当搜索到正确频道时内码滑动过程对应的外码匹配滤波仿真结果如图4所示。rms_out为外码匹配滤波结果,此时有非常明显的相关峰出现。当内码滑动相差超过一个码片时,外码匹配滤波的相关峰急剧降低,仿真结果如图5所示。

3.2 捕获时间计算

根据前述分析,遍历一个频率分段需要滑动36次,内码滑动期间外码非相干累加10次,所需时间为36×10×0.1=36 ms。第一次遍历搜索81个分段,用时81×36 ms=2.916 s,此期间最大多普勒变化达2.916 s*2.4 kHz/s=7.2 kHz跨越三个频率分段,需要对当前分段和前后相邻各3个分段进行再次搜索。

第二次遍历搜索7个频道,用时7×36 ms=0.252 s。

总捕获时间为2.916+0.252=3.168 s。

3.3 资源占用分析

本算法串并转换模块、下变频模块、伪码NCO模块、伪码产生模块、捕获模块的内码滑动、积分累加为并行处理环节,占用资源较多;捕获模块外码匹配滤波、捕获策略设计、跟踪环节是非并行设计模块。占用资源较少。经ISE综合,共占用FPGA片内63%的Slice资源、46%的块RAM资源、52%的乘法器资源。

4 结论

经过分析计算可知,本文提出的宽带扩频信号捕获算法,通过“以面积换速度”的形式,利用并行信号处理技术,有效降低了系统处理时钟要求,算法技术可行实现简单,共占用FPGA片内63%的Slice资源、46%的块RAM资源、52%的乘法器资源,资源占用率较低,利于工程实现。

参考文献

[1] 黄爱军.卫星通信抗干扰设计考虑及性能分析[J].电讯技术,2012,52(3):259-263.

[2] 童长海,郑雪峰,郑戈,等.600 Mb/s高速数传接收机的设计与实现[J].遥测遥控,2007,28(S1):34-38.

[3] 严家明,李瑾,胡楚锋.基于正交混频的数字下变频技术研究[J].计算机测量与控制.2009,17(1):200-202.

[4] 代敏,禹思敏,罗玉玲.匹配滤波器同步捕获技术FPGA设计[J].通信技术.2010,43(2):13-16.