摘 要: MAC(Media Access Control)层位于网络结构七层协议中的数据链路层,控制局域网中的多个节点对共享介质的访问,保证相邻节点之间数据的可靠传输。本文介绍一种吉比特MAC接口的结构,该MAC采用基于描述符传输的DMA(Direct Memory Access)和双通道的MTL(MAC Transaction Layer),在半双工模式下支持10/100 Mb/s、全双工模式下支持10/100/1 000 Mb/s的网络数据传输速率。

关键词: MAC;描述符;DMA;MTL

0 引言

在计算机网络技术飞速发展的新时期,人们对现有资源共享越来越依赖网络,并设计开发了多种不同应用范围的局域网技术。其中,以太网凭借其较高的灵活性和操作性,在局域网技术使用过程中得到了飞速迅猛的发展。随着人们对网络带宽和数据传输速率要求的提高,千兆位以太网应运而生。千兆位以太网仍然保留了以太网的帧格式、CSMA/CS机制和MTU[1],并且引入了载波扩展和帧突发机制[2]。以太网IEEE802.3协议根据LAN的特点,把数据链路层分为LLC(逻辑链路控制)和MAC(介质访问控制)两个子层。MAC层协议作为数据帧收发的基础,是以太网技术的核心,主要负责上层数据和物理层的数据流量控制以及数据流的检测、校验工作。

IP核是采用Verilog等硬件描述语言实现的功能块。使用IP核的方式便于实现元件系统引用、修改基本元件功能及IP核复用都非常容易。在SoC设计中,IP核的使用可以缩短设计周期,降低设计风险,已经成为SoC设计中不可缺少的部分[3]。

本文主要介绍吉比特MAC接口IP软核的结构和实现。

1 MAC功能

本设计中的MAC遵守CSMA/CD协议,网络数据在发送的过程中打包成标准的IEEE802.3帧格式;在接收数据过程中,对数据帧进行CRC校验,有效删除错误数据,提高数据传输效率[4]。支持半双工和全双工的操作模式,半双工模式下支持10 Mb/s/100 Mb/s的网络数据传输速率,提高载波扩展和帧突发机制,并以back-pressure的形式进行流控制;全双工模式下支持10 Mb/s/100 Mb/s/1 000 Mb/s的网络数据传输速率,并采用pause帧的方式进行流控制;支持可编程的帧间距以及帧长度以适应标准以太网帧和长达16 kB的超大以太网帧;支持IPv4、IPv6和ICMP网络协议和TCP、UDP传输协议;提供GMII/RGMII/MII/RMII端口与相应的PHY端口连接,并且提供MDIO主机对PHY进行配置管理。

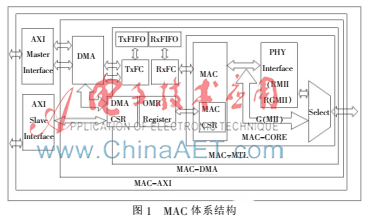

2 MAC体系结构

如图1所示,MAC由以下四个部分构成:MAC-AXI、MAC-DMA、MAC-MTL、MAC-CORE。MAC采用独立的数据传输与寄存器访问接口,通过AXI接口与DSP连接,通过AXI主机端口进行数据的传输,通过AXI从机端口访问DMA和MAC的系统控制、状态寄存器(CSR)[5]。AXI接口基于burst的传输方式和独立的控制、数据及响应通道,提高了传输效率和总线的利用率;DMA提供独立的数据和寄存器访问接口,数据端采用基于描述符的传输将数据传输到MTL,大大提高了数据传输效率;MTL提供两个FIFO对DMA与MAC-CORE之间传输的数据进行缓存;MAC-CORE对网络数据帧进行接收发送并对PHY进行配置管理;各个层次都提供了单独的发送、接收通道,加快数据传输速率。此外,该MAC IP核的各个层次可独立,用户可以根据自己的需求选择合适的结构。

2.1 AXI接口

MAC通过AMBA3 AXI总线接口与DSP连接。AXI主机接口支持burst请求以队列的形式发出读写请求,并通过请求重排序,数据交错使得主机可以更加灵活地选择优先请求、慢速外设从机。在写数据通道设计了一个深度为8的数据请求FIFO,这样AXI总线上最多能支持8个读写请求。此外还设计了深度为2的数据FIFO和响应FIFO,用以支持DMA的OSF操作模式,提高数据传输效率。AXI从机接口访问MAC的系统控制、状态寄存器(CSR)。

该接口提供128 bit的数据位宽、32 bit的地址位宽,最大burst长度为32,每个ID最多支持4个读/写请求,为数据的高效传输提供了保障。该接口允许来自不同DMA通道的读写同时传输,以提高总线的利用率。另外,为了减少整个芯片的功耗,DSP可以通过控制AXI接口使MAC进入低功耗模式。

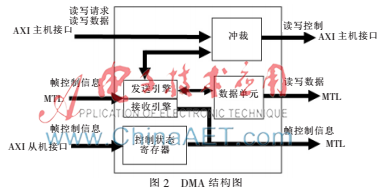

2.2 MAC-DMA

DMA模块实现MTL模块和AXI接口之间的数据交换,DSP通过AXI从机接口配置DMA寄存器直接启动MAC,DSP可以通过设置DMA CSR来控制DMA的操作。该模块采用128 bit的数据位宽与AXI接口和MTL模块连接。如图2所示,DMA提供独立的CSR访问接口和数据接口;具有独立的发送、接收引擎,发送引擎将数据从DSP的发送数据buffer传输到MTL,接收引擎将数据从MTL传输到DSP接收数据buffer,描述符作为这些buffer的指针;冲裁模块除了对读写操作进行冲裁和发送接收之间的冲裁之外,还包括对描述符传输与数据传输的冲裁。读写数据通过数据单元缓冲,提高传输效率。

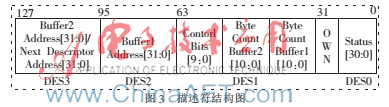

DMA通过描述符的传输在DSP尽量少干涉的情况下实现数据交互,每个描述符可以传输8 KB的数据,描述符地址宽度与总线宽度一致。描述符有两类:发送描述符(TDES0-3)和接收描述符(RDES0-3),如图3所示,每一类描述符包含两个buffer、两个字节计数buffer和两个指向DSP发送、接收数据buffer的地址指针。每一个描述符最多指向两个数据buffer,数据buffer可以包含一整帧的数据或者不满一帧的数据,但是不能超过一帧,并且只含数据,buffer状态包含在描述符中。一帧的数据可以跨越多个数据buffer,但是一个描述符中的数据不能跨越多帧。描述符列表有两种结构:环型,每个描述符指向两个数据buffer,执行到最后一个描述符时跳回描述符列表的首地址;链接型,将DES3配置成下一个描述符地址形成描述符链,这种模式下的描述符只能指向一个数据buffer。

与以往基于计数的DMA传输相比,采用基于描述符传输的DMA每次传输的数据量增大,传输速率更快。此外,DMA具有单独的发送、接收引擎可加快数据的传输,并提供帧分隔符以优化报文结构的传输,对任何正确或错误的传输都给出状态标识位,增强数据传输可靠性,支持可编程地发送、接收DMA引擎burst尺寸以提高总线利用率,支持每一帧的发送接收完成中断控制和各种操作情况下可编程的中断选择。

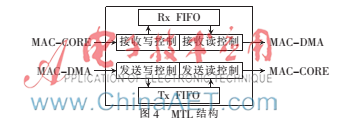

2.3 MAC-MTL

MTL作为DMA的从设备,采用128 bit数据位宽与DMA和MAC-CORE相连,数据传输以简单的FIFO协议执行操作。该模块包含两个数据通道,发送通道和接收通道。发送通道将DMA的数据传输到MAC-CORE,DMA控制发送通道的所有传输;接收通道则把MAC-CORE的数据传输到DMA,如图4所示。每个通道都含有单独的读写控制模块。根据接收帧的状态信息,接收写控制模块对接收帧进行过滤,删除错误帧。在发送过程中产生冲突时,发送读模块将冲突的数据帧重新发送到MAC-CORE端。

MTL提供了两个8 KB的双端口异步FIFO缓存DMA与MAC-CORE之间传输的数据帧。Tx FIFO缓存DMA从DSP内存读取且尚未被发送到MAC的数据,Rx FIFO保存从以太网接收且尚未被传输到DMA的数据。除了缓存每一帧的数据外,每一帧的状态信息紧跟数据存入FIFO中,而不需要额外的FIFO来保存,因此只要FIFO未满就能不断接收数据帧,提高传输效率。数据FIFO通过选择信号启动,即FIFO不工作时处于休眠状态,减小功耗。MTL将FIFO的空满状态信息反馈给DMA,再由DMA控制发送接收操作。此外,Rx FIFO满的情况下,可以通过pause帧控制或产生back-pressure给MAC-CORE来控制数据帧的接收,进行流控制。Tx FIFO的flush操作则是通过软件来控制的。

2.4 MAC-CORE

MAC-CORE有发送、接收两个通道,实现PHY与MTL模块的数据交互,具有单独的地址过滤单元,对接收数据帧的地址进行检查以便决定接收帧的传输与否。支持多种地址过滤方式:目的地址/源地址过滤、单播地址/多播地址过滤,另外还可以提供哈希表对地址进行过滤,具有单独的CRC模块,对每一个接收帧进行CRC校验,对需要发送的帧产生CRC检验码。支持可编程的IFG和接收帧的IEEE802.1Q VLAN检测。对IPv4、IPv6数据包负载进行TCP、UDP、ICMP检验以及IPv4首部检验和验证。提供四种PHY端口:MII、GMII、RMII、RGMII,并且输出端口的数据并行输出,提高数据传输效率。提供MDIO模块对PHY进行配置和管理。

3 MAC体系结构

在VCS验证平台下,分别在10 Mb/s/100 Mb/s/ 1 000 Mb/s传输速率下对MAC IP核的RTL级代码进行了模块级和系统级验证,主要验证其逻辑功能的正确性,逻辑验证和功能结果均符合要求。图5为半双工模式下100 Mb/s传输速率MAC模拟波形图,图6是全双工模式下1 000Mb/s传输速率MAC模拟波形图。模拟验证表明,该结构的MAC设计达到了预期目标。

4 结束语

本文针对千兆位以太网的要求,介绍了一种吉比特MAC接口,用Verilog硬件描述语言,实现了一个RTL级的IP核,该MAC采用AXI接口,连续发送burst请求,各个通道独立,提高总线利用率。基于描述符传输的DMA在没有CPU干涉的情况下,一次可以传输大量的数据,独立的双通道MTL为数据快速传输提供了保障。MAC-CORE提供了多种类型的PHY端口,数据并行输出,加快了传输速率。最后对该MAC进行了模拟和验证。验证结果表明,本文设计的模块功能正确,达到了预期目标。

参考文献

[1] IEEE P802.3ba(tm) D3.2-2010. Telecommunication and information exchange between system-local and metropolitan area networks specific requirements Part3: carrier sense multiple access with collision detection(CSMA/CD)access methodand physical layer specifications[S]. 2010.

[2] 蔡开裕,朱培栋,徐明.计算机网络[M].北京:机械工业出版社,2008.

[3] 韩建,陈岚,粟雅娟,等.基于用户的IP核评测方法[J].微电子学与计算机,2009,26(11):43-47.

[4] 张伟华,魏仲慧,何昕.嵌入式通用千兆以太网接口的设计与实现[J].仪表技术与传感器,2011(6):41-43,47.

[5] 吴俊杰,吴建辉.以太网MAC控制器的MII接口转RMII接口的实现[J].电子器件,2008(2):712-715.