摘 要: 采用DSP与FPGA相结合的方案,设计了一款雷达回波信号采集卡。此设备主要用于小型VTS系统、中小型船舶以及航海操纵模拟器中。DSP与FPGA相结合构成快速传输通道,为雷达回波采集处理提供有力保障。现场可编程门阵列(FPGA)灵活性强,内部逻辑功能可以根据需要在系统中配置,其作为DSP的辅助芯片为AD提供时钟,协同AD完成模拟信号的采集与传输,同时完成外部接口的逻辑转换,充分发挥它的灵活性优点。主控芯片DSP主要用于信息处理和整个硬件模块的控制。

关键词: FPGA;DSP;雷达回波;采集系统

0 引言

数据采集系统是一种应用非常广泛的模拟量测量系统,其基本任务是将模拟信号经采样量化编码后送入计算机或相应的信号处理系统中,然后根据不同的需要进行相应的计算处理。随着科技的发展,其应用领域涵盖雷达、电力、空间遥测、汽车制造、军事等行业。雷达性能的日益强大离不开数据采集系统的发展,特别是数据处理芯片和AD采样频率的快速发展。现在雷达探测距离涵盖愈来愈广泛,探测精度越来越高,使得航海安全更具保障。

近年来,随着加工工艺的突破,处理器的运算速度大幅提高,同时芯片功能更加强大。模拟信号采样芯片AD的采样频率已达到10 GHz。采样频率和数据处理芯片运算速度的提高推动着数据采集系统的发展。因此,专用的数据采集卡日渐成熟,并大量涌现。雷达回波信息数据采集可以运用专用的高速数据采集卡来采集,实现雷达回波信息的高速实时采集[1]。解放初期我国雷达研制技术相对比较薄落,航海上雷达的研制几乎是空白,国内的航海雷达几乎是靠国外进口[1]。随着这几年的发展,尤其改革开放以后,我国经济腾飞,在科技领域与国际先进水平的差距有了明显的改观。我国海岸线绵长,随着渔业的发展壮大,船用雷达市场需求打开,雷达专用的数据采集卡的普及应用将是未来的发展趋势。借此本论文提出一种雷达回波信息采集卡的技术方案。

1 硬件架构

1.1 硬件架构

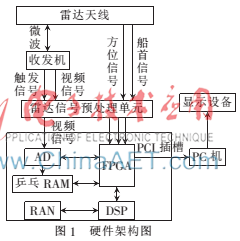

航海雷达由天线、收发机、雷达信号采集单元和显示器四部分组成,如图1所示。本文主要设计雷达信号采集单元,由天线和收发机产生的雷达信号包括视频信号、触发信号、方位信号和船首信号,它们不能直接被采集卡采集。为此,以上信号需要预处理之后才能被采集。信号经过转换电路后接入采集卡进行采集处理。采集卡主要芯片采用DSP和FPGA芯片,并使用PCI接口的方式与PC机主板集成,以达到雷达图像实时精确地显示采集到的信息。

1.2 雷达视频信号分析

本文以智森雷达RS1712作为实验雷达,视频信号幅度为-3.3~0 V,带宽20 MHz。信号参数不能直接接入AD采集,需要信号转换,转换接口电路如图2所示。航海雷达回波信息称之为视频信号,是由天线将接收到的高频信号经变频、检波后包络完成的信号。雷达视频信号属于一维信号,回波强弱代表有无目标障碍物。雷达回波的采集是实现雷达功能的重中之重,也是雷达系统信息处理最前端的工作部分。

雷达视频信号不同于传统意义上的视频信号,它是利用微波成像原理形成的,回波信号的强弱程度决定了图像上相对应处灰度值的大小[2]。不同障碍物其材质、形状和大小的不同导致反射电磁波的能力不同,雷达根据障碍物反射电磁波的强弱来呈现出目标。雷达视频信号是通过扫描线刷新来局部变化的图像。整个雷达图像是以灰度值的大小和强弱来显示海面上目标物的大小和有无。灰度值越高的点,采集的视频信号越强。由于视频信号夹杂大量的杂波,在采集完成后需要以适当的门限值来限制杂波的影响。雷达天线每旋转一圈形成一幅雷达图像,图像以极坐标形式显示。

1.3 雷达脉冲信号分析

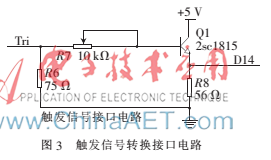

(1)触发信号:触发信号是整个雷达信号中的重要信号之一,是雷达的总指挥,它控制发射机、接收机、显示器同步工作。触发信号与接收机收到的雷达视频回波同步,由此确定一次回波的起点和显示器上扫描线对应的时间。本文实验雷达触发信号幅度约为6 V、脉冲宽度约为33.2 ms,信号参数不能直接接入采集卡,需要进行信号转换,转换电路如图3。

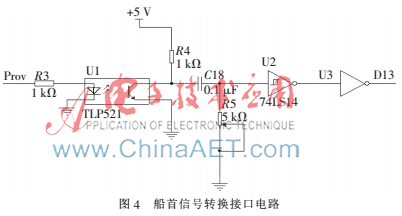

(2)船首信号:天线在旋转过程中,当转到正北或者船舶航行方向时雷达产生的信号。由此,该信号可以作为天线旋转一周的标志信号,同时可以作为视频信号处理中分隔两幅相邻图像的标志。本实验雷达的幅度为 +12.5 V。转换电路如图4。

(3)方位信号:方位信号是由天线产生,与天线旋转同步的信号。为了电路简单雷达在天线底部安装码盘,天线每旋转一圈通过码盘可以产生几百个增量脉冲,但在显示器显示前,利用锁相倍频电路将每周的脉冲调整到4 096或者更高[3]。本实验雷达天线旋转一周输出360个方位脉冲,幅度约为+12 V。转换接口电路如图5。

2 数据传输

2.1 AD的选择

本文实验雷达脉冲重复频率为f=1 500 Hz,脉宽τ=0.32  ,则雷达的发射波形伸展在S=Cτ≈100 m(C为光速)的空间距离上。对于同一方位向上的两个等同目标,当间隔距离S′=S/2=50 m时,它们在距离上可以被区分出来,即雷达的距离分辨率为50 m[4]。

,则雷达的发射波形伸展在S=Cτ≈100 m(C为光速)的空间距离上。对于同一方位向上的两个等同目标,当间隔距离S′=S/2=50 m时,它们在距离上可以被区分出来,即雷达的距离分辨率为50 m[4]。

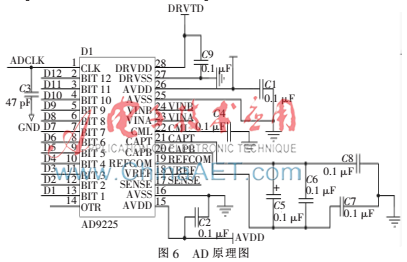

在采样中如何考虑采样速率和采样数据精度是一个重要的问题。当采样频率为f时,可根据公式△=C/2f(C为光速)得采样点的距离分辨率,所以为了使采样结果能够无失真地还原出雷达回波,需保证△大于或者等于S,即必须保证采样速率f>=1/τ。根据RS1712雷达的性能指标参数,雷达视频信号的带宽为20 MHz,因此数据采样带宽要求大于20 MHz,并且数字化的采样数据精度要求不低于10位。一般要求采样频率20 MHz以上,数据量大要求传输速度与处理速度要相匹配。本文选用AD9225芯片,采集速度25 MS/s,数据精度达到12位。图6为AD部分原理图。

2.2 快速数据流的传输

此方案利用FPGA来控制AD的工作。为了提高效率,采用乒乓缓存原理。乒乓缓存结构是在FPGA内部开辟出两个数据缓存区域,将数据等时地输入进去,区域的选择由选择标志位决定。在第一个周期内,将输入的数据缓存到数据缓存模块1中[5];在第二个周期内,将输入的数据缓存到数据缓存模块2中。以此类推,随着时间推移,缓存模块由输入选择标志位来控制。两个数据缓存区域缓解DSP处理数据的压力,同时避免数据处理错位。两个数据缓存区域循环往复依次切换数据输入输出,可以更加有效的进行数据采集传送。以下为FPGA中部分程序。

reg[8:0]data_addr;

always@(posedge ADCLK or posedge RST)

if(RST)

data_addr<=0;

else

data_addr<=data_addr+1;

reg pingpang;

always@(posedge ADCLK or posedge RST)

if(RST)

pingpang<=0;

else if(data_addr==511)

pingpang<=!pingpang;

reg[8:0]dpra;

wire[11:0]dpo1;

wire[11:0]dpo2;

always@(posedge ARE or posedge RST)

if(RST)

dpra<=0;

else if(~CE[2]&&(TEA==4′b0000))

dpra<=dpra+1;

3 技术方案

数据采集是雷达信号数字处理必不可少的前提,特别对雷达微弱信号的检测,良好且不失真的数据采集是处理的关键[6]。雷达视频信号数据量极大,实时性要求高,为此需要专门的信息采集处理板卡。DSP与FPGA结合构成采集板卡主控芯片。DSP可胜任数据处理功能,FPGA能够提供AD采集接口和数据传输通道。此外,利用高性能DSP芯片和PCI接口芯片,可有效提高雷达信号采集卡的通用性和扩展能力。采集卡使用德州仪器6000系列6713,这是一款浮点型芯片,运算速度可达1 350 MIPS,搭配一款赛灵思公司的FPGA型号XC2S200。

该板卡采用了一款高速12位的模数转换芯片AD9225,转换频率达到25 MHz,可以满足雷达视频采集的要求。数字信号处理模块以DSP作为核心处理器。DSP外接PROM和SRAM,其中,EEPROM存放程序代码用于DSP的boot loader,SRAM作为数据空间的扩展用于存储多次回波数据。首先,雷达上单元发出的视频信号经过高速AD采样后由FPGA控制写入乒乓RAN中,DSP收到相应中断信号时,读取数据进行处理,处理完成的信号写入PROM和SRAN等待上位机的读取。方位信号、船首信号和触发信号经过预处理接入FPGA中。方位信号经过FPGA电平逻辑转换,由倍频电路倍频至4 096 Hz,作为雷达信号的方位基准传输给显示模块。触发信号作为控制信号接入DSP中断,由DSP中断触发对视频信号的采集处理,以达到与上单元同步,同时区分每条扫描线的视频信号。船首信号经FPGA接入DSP中断,来触发对方位信号和触发信号计数清零处理,同时区分一幅完整的雷达图像。FPGA作为DSP的辅助器,协助DSP控制其外设器件。另外,为了便于调试,在板卡中增添串口模块、JTAG模块和USB模块。

3.1 FPGA的功能实现

FPGA负责控制AD采样、读取采样数据和与DSP通信的任务,以及对脉冲信号进行预处理[7]。FPGA将对AD的配置参数写入其相应的寄存器中。将输入时钟分频,产生采样时钟提供给AD。同时,FPGA直接对AD下达启动采样开始。FPGA监测AD的采样完成信号,若采样完成则通过AD并行数据接口接收一个采样数据,送入FPGA内部的开辟的乒乓RAN中,同时等待下一个采样数据的到来。当FPGA内部乒乓RAN存储满后溢出标志位触发DSP中断,DSP开始从数据总线中读取数据处理。

3.2 DSP功能

DSP负责数据处理和控制整个系统的协调运作。触发信号、方位信号、船首信号经过FPGA时序处理接入DSP中断,DSP通过对此信号的处理完成对雷达视频信号的解析,例如控制上下位机协同工作、确定雷达的分辨率、分割天线扫描一周形成的一帧图等。DSP有几个重要的控制中断:触发信号中断是AD采集开始及一条扫描线数据开始标志中断;船首信号中断是触发脉冲和方位脉冲计数清零标志,同时也是一幅完整雷达图像产生的标志,而且由此获得船首位置;FPGA数据溢出标志位中断通知DSP从数据总线中读取采集的雷达数据。

3.3 PCI接口

PCI接口是应用最为普遍、较为成熟的接口总线。PC机主板中常见的接口总线都能够方便地与PC连接,并且具有独立于CPU的结构,兼容性好。同时,它具有传输速度快、存储延误性小、成本低、可编程等优点。PCI接口有现成的模块,故此不再赘述。

4 结束语

本文设计的雷达信号采集卡,结合目前较为先进的硬件芯片,整合各个芯片的优点,实现对雷达的回波信号的高速采集。本设计中相关FPGA的程序用Xilinx ISE软件编写,DSP程序使用CCS软件完成程序设计。采用FPGA能够有效地控制AD的采集,同时,能够实时、高速地把数据传输出去,为雷达信号的实时采集处理、雷达图像的实时显示提供了保障。DSP是传统的信号处理芯片,运算速度快,能够在高速数据流中发挥它的优势。

参考文献

[1] 邱海琴.航海雷达回波数据采集与特性研究[D].厦门:集美大学,2011.

[2] 白雅卿.船舶导航雷达视频信号分析[D].大连:大连海事大学,2013.

[3] 郭鹏.雷达信号数字化单元研究[D].大连:大连海事大学,2006.

[4] 王立宁.导航雷达回波信号数据采集与压缩技术研究[D].哈尔滨:哈尔滨工程大学,2009.

[5] 邰林,黄芝平,唐贵林,等.并行缓存结构在高速海量数据记录系统中的应用[J].计算机测量与控制,2008,16(4):527-529.

[6] 张亚标,程家明,阎世强,等.一种雷达弱信号处理的视频回波数据采集系统[J].空军雷达学院学报,2003,17(1):31-33.

[7] 刘欢,田建生,梅安华,等.FPGA+双DSP结构的雷达信号采集处理系统设计[J].计算机测量与控制,2005,13(2):157-159.