文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.10.006

中文引用格式: 徐建松,俞拙非,侯凯,等. 一种基于FPGA的阀基电子设备的研制[J].电子技术应用,2015,41(10):27-29,33.

英文引用格式: Xu Jiansong,Yu Zhuofei,Hou Kai,et al. The development of VBE based on FPGA[J].Application of Electronic Technique,2015,41(10):27-29,33.

0 引言

随着直流输电技术和电力电子技术的迅速发展,晶闸管换流阀得到了广泛的应用。在高压直流输电中,控制保护系统(Converter Control and Pprotection,CCP)、阀基电子设备(Valve Base Electronics,VBE)和门极驱动单元(Gate Driver Unit,发射、分配、解析控制保护系统产生的触发命令并GDU)三部分构成晶闸管换流阀的二次触发监控系统,其在高压直流输电工程中主要完成以下功能:发送到晶闸管级;监测保护晶闸管器件不受过高电压的冲击;在阀内发生过流短路时能即时停止触发;对整个换流阀进行在线监测,上报设备与器件运行情况,并在出现故障时告警跳闸等。其稳定可靠性对换流阀系统的安全运行起着至关重要的作用[1,2]。

阀基电子设备主要由触发回路和监测回路组成,是换流阀触发监控系统的核心设备[1]。传统阀基电子设备的核心控制一般是由微处理器或数字信号处理器完成[3],由于软件执行的非实时性,加上控制通道数量越来越多,一些应用场合下VBE输出的各路PWM脉冲之间出现不可控的相位延时差,甚至存在脉冲丢失的隐患[1],系统的可靠性和同步性难以保证。随着电子技术的发展,具有并行高速处理能力的可编程逻辑器件被广泛地应用到阀基电子设备中来[3,4]。

本文依托国家重大02专项,提出一种以FPGA为控制核心的阀基电子设备的研制方法,将传统设备中处理器软件完成的工作以硬件逻辑的形式实现,设计了一种同步性好、可靠性高、扩展能力强的新型阀基电子设备,提高了换流阀系统运行的稳定性。

1 换流阀触发监控系统总体结构设计

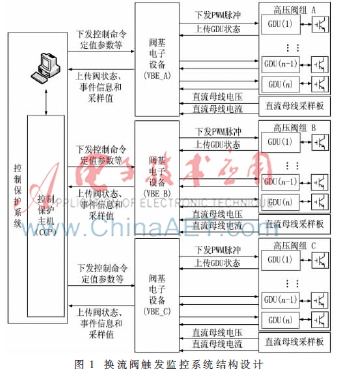

高压大功率电压源换流阀的子模块比较多,采样数据和触发命令的实时性直接影响电压源换流阀的控制性能,设计可靠高速的触发监控系统非常重要。目前最常用的触发监控系统方案是三级控制系统,包括控制保护系统、阀基电子设备和阀组驱动阵列。系统结构如图1所示。

控制保护系统是换流阀触发监控系统的控制核心,处于最上层,主要由PC上位机和控制保护主机CCP构成。上位机对整个系统进行监控,实现良好的人机界面,记录和显示试验波形数据等功能;CCP完成整个系统的控制保护,主要工作包括一次电量的采集,控制算法的设计与实现,对整个系统运行状态的检测和保护,响应上位机的控制命令,并将系统电量上传至上位机等。

阀基电子设备VBE是换流阀触发和监控系统的重要部分,处于中间层,VBE系统承上启下,接收上层CCP的控制要求,并通过光纤实时地下发触发指令并监控下层阀组门极驱动单元GDU;同时也接收GDU侧的状态信息和直流电流电压值,实时地进行分析处理,必要时下发保护关断指令,并将状态信息和电流电压值上报给CCP[5]。VBE的数量可以根据应用需要进行配置,图1系统所示每台VBE装置控制一相阀组,共需要3台VBE装置。

阀组门极驱动单元GDU是与一次侧晶闸管或IGBT直接相连的驱动控制电路单元,负责接收VBE侧的触发指令,直接对晶闸管或IGBT执行PWM开关控制;同时采集电流、电压、温度等模拟量,实时判断过流、过压、过温等状态信息,并汇总上报给VBE侧。

2 阀基电子设备的原理与设计

2.1 阀基电子设备系统结构设计

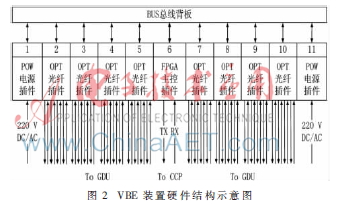

图1所示,一般情况三相换流阀对应的VBE系统由3台VBE装置组成,每台VBE可以实现对单相阀组上下桥臂多个晶闸管的独立触发监控。VBE装置硬件结构如图2所示,每台装置由主控插件(FPGA)、光纤插件(OPT)、电源插件(POW)、总线背板(BUS)4种板卡构成,装置机箱尺寸大小为标准3U机箱,共11个卡槽。

FPGA主控插件是VBE的控制中心,它通过一对光纤与控制保护主机实现HDLC协议通信。一方面,主控插件接收CCP下行发出的对应相的控制命令,通过FPGA完成命令解析,PWM生成和调制编码等逻辑处理流程,最终输出PWM命令;另一方面,FPGA主控插件汇总由OPT光纤插件通过背板总线上传的阀组状态信息,检测过流过温等报警信号,将这些状态信息通过光纤上报给CCP,必要时产生相应的中间层PWM保护动作命令。

OPT光纤插件是VBE与阀组驱动单元GDU的连接通道,每个OPT插件板配有4对收发光纤,可以控制4个GDU模块,每台VBE最多可以配置8块插件,这样最多可以控制32个GDU。OPT插件的主要工作是接收来自FPGA主控插件的PWM命令的差分电信号,将其转换为光信号从光纤发出;同时接收GDU上送的状态信息和告警信息光信号,将其转换为差分电信号送给FPGA主控插件。

POW电源插件是VBE装置的供电板卡,每个VBE配置两块相同的POW电源插件,安放在装置的两端,形成双电源冗余备份供电,以此来提高装置的运行稳定性。POW插件可以将外部的220 V交直流电经过开关电源的转换输出稳定的24 V直流电源,作为OPT插件和FPGA插件的工作电源。

BUS总线背板是VBE装置的内部信号总线通道,主要是负责FPGA插件和OPT插件之间的星形总线通信,为保证信号传输的质量,背板为无源设计,总线信号都换转为差分形式在背板传输,目前最大总线带宽能达到50 Mb/s。

2.2 FPGA主控插件设计

2.2.1 硬件结构设计

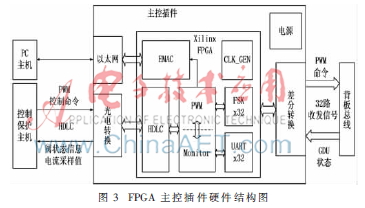

FPGA主控插件板卡主要包括一块FPGA芯片、一对光电转换器、以太网接口、差分驱动电路、与背板相连的高速接插件以及电源模块等。其中FPGA选用Xilinx公司Spartan-6系列XC6SLX25-FTG256芯片,包含25 K的Logic Cells、936 Kb的Block RAM和186个用户管脚等资源[6]。板卡的硬件结构设计如图3所示。

2.2.2 软件功能设计

软件功能主要由FPGA程序执行完成,程序编写采用Verilog HDL语言,片内的主要逻辑模块如图3所示,包括HDLC协议收发模块、PWM脉冲控制器、GDU状态监控模块、FSK调制解调模块、UART协议收发模块、以太网MAC控制器以及时钟复位模块等。

HDLC协议收发器主要负责通过光口与上层CCP通信,通信协议采用高级数据链路控制HDLC协议,主要负责接收CCP下发的PWM控制命令报文,并实时解析获取PWM的周期、占空比、死区时间、相位时延、开关使能等控制参数,同时汇总GDU监控模块上送的阀组状态及告警信息,组成数据报文上传给CCP。点对点HDLC协议全双工通信,数据报文透明传输,每帧数据均采用CRC校验,并且在与CCP通信故障的情况下能立刻产生PWM关断使能,保证了VBE与CCP之间报文传输的实时性和可靠性[7]。

PWM脉冲控制器接收逻辑解析得出的PWM的周期、占空比、死区时间、相位时延、开关使能等控制参数,通过计算和时序逻辑产生相应的上下桥臂互斥的PWM脉冲波形。GDU状态监控模块接收阀组中各路GDU上传的状态信息,主要包含光纤通断状态、工作模式、过流过温等告警信息,并实时地反馈给PWM控制器作为保护逻辑判据,在中间层实现阀组过流过温等情况下的快速保护功能。

传统的VBE装置一般都是将PWM脉冲直接以IO信号的方式通过光纤下发给阀组,以有光无光来表示PWM的打开和关闭,但当光纤通道出现问题或光电转换器出现故障时,阀组侧可能就会收到错误的PWM命令,从而导致阀组上晶闸管误动作甚至器件烧毁;但如果以报文协议的形式下发PWM命令,由于解析报文需要多个时钟周期,并且是异步时序逻辑,会给阀组上各晶闸管器件的PWM脉冲引入时延的不一致性,导致器件通断不同步,也会导致阀组故障的产生。鉴于上述两种命令下发方式的利弊,该VBE采用FSK频率调制方式对PWM信号进行编码后发送,也可以配置FPGA程序[8]使VBE采用IO信号或UART协议报文两种方式发送PWM命令,作为与FSK方式对比的实验方案。

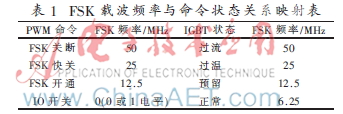

FSK调制解调模块主要是将PWM信号进行频率调制,利用载波的频率变化来传递PWM的开关信息,这样做的好处是可以区分PWM开通、正常关断、故障关断、无信号等多种控制命令,同样接收不同频率的载波也可以解析GDU正常运行、过流、过温、光纤通信异常等多种状态信息。FSK方式相比IO信号灵活很多,相比UART报文方式实时性要好,只是在调制解调过程中会引入极小的固定可预知延时。本VBE中采用的FSK载波频率与命令状态关系映射见表1。

3 运行实验及结果分析

该VBE装置用于10 kV电压源型变换器(VSC)的逆变实验。图4是系统联调过程的示波器波形截图,其中通道1、2测量的是VBE与CCP之间通信的HDLC帧,通道3、4为GDU接收到VBE的FSK信号后解调产生的一对互斥的SPWM波形。

经过实验测试,该VBE在CCP的管理下可以实现32路200 Hz~10 kHz的SPWM脉冲命令控制,占空比调节范围在5%~95%,各路PWM信号之间的时延偏差能满足应用要求,具体测试结果为:IO方式传输时延偏差在10 ns以内;FSK方式传输时延偏差在40 ns以内;UART协议传输时延偏差在100 ns左右,前两者都在器件时延容忍范围内。

4 结论

该VBE装置以FPGA芯片为控制核心,通过其高效的并行处理技术,将传统装置中软件程序实现的功能以电路逻辑硬件化实现,并采用FSK方式对PWM触发脉冲进行编码发送,使得装置对换流阀的监控具有可靠性、可扩展性和高精度的同步一致性,满足了实际工程的应用需求。

参考文献

[1] 周亮,汤广福,郝长城,等.换流阀阀基电子设备丢脉冲保护与控制的研究[J].电网技术,2011(7):222-226.

[2] 李宏.阀基电子设备的研究[J].科技成果管理与研究,2011(5):63-65.

[3] 郑月宾,陈国联,白云飞,等.一种冗余设计的直流输电用阀基电子设备[J].电源学报,2012(9):63-66.

[4] 赵中原,邱毓昌,方志,等.现代HVDC换流阀设计特点及其技术动向[J].高电压技术,2001,27(6):3-5.

[5] 袁清云.HVDC换流阀及其触发与在线监测系统[M].北京:中国电力出版社,1999.

[6] Xilinx.Spartan-6 family overview datasheet[Z].DS160.Xilinx,June 24,2009.

[7] 徐建松,姚晓明,骆健,等.HDLC协议在阀基控制通信中的应用[J].电子技术应用,2014,40(6):23-26.

[8] 解婷,郑健超,汤广福.部分重配置技术用于智能电网换流阀控制系统[J].高电压技术,2011,37(3):700-705.