摘 要: 基于TI公司的TMS320C6657芯片,结合片外的PHY芯片88E1112,实现了千兆以太网通信接口的设计。结合TCP/IP网络模型,详细描述了TMS320C6657片内千兆以太网接口模块以及通信接口的硬件设计,介绍了网络开发包NDK的结构并运用NDK完成DSP通信接口软件设计,最终实现了DSP与PC间可靠稳定的网络传输。

关键词: TMS320C6657;千兆以太网;NDK;Socket

0 引言

随着网络技术的不断发展,在DSP嵌入式系统上进行网络通信已经成为热门研究课题。对于网络开发而言,TI的C6000系列DSP芯片有很多都在其片上集成了以太网接口,不仅在硬件上缩减了嵌入式产品的网络应用成本,而且其推出的NDK网络开发工具在软件上大大降低了网络应用程序的开发难度,缩短了开发周期,为实现设计性价比高、易于实现的网络通信接口提供了可靠的保障。

TMS320C6657是TMS320C6000系列中高性能的定点/浮点DSP,建立在TI KeyStone多核架构基础之上,采用创新C66x DSP内核,此器件能够以高达1.25 GHz的频率运行,同时具有丰富的外设资源,能够方便地与其他器件进行通信[1]。本文通过TMS320C6657片内集成的千兆以太网接口模块,结合片外的PHY芯片88E1112以及简单的外围电路,实现了DSP与PC之间的千兆以太网通信。本文主要完成了通信接口硬件电路设计、通信接口软件总体架构设计、用户定制网络应用程序的编写等工作,最终实现DSP与PC间可靠稳定的网络传输。

1 千兆以太网接口的硬件设计

TMS320C6657内部集成了千兆以太网接口模块EMAC/MDIO/SGMII,下面对这三个模块分别进行叙述[2-3]。

EMAC(Ethernet Media Access Controller)模块是DSP处理器内核与片外的网络物理层数据传输的接口,负责以太网数据的接收和发送,接收和发送分别具有8个队列,能够满足快速收发以太网数据包的要求。它实现了IEEE802.3标准的以太网数据链路层协议功能;将从上层协议栈传递来的数据打包成符合IEEE802.3标准的以太网数据包,并从收到的以太网数据包中剥离出载荷数据,提供给上层协议栈进行分析和处理;提供了GMII/MII接口,能够与符合IEEE802.3标准的片外PHY芯片无缝连接。

MDIO(Management Data Input/Output)模块负责管理与EMAC相连的所有PHY芯片,包括对PHY芯片进行枚举、复位、配置和器件状态检测等。

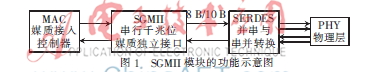

SGMII(Serial Gigabit Media Independent Interface)模块是连接数据链路层和物理层的接口,并具有内置SERDES(serializer/deserializer)电路,能够实现EMAC模块所使用的GMII数据格式与SERDES模块所使用的 8 B/10 B编码数据格式之间的转换。SGMII(Serial GMII)是串行GMII,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟,另外,SGMII有8 B/10 B编码,速率为1.25 Gb/s。其中,8 B/10 B编码是为了扰码,避免信号中出现过长的连“0”或连“1”情况,保证时钟信息的提取。SGMII模块具体的功能示意图如图1所示。

88E1112 PHY芯片是千兆以太网物理层自适应收发器,支持IEEE802.3标准,支持10/100/1 000 Mb/s全双工数据传输,内部集成SERDES,支持与SGMII/SERDES MAC连接。

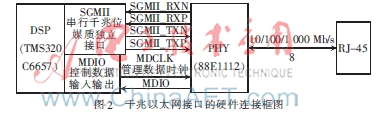

TMS320C6657与88E1112都提供了SGMII接口,两者之间可以在IEEE802.3标准基础上实现无缝连接。本方案中千兆以太网接口的硬件连接框图如图2所示。

图2中,SGMII_RXN与SGMII_RXP是SGMII的一对差分接收信号线;SGMII_TXN与SGMII_TXP是SGMII的一对差分发送信号线;MDCLK为管理数据时钟,该时钟信号由DSP片上的MDIO模块提供,用于同步MDIO管脚上的数据;MDIO为管理数据线,以向PHY写入或读出数据帧的形式对PHY进行配置。

2 千兆以太网接口的软件设计

本方案中,千兆以太网通信接口的软件设计主要是基于TI公司提供的嵌入式操作系统SYS/BIOS[4]和TCP/IP网络开发包NDK(Network Development′s Kit)[5-6]来实现的。网络开发包NDK是TI公司为本公司DSP的网络程序开发提供的平台,采用自顶向下、分层、模块化的设计方法来支持TCP/IP协议[7],并占用较少的系统资源(对于常规的TCP/IP服务,程序空间仅需200 KB~250 KB的程序空间,数据空间仅需95 KB)。TCP/IP协议的体系结构包括应用层、传输层、网络层、数据链路层以及物理层,对于NDK模型,网络开发包NDK就实现了5层体系结构中的传输层、网络层、数据链路层。图3为TCP/IP模型与NDK模型的对比示意图。

NDK通过编程接口与嵌入式操作系统SYS/BIOS以及底层硬件相互隔离。对于NDK而言,SYS/BIOS被抽象成一个操作系统适应层(OS Adaptation Layer),底层硬件被抽象成一个硬件适应层(Hardware Adaptation Layer),它们的函数库OS.LIB、HAL.LIB成为了NDK与SYS/BIOS以及底层硬件的接口。图4为基于NDK与SYS/BIOS的通信接口软件架构图[8]。

由图4可以看出,NDK主要包含NETTOOL.LIB、STACK.LIB、OS.LIB、HAL.LIB、NETCTRL.LIB五个部分。

(1)NETTOOL.LIB提供网络服务,包含NDK提供的基于网络服务的所有套接字以及一些用于网络应用开发的附加工具。

(2)STACK.LIB是主要的TCP/IP协议栈,提供了顶层(套接字层)至底层(以太网和PPP层)的所有功能。

(3)OS.LIB提供与SYS/BIOS操作系统的接口。

(4)HAL.LIB提供与底层硬件的接口。

(5)NETCTRL.LIB控制TCP/IP协议栈与外界的交互,管理所有网络事件、协调操作系统与硬件驱动,主要包括:①初始化TCP/IP协议栈和底层设备驱动;②启动和维护系统配置(通过配置服务提供者的回调函数);③连接底层设备驱动和安排驱动事件呼叫TCP/IP协议栈;④卸载系统配置和清除底层驱动。

对于基于NDK与SYS/BIOS的通信接口的软件架构,其实现主要分为三部分工作:

(1)编制底层驱动程序。底层硬件驱动负责向TCP/IP协议栈提供具体的操作接口,用以控制以太网器件的配置和运行,主要包括:初始化驱动环境,包括器件复位、中断使能、存储区数据访问优先级设定、器件枚举和配置等;以太网数据包的接收和发送;监测底层网络器件状态,将事件信息反馈给协议栈;关闭驱动环境,并收回占用的系统资源。

(2)在SYS/BIOS操作系统平台上配置和运行NDK的TCP/IP协议栈。CCS5.3提供了配置工具XGCONF来实现图形化界面配置NDK,如图5所示,传输层、网络层、数据链路层分别选用TCP、IP、EMAC协议,并对其作相关必要的配置,主要包括发送/接收窗口大小、IP地址、生存时间等内容的配置。

(3)开发用户定制的网络应用程序。本方案中主要是完成接收上位机控制信息和发送结果信息这些操作,采用流式套接字(Socket)来实现。

Socket是应用层与TCP/IP协议簇通信的中间软件抽象层,它是一组接口,把复杂的TCP/IP协议簇隐藏在其后面。对于用户来说,一组简单的Socket接口就是全部通信过程,让Socket去组织数据,以符合指定的协议。

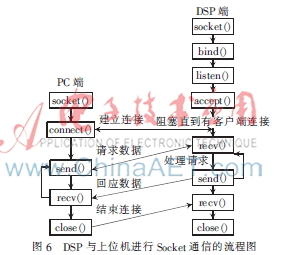

本设计中,选取DSP作为服务器,上位机作为客户端。对于DSP端,先初始化一个监听Socket,然后与端口绑定(bind),并对端口进行监听(listen),再调用accept阻塞,等待PC端连接。对于PC端,先初始化一个Socket,然后请求连接DSP端(connect),若此时DSP端正处于等待PC端连接状态,则DSP端接受此连接请求,于是,PC端与DSP端就成功建立起了连接。PC端发送数据请求,DSP端接收请求并处理请求,再把回应数据发送给PC端,PC端读取数据,最后关闭连接,一次交互结束。DSP与上位机进行Socket通信的具体过程如图6所示。

3 功能测试

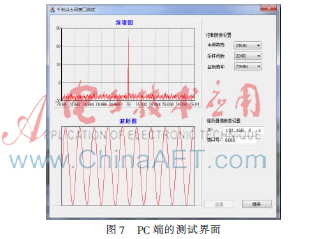

为了测试本文设计的千兆以太网接口的可行性,PC端采用VC++的MFC来设计测试程序,测试程序主要实现对单通道正弦信号的采集、处理以及显示等操作,测试界面如图7所示。根据具体的设计需求,测试程序分为数据发送/接收和数据处理/显示这两个部分。其中,数据发送/接收部分通过Socket编程完成与DSP的收发数据包等通信过程,数据处理/显示部分不仅能够支持用户对服务器端参数和控制参数的可配置,而且通过显示接收到的正弦信号时域波形与频谱图,实现对PC端与DSP端通信的直观体验,同时更增加了本接口程序的可移植性与可扩展性。

通过测试可以发现,正弦信号的时域波形图与频谱图较为流畅,且稳定性较高,能够支持长时间稳定可靠传输及显示。

4 结论

本文利用TMS320C6657内部集成了千兆以太网接口模块(EMAC、MDIO与SGMII),结合片外的PHY芯片88E1112以及简单的外围电路,提出了千兆以太网通信接口的软硬件设计方案,实现了DSP与PC的网络通信功能。测试结果显示,该设计方案能够实现长时间稳定可靠传输,同时,由于使用TI公司提供的NDK,降低了开发难度、缩短了开发周期,更便于扩展与维护。目前,本设计方案已成功应用到了无线电频谱监测接收机中,运行状况良好。

参考文献

[1] Texas Instruments. TMS320C6655/57 fixed and floating-point digital signal processor data manual[EB/OL]. (2014-05-11) [2014-07-12]. http://www.ti.com/lit/sprs814a.

[2] Texas Instruments. KeyStone architecture gigabit ethernet(GbE) switch subsystem user guide[EB/OL].(2013-07-03) [2014-07-12]. http://www.ti.com/lit/sprugv9d.

[3] Texas Instruments. KeyStone architecture Ethernet media access controller(EMAC)/management data input/output (MDIO) user guide[EB/OL].(2012-03-12) [2014-07-12]. http://www.ti.com/lit/spruhh1.

[4] Texas Instruments. SYS/BIOS (TI-RTOS Kernel) v6.40 user′s guide[EB/OL]. (2014-03-22) [2014-07-12]. http://www.ti.com/lit/spruex3n.

[5] Texas Instruments. TI network developer′s kit(NDK) v2.24 user′s guide[EB/OL]. (2014-04-21)[2014-07-12]. http://www.ti.com.cn/cn/lit/ug/spru523i/spru523i.pdf.

[6] Texas Instruments. TI network developer′s kit(NDK) v2.24 API reference guide[EB/OL]. (2014-03-21)[2014-07-12]. http://www.ti.com.cn/cn/lit/ug/spru524i/spru524i.pdf.

[7] 高翔,李凌,刘广存.基于TMS320VC5409的嵌入式WEB数据服务器的实现[J].电子技术应用,2007,33(7):72-74.

[8] Texas Instruments. TMS320C6000 network developer′s kit(NDK)support package ethernet driver design guide[EB/OL].(2011-08-06)[2014-07-12].http://www.ti.com/lit/sprufp2.