文献标识码:A

文章编号: 0258-7998(2014)11-0043-04

0 引言

传统的视频采集系统仅支持PAL和NTSC几种制式的视频数据,这些模式很难清晰地抓拍到目标快速变化的瞬时图片,而很多高帧频的摄像头只是对图像进行了简单的采集,并未处理和压缩。为了改善视频图像数据的信道传输和存储速度,降低对信道宽度以及存储空间大小的要求,本文设计了一种多接口、高速率传输的图像压缩系统。该系统不直接存储图像数据,而是由FPGA采集数字化后的视频图像数据,通过DSP将采集的数据进行编码压缩,然后再将编码压缩后的数据通过PCI高速传输给计算机,最后再通过计算机对图像进行解压缩并显示。

1 总体结构设计

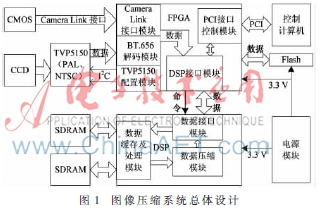

本设计结合FPGA处理速度快、DSP运算能力强等优点,提出了如下方案:通过FPGA模拟I2C总线时序,对模拟视频采集芯片TVP5150进行配置,并接收TVP5150输出的ITU-R BT.656格式的图像数据;同时,采用了Camera Link 接口,接收标准数字相机输出的图像数据。在FPGA完成对视频数据的采集并经内部FIFO缓存后,将数据打包并行传输给DSP,DSP对图像进行JPEG2000标准的压缩,压缩帧频不低于60帧/s,压缩比不小于20:1;压缩后的数据通过PCI总线传输给控制计算机,然后通过计算机对图像进行解码显示。

图像压缩系统的整体结构如图1所示,主要包括图像采集模块、FPGA控制模块、DSP压缩模块、PCI接口模块、电源和时钟管理模块。

视频采集模块使用了型号为PNT-698的CCD模拟摄像头,该摄像头帧频为25 Hz,场频为50 Hz,像素为720×576,输出为PAL制式图像信号,信噪比大于48 dB,并可以实现自动增益控制以及自动白平衡调整,输出接口标准为BNC。

2 硬件平台的搭建

2.1 视频接口协议设定

视频接口由8路并行数据和1路时钟信号组成,时钟为像素时钟,时钟周期T=1/1 728fN,fN为行频率,单位是Hz,fN=1/625(一帧图像为625行),脉冲宽度t=18.5±3 ns,数据保持时间为td=18.5±3 ns。

视频传输协议是以帧为单位传输,一帧图像的传输格式如图2所示。为了与标准电视图像扫描方式相兼容,采用隔行扫描,每帧625行,每行1 728 B。其中第1行~第23行和第311行~第336行为场消隐信号,主要针对视频数据场结束后扫描位置的重新定位,偶数场共288行(23~311),奇数场共288行(336~624)。

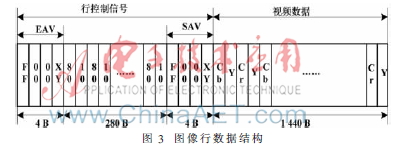

图像解码芯片TVP5150采用了同步信号嵌入数据内部的输出方式,所以需要对行数据结构进行研究。行数据结构如图3所示,一行共1 728 B,前288 B为行控制信号,后1 440 B为图像数据。行控制信号包括行开始标志SAV(Start of Active Video),长度为4 B;行结束标志EAV(End of Active Video),长度为4 B;行消隐信号280 B。SAV信号和EAV信号都由4 B组成,分别为FF、00、00、XY,前3 B为固定数,最后1 B XY表示该行数据在整帧图像中的位置信息。XY字节包含奇偶场标志、行消隐状态信息、场消隐状态信息。

视频图像数据为YCbCr 4:2:2格式,Y表示一个像素的亮度,Cb、Cr表示一个像素的色差信号,一个像素2 B,每行共720个像素,共1 440 B。视频数据格式为CbYCrYCbYCrY……CrY,因此可以理解为每个像素均有各自的亮度信号Y,但是共用一组色差信号Cb和Cr。在解包数据时,需要将它们分开,若需要显示,可以将YUV格式转换为RGB格式。

2.2 FPGA与DSP接口设计

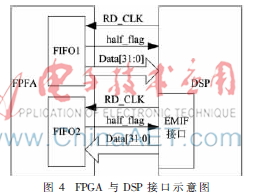

FPGA完成图像数据的接收后,经过格式变换及滤波将图像数据传输给DSP进行压缩。压缩打包完成后,又需要将数据回传给FPGA,通过FPGA控制PCI接口时序,将数据最终上传给计算机。为了满足图像数据高速、双向、实时的传输,在DSP与FPGA之间设计了两个高速的FIFO缓冲。

本系统中选用Spartan3系列的XC3S1400AN作为核心处理器[1],其内部储存资源丰富,内部Flash 16 Mbit, Distributed RAM(分布式RAM)176 Kbit,Block RAM(块RAM)576 Kbit。为了节约成本,同时考虑到系统的传输速率及可靠性,在FPGA内部IP核中创建了内部FIFO,数据宽度为32 bit,存储容量为3 M×32 bit。采用了独立的读时钟(RD_CLK)和写时钟(WR_CLK),数据达到半满,半满标志位置1(half_flag=′1′);达到满,满标志置1(full_flag=′1′)。

FPGA和DSP的接口如图4所示,视频数据采集、处理完成之后,FPGA通过FIFO的满标志查看FIFO是否已满,如果未满,则将32 bit图像数据在写时钟的逻辑控制下写入到FIFO;将半满信号连接到DSP的中断引脚,半满信号置高,会触发DSP的DMA进程,将FIFO中的图像数据读走[2]。同理,DSP通过EMIF外设接口将FPGA作为其外部存储空间,压缩后的数据通过DMA写到FPGA内部的另一个FIFO,半满信号触发FPGA内部读数进程,将数据读走,通过PCI总线上传到控制计算机。

2.3 DSP压缩模块设计

JPEG2000压缩算法硬件实现复杂度比较高,其核心算法离散小波变换和EBCOT算法计算量特别大[3],同时要考虑到实时性要求,所以对CPU的处理速度以及缓存空间等要求很高。因此在本次设计中,选择了TI公司C6000系列DSP中的TMS320DM642作为硬件平台。该DSP计算速度超过每秒64亿次,适合大数据吞吐量高速运算,比如在图像处理领域。同时,DM642拥有丰富的外设接口,包括可实现与SDRAM、Flash等外部存储芯片无缝数据连接的EMIF接口等,非常适合音视频解码、数字监控以及数字视频服务等应用[4]。

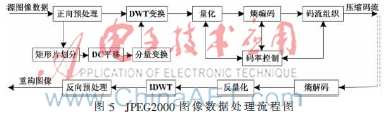

对图像数据处理流程如图5所示,源图像先经过正向预处理后进行离散小波变换(DWT),然后对变换的小波系数进行量化处理和熵编码,最后将熵编码后获得的图像数据打包成压缩数据包输出。解码则按照压缩码流中提供的各个参数将编码过程进行逆向操作,最终将源图像重构还原出来。

2.4 乒乓缓存设计

图像传感器单位时间内产生的数据是连续的,且数据量比较大,而DSP的编码速率是变化的。为了防止在编码过程中造成数据的丢失,需要在采集与编码电路之间设计一组帧缓存电路。

常用的缓存电路主要有FIFO、双端口RAM和乒乓缓存结构[5]。由于FIFO的存储容量太小,不适合图像视频数据的大吞吐量缓存。双端口RAM配备必须进行访问仲裁控制,设计较复杂。乒乓缓存结构克服了它们所有的缺点,输入的视频数据流以帧为单位交替地写入两个不同的SDRAM存储单元,在写入其中一块SDRAM的同时,将另一块SDRAM中的数据读出,并送到数据编码单元进行运算。这样数据的输入/输出都是不间断的,非常适合流水线式操作,完成数据的无缝缓存和处理。

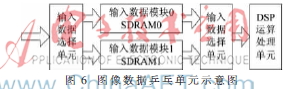

本设计中乒乓缓存结构如图6所示,DSP接收到FPGA传输的图像数据后,以帧为单位交替写入两块SDRAM存储器。与此同时,数据被交替读出,输出给数据压缩单元进行编码。数据流被严格有效地控制,不会出现丢数据或者误码,而且效率很高。选用MT48LC2M-

32B2作为外部高度SDRAM缓存器,读写速率可以达到6 ns,数据总线宽度为32 bit,容量为64 Mbit,而高频数字摄像头输入的一帧图像的大小为600×480×3=864 Kbit,完全可以满足要求。

3 逻辑功能的实现

3.1 TVP5150解码逻辑

TVP5150解码芯片输出的数据流中除了包含有效的视频图像数据之外,还包含行、场同步信号以及一些消隐数据。所以在视频解码时,需要根据同步信号以及ITU-R BT.656的标准格式将有效数据提取出来。

提取有效数据的流程图如图7所示,在时钟的上升沿对TVP5150输出的数据进行采样,若连续出现“FF”、“00”、“00” 3个固定字节,则表明出现了定时基准;如果第4 B出现“80”,表示一场数据的开始,而且为偶场,接着读取1 440 B图像数据。同理,若第4 B出现“C7”,表示奇数场数据的开始,接着同样读取1 440 B有效图像数据;否则,继续等待定时基准的出现。

3.2 DSP编码逻辑

DSP对图像数据的编码流程如图8所示,上电复位后,DSP程序从Flash起始处加载并启动,通过二次引导,最终将应用程序全部搬移到DSP内存中,然后跳转到入口函数c_int00(),完成初始化配置,并等待FPGA的外部中断触发信号。FPGA采集到数据后,缓存到接口FIFO中,并以中断的方式触发DSP的DMA进程,DSP以DMA的方式将数据存储到SDRAM中,若一帧图像传输完毕,则触发软中断,进入JPEG2000编码子程序。编码完成后,再次触发DMA进程,将数据回传给FPGA。 3.3 PCI传输接口逻辑

PCI接口主要用来下发上位机控制命令和系统参数,上传编码后的图像数据。采用PCI9054芯片来连接本地总线和PCI总线,PCI总线协议由PCI9054芯片内部处理,只需对其进行配置,并完成硬件接口驱动程序即可,PCI9054工作在C模式,内部采用了DMA数据传输方式[6]。

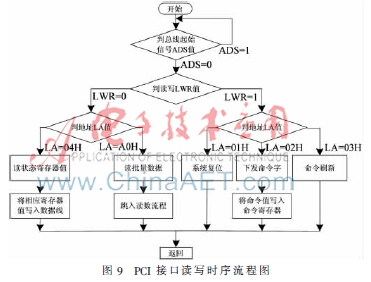

PCI接口内部逻辑流程图如图9所示,先判断总线启动信号ADS,若该引脚电平由高变低,则启动一次数据传输过程,然后判断读写信号电平LWR,若LWR为1,表示PCI写过程,否则为读过程。PCI读过程又分为读状态和读数据,通过地址总线LA来判断,读过程中,若LA=04H,则为读寄存器状态;若LA=A0H,则为读批量图像数据。而写过程中,若LA=01H,则为系统复位,立即执行,不写入寄存器;若LA=02H,则为命令下发,需要将命令字写入相应寄存器;若LA=03H,则为命令刷新,立即执行,不写入寄存器。

为了使得数据不丢失,在PCI接口设计过程中调用FPGA的IP核添加了FIFO数据缓存器,位宽为32 bit,与PCI总线位宽相匹配,深度为4 KB。由于PCI数据总线是双向传输,所以在FPGA内部增添了数据方向控制模块,保证了数据有序地下发和上传。

4 结果分析

为了比较压缩前后图像的质量,首先将未压缩的图片通过PCI接口传输给上位机并显示,如图10(a)所示,图像大小为407 KB,格式为BMP。然后保持源图片不变,将采集到的图像数据传输给DSP编码,编码后传输给上位机,经上位机解码后得到的图片如图10(b)所示,其大小为59.5 KB,压缩比约为10:1;图10(c)大小为15.2 KB,压缩比约为26:1。同时,图像数据通过PCI卡传输给上位机时最高速率达到了38 MB/s。

通过对比可知,压缩比越高,峰值信噪比越低,主观视觉的质量也会有所下降,局部细节有些模糊。总体来说,本次设计的新型图像压缩编码系统实现了预计的功能。

参考文献

[1] 邸丽霞.基于FPGA的高速图像数据采集存储系统设计[J].电视技术,2013,37(13):49-52.

[2] 李娟.基于FPGA的图像预处理及显示系统的设计[D].中国科学院研究生院,2011.

[3] 张晓娣,刘贵忠,曾召华,等.JPEG2000图像压缩编码系统及其关键技术[J].电视技术,2001(8):13-17.

[4] 郑红,刘振强,李振.嵌入式DSP应用系统设计及实例剖析[M].北京:北京航空航天大学出版社,2012.

[5] 周如辉.实时视频处理系统中乒乓缓存控制器的设计[J].电子元器件应用,2006(4):66-68.

[6] 原学山.基于PCI总线的图像采集卡的设计与实现[D].成都:西南交通大学,2006.