文献标识码: A

文章编号: 0258-7998(2015)03-0055-03

0 引言

随着CMOS技术和高水平硅集成电路的发展,片上数据传输率相比于十年前已经有了很大的提高。高的片上数据传输率直接大幅度提高了高端微处理器、智能路由器、光纤传输等产品处理和传输数据的能力。这也使电路对芯片外数据传输率的要求越来越高。但是CMOS和硅集成电路技术的发展对提高芯片外信号的传输速度影响甚微。普通的I/O接口电路要想提高数据传输速率就要消耗更高的功率,并以提高IC封装和PCB板电路的复杂度和成本为代价[1]。在这种情况下普通的I/O接口已经远远不能满足不断提高的高速传输数据的需要。同时随着便携式无线通信的发展,在高速传输数据的同时,对电路的功耗也提出了更高的要求。

1 LVDS技术

1.1 LVDS技术简介

LVDS接口技术正是在这样的背景下产生,并被广泛地接受。它是一种低振幅差分信号技术,这种技术使用的信号幅度非常低,通过一对差分PCB走线或平衡电缆进行数据的传输,具有低功耗、低辐射、高抗噪声等特点。

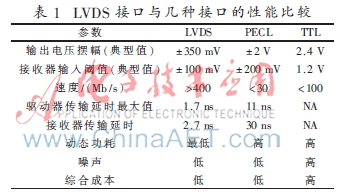

表1提供了LVDS接口和其他两种接口的比较。从表中可以看出,同为差分接口,LVDS与PECL相比,在传输速率、功耗、接收灵敏度方面都具有较大的优势。与TTL/CMOS相比,在高速、低抖动及其对共模特性较高的系统应用场合具有较大的优势。基于以上的优点,LVDS技术成为当今高速I/O接口中的首选技术[2]。

1.2 典型的LVDS接口电路及其局限性

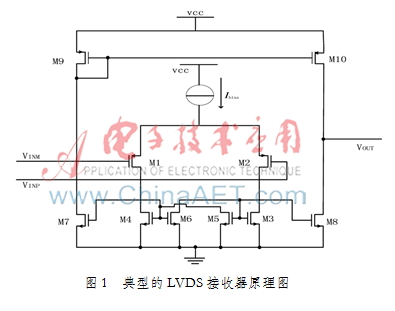

经典的LVDS接收器电路如图1所示。输入端输入的LVDS差分信号通过M1到M6组成的第一级放大器进行放大。第一级放大器的输出驱动反相器连接的M8和M10管,提高了输出信号的摆幅。这款经典的LVDS接收电路在输入信号的共模电压保持一个合适的范围时,基本能满足高速LVDS接口电路的要求,但是如果电路要满足LVDS接口标准,输入的共模电压在0.05 V~2.4 V之间发生变化时,就会存在若干问题[3-4]。

首先,如果没有采用低阈值的器件,当输入的共模电压达到最小值0.05 V时,M1和M2会进入到线性区,这将会导致放大器增益的下降,使第一级的放大器不足以去驱动第二级的输出反相器,而使输出信号的幅度大大减小。其次在放大器共模输入电压的变化引起增益的变化的同时,也会导致放大器延时发生较大变化,在高速传输数据的情况下,这将导致高的误码率。用轨到轨输入的全差分放大器可以解决这个问题,但是这将会导致电路功耗大大提高。

2 LVDS接收器的设计

接收器支持输入共模电压的范围为0.05 V~2.4 V,最小的差模输入电压的幅度为100 mV,最高传输数据率在600 M/s以上。这款接收器相比于文献[3]、[4]设计的接收器具有更低的功耗。此外这个接收器通过使用3.3 V器件和1.2 V器件,把信号转换到1.2 V水平,以提供给后续核心逻辑模块应用。

2.1 LVDS接收器原理图设计

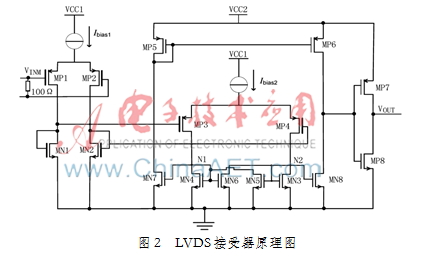

根据LVDS I/O接口标准的规定,LVDS接收器要满足输入差分信号的共模电压范围为0.05 V~2.4 V,输入信号的差模电压范围为100 mV~400 mV[5-7]。LVDS接口标准要求所设计的LVDS接收器要在很宽的共模输入电压范围下工作。然而一般的差分放大器共模输入电压在这么宽的范围内发生变化时,放大器的增益也会发生很大变化,同时放大器增益的变化也会引起放大器的延时随之发生变化。在高速数据传送的情况下,放大器延时较大的变化,会使接收端接收的数据出错,从而影响到数据的传输。为满足LVDS接口标准的要求,设计的LVDS接收器采用了两大部分,第一部分为一个差分放大器,对输入信号进行预放大;第二部分为比较放大器。第一部分的差分放大器主要考虑共模输入电压在大范围发生变化时,放大器的增益尽量保持一个常数,并提高放大器的增益带宽积;第二部分的比较放大器主要考虑提高放大器的增益和输出信号的摆幅,使输出信号的幅度满足后续电路的要求,并把信号转换到采用1.2 V电源供电的电路所需要的水平,以供后续电路使用。LVDS接收器原理图如图2所示。

2.2 LVDS接收器原理图分析

在第一级差分放大器中,由于输入端共模输入电压范围为0.05 V~2.4 V,因此第一级差分放大器采用了3.3 V(VCC1)电源供电,使用了SMIC 0.13 μm工艺提供的厚栅氧化(3.3 V)器件,在电路中用粗的栅符号表示,电路中其余的器件为薄栅氧化(1.2 V)器件。本设计中的第一级放大器选用了OTA结构,为了满足LVDS接口标准对输入共模电压范围的规定,采用了两个PMOS管(PMOS1和PMOS2)为差分输入管,两个NMOS(NMOS1和NMOS2)管连接成二极管的形式做负载。此差分放大器的增益只与输入管和负载管的宽长比有关,而与共模输入电压范围几乎无关,具有很高的线性度和增益带宽积,此外输出的差分信号共模分量也与输入共模电压几乎无关,为下一级放大器提供一个较为稳定的共模输入电压。

LVDS接收器的第一级放大器虽然有很高的线性度和增益带宽积,但是却以牺牲增益和输出信号的摆幅为代价,所提供的信号增益和摆幅十分有限。为了提高放大器的增益,第二级比较器的第一级在OTA结构的基础上,加入了Hysterics结构(NMOS3到NMOS6,如图2所示。输入管PMOS3和PMOS4采用厚栅氧化器件,负载管NMOS3到NMOS6采用薄栅氧化器件,由于0.13 μm工艺中要求薄栅NMOS器件的漏极电压不高于1.4 V,因此在设计时应该选择合适的工作点,保证电路工作时N1点和N2点的电压在任何情况下都低于1.4 V。比较放大器的第一级由于采用了OTA结构,因此输出的摆幅受到限制,为了提高输出信号的摆幅,加入了由NMOS7、NMOS8、PMOS5、PMOS6薄栅氧化器件构成的第二级放大器,并由1.2 V电源电压(VCC2)供电,提高输出摆幅的同时也使输出信号满足该工艺常用的1.2 V电源供电电路的需要。在比较放大器之后接入由一级反相器构成的缓冲器,为后续电路提供所需要的矩形波信号。

3 后仿真结果

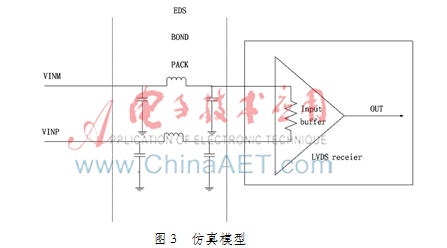

设计采用SMIC 0.13 μm CMOS工艺,并用Cadence提供的spectra进行仿真。为了减小ESD保护电路和封装电路对接收电路的影响,在仿真时加入了焊盘、ESD保护电路和封装电路的模型。ESD电路的寄生电容选为2 pF,封装电路的寄生参数为2 nH和5 pF[3],等效电路如图3所示。

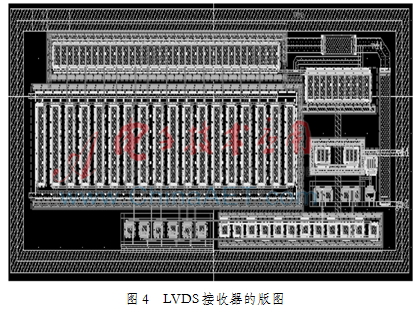

本次设计的版图如图4所示。版图不包括焊盘的面积为90 μm×30 μm。

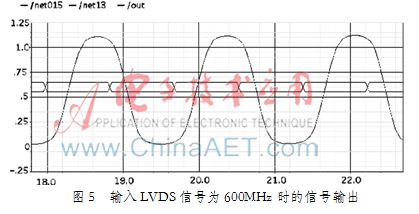

图5给出了该电路在数据传输速度为600 Mb/s时的输出信号瞬态后仿真结果。图中输入的LVDS差分信号幅度为100 mV,频率为600 MHz。

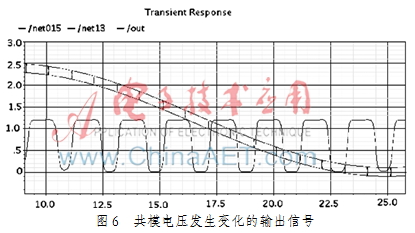

图6为该电路在输入共模电压发生变化时输出信号的瞬态后仿真结果。其中输入的共模信号为30 MHz的正弦波,变化范围为0 V~2.4 V,输入的差模信号频率为500 MHz,Vp-p幅度为200 mV。从仿真结果可以看出,当输入的共模电压从0 V~2.4 V发生变化时,芯片仍能正常工作。

4 结论

本文采用LVDS信号(低电压差分信号)进行数据传输,设计低功耗高速LVDS接收器,相比于常用的ECL技术,在提供传输速度的同时,能够较大地降低功耗。设计在不同的工艺角下进行仿真,数据传输率都能达到600 Mb/s以上,共模电压输入范围为0.05 V~2.4 V,差模输入电压范围为100 mV~400 mV,符合LVDS接口标准的规定,同时芯片的功耗仅为1.26 mW。

参考文献

[1] Chen Mingdeng.Low-voltage,low-power circuits for data communication systems[D].Texas A&M University,2003.

[2] 谭炜峰.高速LVDS发送器设计[D].成都:电子科技大学,2009.

[3] BONI A,PIERAZZI A,VECCHI D.LVDS I/O interface for Gb/s-per-pin operation in 0.35-μm CMOS[J].Solid-State Circuits.2001.

[4] Zhao Fei,Xu Yong,Li Miaoying,et al.A LVDS transceiver chip design in 0.5μm CMOS Technology[C].Congress on Image and Signal Processing,CISP,2008.

[5] MANDAL G,MANDAL P.Low-power LVDS receiver for

1.3Gbps physical(PHY) interface[C].IEEE International Symposium on Circuits and Systems(ISCAS),2005.

[6] TIA/EIA-644-A,TIA/EIA,standard,Electrical characteris-tics of low-voltage differential-signaling(LVDS) interface circuits[S].2001.

[7] 1596.3 SCI-LVDS Standard.IEEE Std.1596.3-1996.IEEEstandard for low-voltage differential signals(LVDS) for scalable coherent interface(SCI)[S].1996.