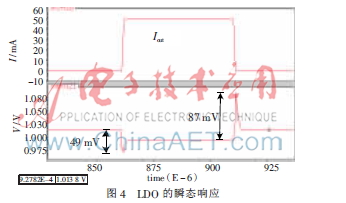

摘 要: 设计了一种基于电容倍增的无电容式LDO,将电容倍增模块嵌入到了误差运算放大器的第一级,提升了系统的环路带宽,有良好的瞬态响应。电路通过0.13 m标准CMOS工艺仿真实现,仿真结果显示,系统静态功耗为42 W,当负载从0~50 mA变化时,电压最大波动为87 mV,建立时间为2.5 s。

关键词: LDO;电容倍增;瞬态响应

0 引言

作为电源管理芯片中重要的一员,低压差线性稳压器(Low-Dropout regulator,LDO)因其纹波低、噪声低、体积小等优点被广泛应用到各种便携式电子产品(如手机、PDA等)中。传统的LDO利用片外大电容稳定其输出电压,但是不易于系统集成[1-3]。与传统的LDO相比,无电容式LDO不需要较大的片外电容,易于系统集成,然而其稳定性和瞬态响应成为设计的难点。为了保证无电容式LDO的稳定性,通常利用米勒效应来实现极点分类,为了达到足够的相位裕度,通常需要采用较大的米勒补偿电容,消耗较大的芯片面积。参考文献[4]提出了一种经典的电容倍增技术,但是其电容倍增系数受到电流镜电流之比的限制;参考文献[5]提出的电容倍增技术能提高电容倍增系数,有效地减小所需补偿电容的面积,但由于误差放大器输出节点的非对称性,为系统引入了失调,影响了LDO的线性调整率。

本文提出LDO结构,将电容倍增技术嵌入到第一级,使得第一级完全对称,且能提高环路带宽,提高了环路瞬态响应速度,电路采用0.13 m标准CMOS工艺仿真实现。

1 电容倍增技术

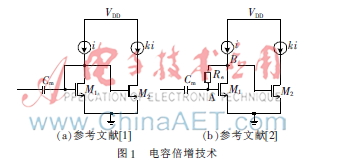

参考文献[1]提出的电容倍增技术如图1(a)所示,该技术基于电流模式实现,其原理为:采样流过电容的电流,通过电流镜实现放大后再反馈到电容的另一端,以实现电容倍增效果。其等效电容为(1+k),其中k为电流镜的放大系数。

参考文献[2]采用的电容倍增技术如图1(b)所示,在M1的栅极和漏极之间插入了一个电阻Re,同样能实现自偏置效果,无需额外的偏置电路。A点仍为低阻节点,但是B点不再是低阻节点,因此流过Cm的电流通过Re和M1放大成电压V1,然后通过M2再次转换成电流。其等效电容可表示为:

Ceq=(1+k)gm1RbCm(1)

从式(1)可以看出,其等效电容与参考文献[1]中提出的电容倍增技术相比,提高了gm1Re倍,因此对于固定的负载电容,所需要的片上补偿电容大大减小。

2 LDO电路设计

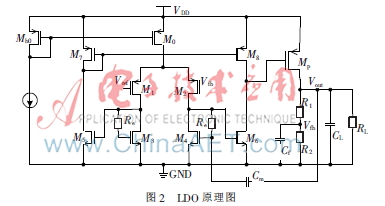

本文提出的LDO结构如图2所示,主要包括三部分。第一级全对称的运算放大器由M0~M8和电阻Re组成,其中包括由M3、Re、M5和M4、Re、M6组成的电容倍增模块,该模块嵌入第一级,与参考文献[2]相比,功耗减小了。同时第一级为完全对称结构,因此能减小失调。第二级运算放大器由功率管Mp和采样电阻组成。第三部分为频率补偿部分。Vref为带隙基准源产生的基准电压;Cm为米勒补偿电容;RL为负载电阻;CL为负载电容,为100 pF。

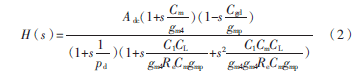

为了分析环路的稳定性,求出其传输函数为:

其中,gmi为Mi的跨导,R1为第一级输出电阻,Ro为第二级输出阻抗,C1为第一级输出电容,其值分别为:

Ro=(R1+R1)//Rp//RL(3)

C1=Cgs_p+ApassCgd_p(4)

Adc和pd为运算放大器的直流增益和主极点,分别为:

Adc=kgm1gmpR1Ro(5)

![V{ZG9GJZ6JBP19@]L}OTC9C.jpg V{ZG9GJZ6JBP19@]L}OTC9C.jpg](http://www.ninimall.com/files/images/2015/06/24/6357077349023700009230179.jpg)

由式(7)可以看出,本文提出的LDO结构具有大的电容倍增系数,同时与参考文献[5]相比,GBW提升了k倍,因此具有更好的瞬态特性。

3 仿真实验

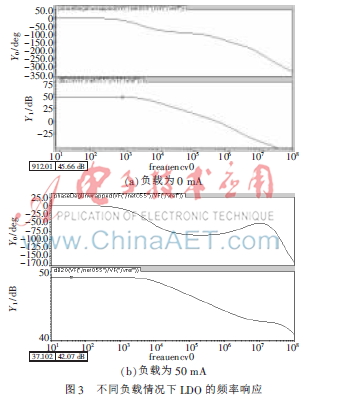

为了验证本文所提出的LDO的合理性,对图2所示的电路采用0.13 μm 标准CMOS工艺仿真验证,当工作温度为25℃、输入电压为1.2 V、输出电压为1 V、负载电容为100 pF时,由于采用了本文提出的电容倍增技术,片上补偿电容仅为0.8 pF。空载和负载为50 mA时,LDO环路频率响应曲线如图3所示。

仿真结果显示,在0~50 mA全负载范围内,最小增益为45.66 dB,单位增益带宽为570 kHz,相位裕度为60°,反馈环路具有很好的稳定性。同时由于将电容倍增模块嵌入到了误差运算放大器的第一级,因此提高了环路的单位增益带宽。

当负载从空载跳到50 mA然后再跳回空载时,系统的瞬态响应如图4所示。仿真结果显示,上冲电压为87 mV,调整时间为2.5 s;下冲电压为49 mV,调整时间为2.0 s,由于系统单位增益带宽得到了提升,因此具有良好的瞬态响应特性。

4 结论

本文设计了一种新型的LDO,分析了电容倍增技术的原理,且将电容倍增模块嵌入到了误差运算放大器的第一级,提升了系统的环路带宽,有良好的瞬态响应。电路通过0.13 m标准CMOS工艺仿真实现,结果显示,系统静态功耗为42 W,当负载在全负载范围变化时,电压波动最大为87 mV,建立时间为2.5 s,能够满足SoC系统中供电电源的要求。

参考文献

[1] 应建华,黄杨,黄萌,等.基于电容倍增技术的LDO补偿方法[J].微电子学与计算机,2009,26(11):102-105.

[2] 刘明亮,明鑫,欧雪春,等.一种带过温保护和折返电流限的LDO设计[J].微电子学与计算机,2011,41(3):411-415.

[3] LIN H C, WU H H, CHANG T Y. An active-frequency compensation scheme for CMOS Low-Dropout regulators with transient-response improvement[J]. IEEE Transactions on Circuits And Systems-II: Express Briefs, 2009,55(9):853-857.

[4] GABRIEL A, RINCON-MORA. Active capacitor multiplier in miller-compensatedcircuits[J]. IEEE Transactions on Solid-State Circuits, 2000, 35(1):26-32.

[5] MILLIKEN R J, Silva-Martínez Jose, Sánchez-Sinencio Edgar. Full on-chip CMOS Low-Dropout voltage regulator[J]. IEEE Transactions on Circuits and Systems-I: Regular Papers, 2007,54(9):1879-1890.

[6] 王晋雄,原义栋,张海峰.一种高线性调整率无电容型LDO的设计[J].电子技术应用,2012,38(11):44-47.