小梅哥和你一起深入学习FPGA之数码钟

2015-05-26

实现数码时钟的功能,要求能够进行24时制时、分、秒的显示,并能够通过按键调整时间。

二、 实验原理

通过对系统时钟进行计数,获得1S的标准信号,再以该信号为基础,进行时、分、秒的计数,通过数码管将该计数值显示出来,即可实现数字钟的功能。同时可以使用独立按键对时、分、秒计数器的初始值进行设置,即可实现时间的设定。

三、 硬件设计

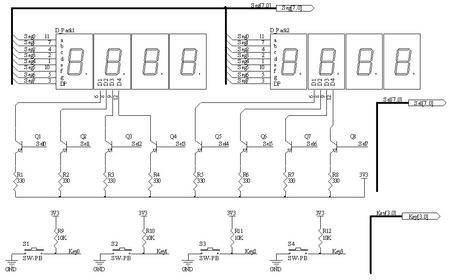

本实验硬件电路简单,用到了8个数码管和4个独立按键。硬件电路如下:

图3-1 数字钟电路

四、 架构设计

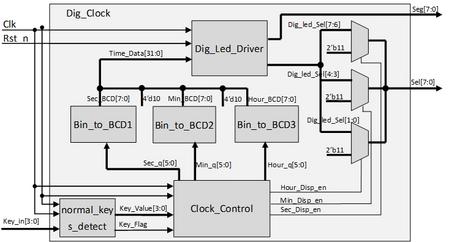

本实验设计架构模块较多,下图为数字钟的架构:

图4-1 数字钟实验模块组织结构图

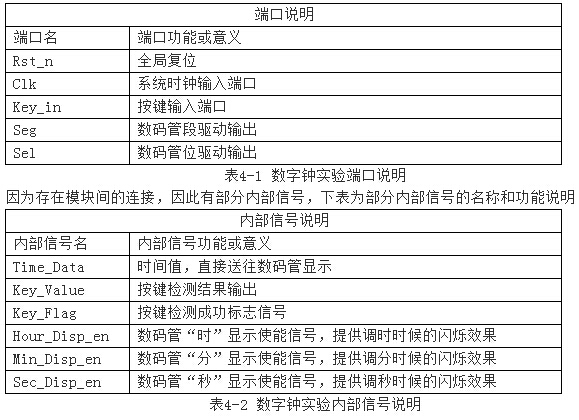

由图可知本实验有16个输出端口和6个输入端口,各端口的意义如下

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。