摘 要: 根据TMS320C6678芯片的特点,针对核间、片间、板间的通信要求,提出了一种跨系统的透明传输模型及实现,并分析了传输性能,对基于TMS320C6678的嵌入式软件系统设计提供了指导。

关键词: TMS320C6678;多核通信;平台软件

TMS320C6678是TI公司2010年11月发布的KeyStone架构的8核DSP处理器,每个CorePac核的频率最高为1.25 GHz,提供强大的定点和浮点运算能力,同时芯片内部集成了Multicore Navigator、RapidIO、千兆以太网和EDMA等外设,由于芯片处理能力强,外设功能丰富,而且片内集成了大量的硬件加速器,例如Packet Accelerator、Multicore Navigator等,被广泛地应用在通信、雷达、声纳、火控、电子对抗等领域。从目前的情况看,由于C6678的以上优异的特性,基于TMS320C6678的硬件和软件平台,在未来的5~10年内,将是信号处理平台主流。

虽然TMS320C6678硬件优点众多,但由于芯片内部集成了8核,而且有大量的外设及加速器,通常每个板卡单位上有4个TMS320C6678,相当于32个DSP核,按照一个机架4块板卡的设计,这将是一个128个DSP核的阵列,而且节点间的连接方式复杂,如何简单、高效、易调试地实现128个分布式节点的通信,为平台软件设计者提出了极高的要求。

针对基于TMS320C6678分布式系统的特点,本文首先分析了TMS320C6678的硬件通信方式及设计难点,进而提出了一种基于透明传输的分布式系统通信方式及实现,最后通过实验给出了性能分析,为基于TMS320C6678的平台软件设计提供了参考。

1 核间、DSP间和板间的传输方式

由于TMS320C6678芯片高度集成的特性,片内除了8个CorePac内核外,还集成了以太网、EDMA、RapidIO、PCIe以及Multicore Navigator、Packet Accelerator协处理器等外设。

在多个TMS320C6678的板卡设计中,芯片内的核间通信,通常采用共享内存或DMA实现,因为TMS320C6678中有专门用于数据搬移的协处理器Multicore Navigator,因此芯片内的核间通信用基于硬件队列协处理器的CDMA实现。特点是速度快、效率高,缺点是编程复杂,学习周期长。

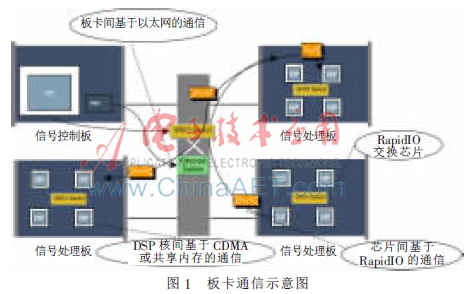

在雷达、声纳等应用中,一般在一块DSP处理板上设计多个TMS320C6678处理器,在一个机架上插多块DSP处理板卡来承载大数据量的处理。对于板卡内DSP间通信,以前可能会经常采用PCIe的设计,但目前的主流设计,倾向于采用RapidIO的通信方式,因为虽然PCIe有架构简单、编程容易等特点,但是PCIe一般只能用作设备内的通信,而且对于复杂的阵列节点间的通信就力不从心。因此RapidIO这种高效、可靠、跨设备的传输方式被用作DSP间、板间传输的主要方式。对于大数据量的传输,一般会采用RapidIO type5、RapidIO type6以及RapidIO type10、RapidIO type2混合的模式。由于TMS320C6678支持千兆以太网传输,在某些TMS320C6678阵列的板卡设计中,例如Advantech DPS8901单板20个TMS320C6678的阵列,DSP间以及CPU和DSP间还会采用基于以太网的传输方式。板卡通信示意图如图1所示。

综上,在一个板卡的软、硬件系统设计中,单位节点之间交互有如此多的接口和通信路径,使平台软件的设计和编程工作变得异常复杂。比如节点A和节点B之间,底层通过CDMA连接,节点B和节点C之间底层通过RapidIO通信,如果没有一种好的上层通信机制,节点A向节点C发送数据,这一过程是非常繁琐和复杂的,如图2所示。

因此,为解决分布式系统节点的透明传输问题,本文提出一种跨核、跨处理器、跨板卡、跨系统的透明传输机制LINX及软件实现,下面将详细阐述LINX模块的机制和通信模式。

2 统一接口的分布式透明传输模式

针对TMS320C6678板卡设计中复杂的底层接口状况,提出一种点对点的分布式系统节点间的透明传输模型,称之为LINX。

这一分布式透明节点间传输模型应具有以下特性。

(1)统一接口、使用简便。从系统架构的角度,LINX设计为统一应用程序接口的中间件模型,即不管底层是何种传输介质,例如SRIO、以太网、CDMA等,对于应用程序来说,对于跨介质传输,均使用统一的接口函数。统一通信接口的好处是显而易见的,因为对于应用程序开发者,可以直接调用统一的接口,跨介质进行数据的收发。

(2)跨介质传输。传输模型设计为分层架构,不同的底层链路驱动按照一定的格式,通过统一抽象的接口例如发送、接收、初始化、查询、响应中断等基本接口,与LINX中间件层对接。对于跨多个节点的传输,提供简单的链路定义及使用的方式。

(3)错误检测。具有基本的错误检测功能,当LINX模块检测到底层链路错误时,应及时上报给通信节点。而且对于不可靠传输介质,比如基于共享内存的通信方式,还需要提供可靠传输保证,例如用心跳机制的发送/应答,对不可靠的链路提供通信安全保证。

根据以上特性,提出的LINX传输模型如图3所示。自下而上依次是驱动层、传输层、会话层以及应用程序接口。

其中驱动层负责具体的驱动链路实现;传输层负责与驱动层接口,底层的监控和检测重传;会话层负责和传输层接口,进行链路名管理、链路路径的搜索并提供应用程序接口。

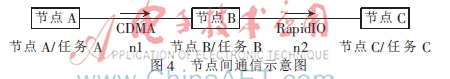

LINX采用点对点的传输模型,如图4所示。节点为TMS320C6678的CorePac核,节点A与节点B之间通过CDMA驱动通信,链路标识号为n1,那么节点A上的任务A给节点B上的任务B发送数据,可通过接口写成Send(n1/B,&data)。

同理,节点A上的任务A通过节点B,向节点C上的任务C发送数据,经过CDMA和RapidIO两个链路,分别标识为n1和n2,那么可通过接口写成Send(n1/n2/C,&data)。

由此可见,在TMS320C6678的阵列中,使用基于LINX中间件架构构建的分布式系统通信方式,实现跨介质的传输,通信接口非常简便。对于系统设计来说,可达到各个节点间的无缝传输。由于LINX是基于底层驱动的中间件管理模块,在驱动之上会增加一些负载,下面是LINX模块的软件实现,在TMS320C6678EVM开发板卡上所做的性能测试实验,用以评估LINX模块对传输性能的影响。

3 分布式透明传输模式的性能测试

由于RapidIO在多DSP及多板卡的集群设备中是最常用的一种接口,因此以RapidIO为例测试LINX基于RapidIO传输在TMS320C6678上的性能。

本测试基于标准TMS320C6678EVM开发板,测试采用OSEck硬实时操作系统,内核代码在L2 Memory上,其他驱动、中间层LINX所使用的数据区以及应用层所用的内存池均位于片外的DDR3存储器上,测试的时间周期使用硬件定时器Timer 10(0x022A0000)测量,TMS320C6678主频为1 GHz,RapidIO配置为5 Gb/s、4x模式,采用DirectIO(SRIO type5/6)方式通信。

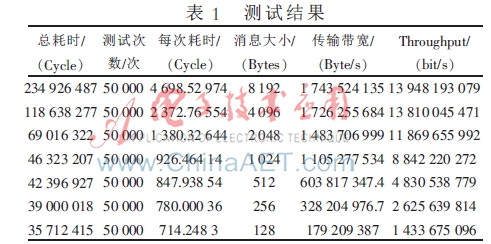

TMS320C6678核0发送数据,核1接收数据,1核在收到之后向0核回送,每次测试一个回环耗时,测试连续进行n次,由发送端设置时间戳进行连续统计测试,统计单位1 cycle等于1 ns,如表1所示。

其中,总耗时为测试n次之后的单向传输耗时;测试次数为总的测试次数;每次耗时为每次单向发送数据时,从任务发出数据到对方节点收到数据所消耗的时间;消息大小为发送数据块的大小;Throughput为传输带宽。Throughput的计算公式为(消息大小/(总耗时/测试次数))×1 000 000 000×8(单位bit/s)。

按照理论计算,RapidIO 5 Gb/s模式下的去除8 b/10 b编码后的理论有效带宽是4 Gb/s,然后还要去除驱动、中间层及应用层的系统开销,最终的实际有效带宽不超过理论有效带宽的80%。

从测试结果看,在采用LINX中间件架构构建的分布式系统通信方式下,传输带宽随发送的数据增大而增大,由于TMS320C6678的RapidIO传输硬件限制,传输的数据包最大不超过1 MB。一般采用RapidIO传输的数据量是比较大的,典型情况下在传输大于4 KB的数据时,带宽趋向稳定,结果接近于有效实际带宽。

因此,采用LINX中间件架构构建的分布式系统,在使用简便、跨介质传输和有效错误检测等优点特性的基础上,在大数据量的传输模式下,性能接近于直接驱动模式。

目前TMS320C6678芯片被越来越广泛地使用在通信、雷达、声纳、电子对抗等领域,由于系统设计日益复杂,通信接口多样,需要分布式的透明传输中间件模块,把系统中几十个乃至上百个TMS320C6678内核节点无缝连接起来。针对TMS320C6678核间、片间、板间的通信要求,本文提出了一种称为LINX的分布式系统节点间的透明传输模型,提供了实现方法及性能测试数据,为基于TMS320C6678芯片的系统软件设计提供了参考。

参考文献

[1] Texas Instrument TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor[R]. SPRS691, 2010.

[2] KeyStone architecture serial RapidIO(SRIO) user guide[R]. SPRUGW1,2010.

[3] 彭益智.一种基于TMS320C6678的JPEG编码算法并行实现方法[J].指挥控制与仿真,2012,34(1):121.

[4] 郑章汝.基于TMS320C6678的雷达信号处理机设计[J].工业控制计算机,2012,25(11):14.

[5] 齐恩勇.基于多核处理器的弹载嵌入式系统设计研究[J].电子设计工程,2013,21(6):105.