正交频分复用(OrthogonalFrequency Division Multiplexing,OFDM)技术已经成为第四代移动通信研究的热点,同时,OFDM同步又是OFDM的关键技术,研究OFDM同步技术的目的就是为了防止码间干扰和载波干扰。当前OFDM同步的算法是根据OFDM原理提出的基于数据符号方法,它的优点是捕获快、精度高,适合分组数据通信,具体的实现是在分组数据包的包头加一个专门用来做定时、频偏的OFDM块。基于数据符号的算法又可以分为两类:基于训练符号(导频码)的方法和基于循环前缀(CP)的方法。其中基于循环前缀的方法是在OFDM符号中插入保护间隔,保护间隔取符号尾部最后若干个样点的复制,当其中的任何一个位于保护间隔内时,另-个与它相同,两者的相关性较强;当不在保护间隔内时,这两个样点是独立的。利用保护间隔的这些特性可以完成OFDM系统中符号定时偏差和载波频偏估计。

基于循环前缀的同步算法

本文要讨论的基于ML(最大似然估计)时频同步算法是vande Beek等人提出来的,这是一个利用CP所携带的信息完成定时同步和载波同步的最大似然估计算法。它利用OFDM系统循环冗佘扩展的循环前缀携带的信息进行同步估计,避免了基于导频码的同步估计带来的频率和功率资源的浪费。

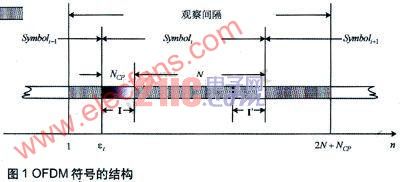

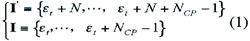

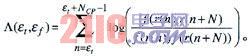

如图1所示,假设观察接收信号r(n)的连续2N+NCP个样值。在这些样值中必然包含了一个长为N+NCP的OFDM符号。由于无法知道符号的开始位置,只能将其设为变量。定义两个索引集合(Indexsets):

其中,I表示的是OFDM符号最后NCP个样值,I′表示的是循环前缀的样值。将观察区间内的2N+NCP个样值作为一个集合,可表示为:

由于循环前缀是OFDM符号后一段的复制,所以集合和集合中的元素是相同的。

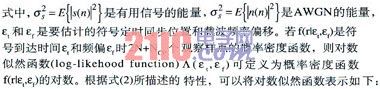

式(4)中同时使用了一维和二维概率密度函数。其中乘积项![]() 是对所有2N+NCP点求乘积,所以与符号起点εt兀关,如果假设信息是独立同分布的,即r(n)的实部和虚部是互相独立的,则

是对所有2N+NCP点求乘积,所以与符号起点εt兀关,如果假设信息是独立同分布的,即r(n)的实部和虚部是互相独立的,则![]() 也与εf无关,所以可以忽略

也与εf无关,所以可以忽略![]() 。据此式(4)可以被化简为:

。据此式(4)可以被化简为:

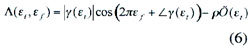

根据集合I的范围,式(5)也可以写作:

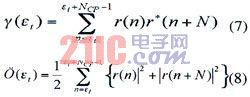

通过一系列代数运算之后,可被简化为:

其中∠表示取复数的角度,且:

r(n)和r(n+N)的相关系数的幅度用ρ表示。

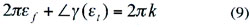

对于频偏εf而言,要使式(6)最大,即使余弦项达到最大值1,即:

其中k为整数。由于余弦函数有周期性,所以根据k的不同会得到很多个最大值。如果考虑|εf|<0.5,则k=0。这样就得到εf的极大似然估计值:

![]()

要估计出频偏就必须对符号精确定时。由此继续简化可得到:

![]()

由于式(11)只与时偏有关,所以可以得到的极大似然估计值为:

![]()

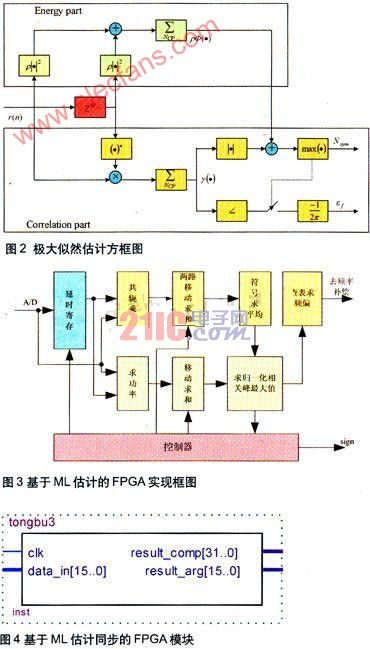

图2显示了极大似然估计算法的方框图。它增加了能量部分,能量部分是通过极大似然准则推导出来的,能量部分的引入弥补了单纯利用循环前缀相关性算法的缺点,使得定时更准确。

算法的FPGA实现 图3所示是同步算法FPGA实现框图,设计采用512抽样点,最大保护间隔按照NCP=512×1/4=128计算。工作过程大致如下:

512位复数数据通过写地址存储到延时寄存器,存满以后通过读地址读出前128位复数,同时和后面的直接输入128位数据送到后级模块,两路数据分别做共轭乘。延时寄存器模块可用一个512×16的双端口 RAM,RAM的读写地址分别为128位计数器和512位计数器。共轭乘后的复数数据流送给两路移动求和模块,求功率后的值送给一路移动求和模块。控制器对累加器清零,同时控制RAM的读写和使能信号的产生。累加器采用16位二进制数累加,两路16位的数据移动求和之后去求符号平均,然后再和另一路移动求和的结果运算归一化,求相关峰最人值,若出现相关峰的最大值,就表明同步的到来,这时标记该数据的地址,然后让控制器发出标志位置高指令,通知从该数据开始就可以进行FFT解调处理。如果没有相关峰最大值的出现,系统再循环读出后128位地址数据,重复前面的运算,直到找到最大相关峰。

在求归一化相关峰最大位置模块中,先求出平均移动和的实虚部绝对值之和,再除以功率,得归一化相关值。南于归一化值为小数,故需给结果乘以一因子,这里取2。由于ML同步脉冲是在最大值后持续ML窗宽时间输出,这期间最大值对应的相关和实、虚部保持不变,故求频偏模块可顺序计算,只须用ML同步脉冲将求频偏模块输出的频偏锁定输出。

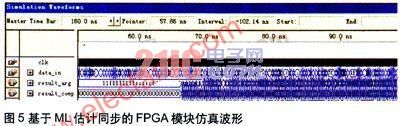

经过QuartusII 5.0工具的设计、编译、综合等一系列步骤,基于PN序列同步系统融合成一个整体模块,如图4所示。仿真结果如图5所示。

结语

上述FPGA实现的是基于数据符号的OFDM系统同步算法,采用Altera公司的芯片EPlS25102015进行试验仿真,该芯片有25660个逻辑单元,1944576个存储模块单元,80个DSP模块单元,707个I/O输出引脚。

基于循环前缀的同步算法占用芯片资源适中,但是占用了27%的芯片I/O引脚,另外,时钟频率也较低,设计电路较难,但是它达到更高的同步精度还要结合其他同步方式,它也可以应用于无线信道通信中。综合算法设计占用芯片资源以及相关情况的分析,算法在FPGA中的实现是可行且可靠的,充分发挥了FPGA芯片集成密度大、速度快、功耗低、通用性好、适应性强和重复编程的特点。通常,可编程逻辑芯片都能提供人容量的逻辑和存储单元,因此,芯片预留资源都是有富余的,信号处理的实时性和可靠性是关注的重点,当然成本也是考虑的一个因素,与此同时,也要考虑电路的设计复杂程度,因为它会影响数据处理的速度。