概览

多功能智能DAQ设备配有自定义式板载处理功能,最大限度地为系统定时及触发提供灵活性能。 与控制设备功能的固定ASIC不同,智能DAQ采用基于FPGA的系统定时控制器,令所有模拟和数字I/O能够根据特定应用操作接受相应的配置。 本指南展示了:如何使用R系列智能DAQ板卡和NILabVIEW FPGA,灵活自如地执行数据采集任务

入门

NI LabVIEW FPGA模块帮助DAQ系统的开发者灵活自如地进行应用程序编程以实现各类输入/输出操作。 用户无需预先了解VHDL等硬件设计工具,便可将LabVIEW代码嵌入FPGA芯片并获得硬件定时的速度和可靠性。

让我们先从数据采集硬件的常用组件切入论题。 假设您拥有了模数转换器(ADC)、数模转换器(DAC)和数字输入/输出线,则所有I/O便要根据实际操作接受某种方式的定时和控制。 典型的多功能数据采集设备采用功能齐全的ASIC,满足了大多数的功能性需求。

比如:M系列DAQ设备通过DAQ-STC2,控制着各类硬件组件的定时和触发。 智能DAQ硬件(如:R系列DAQ设备)区别于市面上的其他任何数据采集设备,因为在控制设备功能方面智能DAQ用基于FPGA的系统定时控制器取代了传统ASIC,从而使得所有模拟和数字I/O都能根据特定应用操作接受相应的配置。 可重配置FPGA芯片通过NI LabVIEW FPGA模块进行编程,此时NI LabVIEW的数据流模式仍旧适用,不过采用了一组新函数控制最底层的设备I/O。

LabVIEW FPGA I/O节点并不通过NI-DAQmx函数负责实现常见的任务和功能,而是灵活自如地在各个通道最底层上运行。 通过以下各部分的内容,我们将了解NI-DAQmx的特定实例,并学习如何通过智能DAQ定制各类数据采集任务。

定时和触发

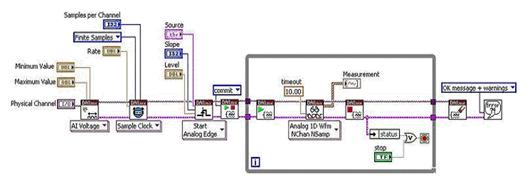

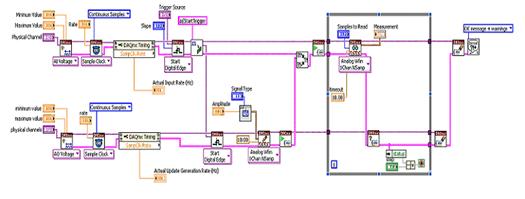

实现高级数据采集的智能DAQ主要用于定制定时和触发。 下方的范例程序框图展现了:NI-DAQmx帮助实现的触发式模拟输入任务。

图1. 通过NI-DAQmx实现的触发式模拟输入

如图1所示,智能DAQ并未使用不同函数配置通道,而是通过名为I/O节点的函数读写各路模拟和数字通道。 让我们看看使用NI LabVIEW FPGA中I/O节点所获得的相同功能。

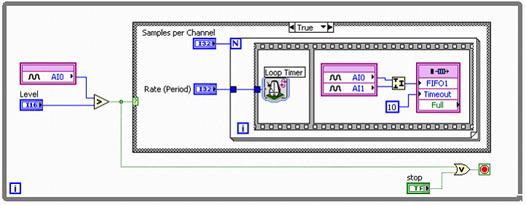

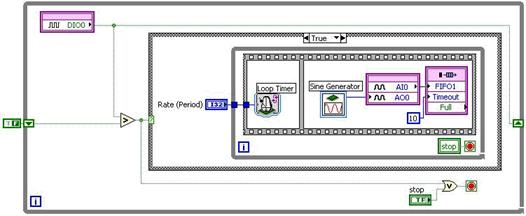

图2. 通过智能DAQ和NI LabVIEW FPGA实现的触发式模拟输入

上图既没有针对全局通道、采样时钟、触发的配置函数,也没有开始、停止和清除等任务。 所有内容都被1个简单的模拟I/O读取所取代;全部定时都为本地LabVIEW结构(如:While循环和条件结构)所控制。由于整个程序框图均在FPGA硬件内执行,LabVIEW代码的运行便体现出硬件定时的速度和可靠性。

让我们更深入地了解一下该程序框图的运行方式。 模拟I/O节点并不指定某个采样速率,而使用For循环采集各个样本。 与之对应的ADC在I/O节点被调用时,负责对输入信号进行实际数字化,因而通过For循环接受定时。 若想在100 kHz的频率下进行信号采样,针对循环的延迟就必须设定为10 µs。 循环的定时器函数从第2轮循环迭代开始便确保着特定的时间延迟,用户因而能够通过顺序结构保证样本之间存在着指定的时间间隔。 NI LabVIEW FPGA中功能强大的条件结构,实际代表了用于封装各类代码的硬件触发。 由于所有的函数和结构都通过逻辑单元在硬件内运行,所以条件结构确保开始具有实时10 µs时间精度的采样。 最后需指出的是,由于操作位于硬件层,只涉及几个层次的抽象处理,因此用户无需清除任务ID或释放内存。

就基于FPGA的智能DAQ硬件而言,其真正的优势是能够定制各类定时和触发,并在硬件中进行信号处理和决策。 现在让我们了解一下:针对某类自定义应用,需对模拟输入触发做出哪些修改。 若我们希望在2路模拟输入通道的某路电压超过指定范围时便触发采集,又该如何修改呢? 借助NI LabVIEW FPGA,此类任务的执行易如反掌。

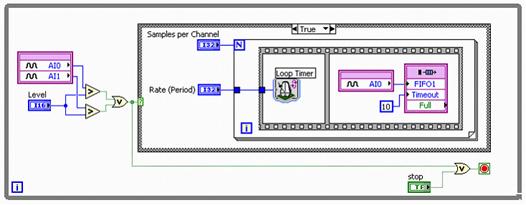

图 3. 通过智能DAQ和NI LabVIEW FPGA实现的自定义触发式模拟输入

这里,我们已经为程序框图添加了第2个I/O节点和第2个比较函数,以及1个布尔“或”函数。 智能DAQ硬件为所有的模拟输入通道提供专用ADC,因而2路通道能够接受同步采样;同时,只要任何1路通道的电压超过了指定范围,条件结构便会执行“真”条件,并开始以10 µs时间精度进行采样。 请记住:缺少智能DAQ便不可能生成类似的触发;在其他DAQ硬件上应用时,触发需要具有更高延迟的软件定时来实现。 如果此后我们希望通过扩展将监控范围从2路通道延伸至全部8路通道,甚至希望添加数字触发,就需要简化自定义代码。 添加预触发扫描后,用户便可对输入通道不断进行采样并将数据传送至FIFO缓冲器。 触发器一旦接受读取,FIFO缓冲器和此后的采样便可经由DMA通道,被传送至主机。

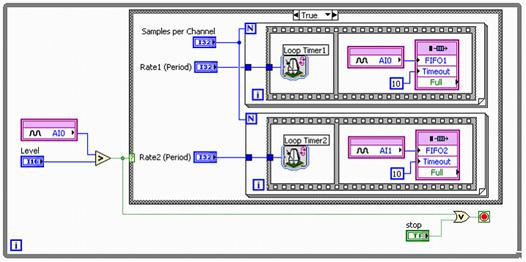

如果我们希望借助NI-DAQmx驱动,对第2模拟输入通道进行采样,则该程序框图与图1所示的内容相差无几。然而限制依然存在,因为2路通道均被迫引用相同的触发器并以相同的时钟频率进行采样。 现在我们来看看:智能DAQ和NI LabVIEW FPGA帮助实现的各类多通道采样。

图4(上图)展现了:如何基于模拟输入通道0中的模拟触发器,对2路不同的模拟输入通道进行同步采样。由于智能DAQ设备均配有独立的ADC,在同一I/O节点中的2路通道可在完全相同的时刻接受采样。 典型的多功能DAQ设备可通过一个ADC多路复用所有通道,因此,各路通道必须共享相同的采样时钟和触发线。 图5(下图)展现了:智能DAQ硬件其实能够以独立的速率,对不同的模拟输入通道进行采样。 在独立回路中放置模拟输入I/O节点后,每路通道会以完全不同的速率进行采样,然后各自通过2条DMA通道读写硬盘。

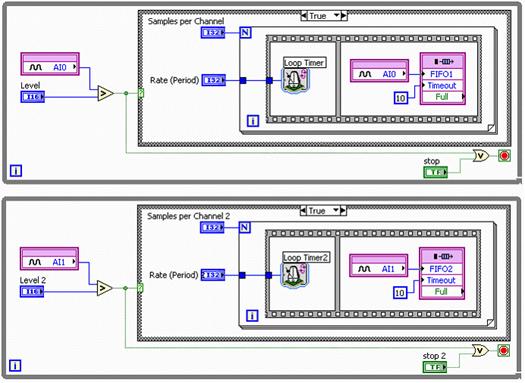

最后需指出的是,我们若是希望2路通道具有相互独立的采样率和开始触发,则可参照图6,将所有I/O节点都部署在并行循环结构中。该方式充分利用了FPGA的并行性,确保了各项任务能够使用专用资源并在执行时完全独立于其他采集任务。

图6. 通过智能DAQ实现的独立触发式多速率模拟输入

同步

DAQmx驱动程序提供多种同步选择,帮助建立输入和输出的时间相关性。 在下方的程序框图中,模拟输入通道和模拟输出通道借助数字触发实现同步;过程中,需对模拟输入指定数字触发,并使用模拟输入的触发器信号触发产生模拟输出。

图7. 通过NI-DAQmx实现的同步模拟输入和输出

用户可通过智能DAQ硬件轻而易举地执行同步任务,而无需借助任务ID和板载信号路由。 本处即显示了NI LabVIEW FPGA中的内容。

此处,我们再次通过条件结构在FPGA芯片上执行硬件触发,而数字通道0上的上升沿则启用了真条件中的代码。 在顺序结构中,模拟输入与输出的节点在同时接受调用的过程中,几乎没有任何抖动;而我们只要简单地在各个独立的While循环内嵌入模拟I/O节点,即可令其拥有独立的采样速率。 另外值得注意的是: 程序框图中显示的正弦发生器函数是1个Express VI,可帮助用户在查找表(LUT)中交互式地配置正弦值。

图8中的智能DAQ程序框图与图7中的DAQmx VI皆具有相同的功能,而唯有智能DAQ才能为自定义任务提供相应的灵活性。 举例为证:如需添加1个暂停触发,我们只消在内部While循环中添加1个条件结构,并通过另一个数字I/O节点选择真条件或假条件,即可轻松完成任务。 对硬件进行编程的强大功能,实现了各类I/O的定时与同步。

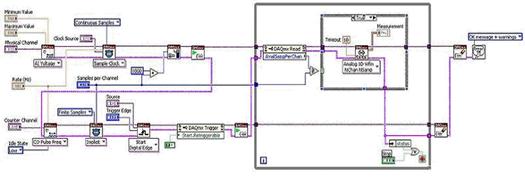

多功能同步的另一例证体现为:通过板载计数器产生有限脉冲并将计数器输出用作模拟输入的采样时钟。 该过程是进行可重触发式有限采样的常用手段。 下图显示了开展此类采集所必需的DAQmx代码。

图9. 通过NI-DAQmx实现的可重触发式有限模拟输入

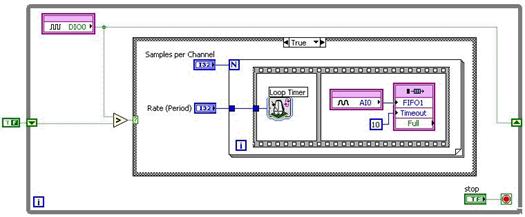

现在,让我们对下图内容和呈现相同功能的NI LabVIEW FPGA程序框图,加以比较。

图10. 通过智能DAQ和NI LabVIEW FPGA实现的可重触发式有限模拟输入

由于NI LabVIEW代码在硬件层运行,图10中的驱动配置步骤显然得到了极大精减。 我们已经借助简单的数字输入线和For循环结构,创建了硬件可重触发式有限采集。 图9中的程序框图使用2个板载计数器,创建出可重触发的有限脉冲序列;典型的多功能DAQ设备只有2个计数器。 而借助NI LabVIEW FPGA,智能DAQ硬件却能够将任意一条数字线配置成计数器。 我们将在之后的段落里,涉及更多“通过智能DAQ运行计数器/定时器”的内容。

我们能够借助由频率触发的采集,进一步地推进智能DAQ在硬件定时方面的灵活性特性。 用户可通过高速板载决策计算输入信号的频率,而后选择条件结构中所需的代码;这一点是使用典型多功能DAQ设备所无法企及的。 在多设备的同步进程中,智能DAQ还可提供用于PCI板卡的RTSI总线或是用于PXI模块的PXI触发总线。 这些外部定时和同步线还可通过程序框图上的I/O节点接受访问。

模拟波形的生成

不少多功能DAQ设备都配有模拟输出通道,能够为了生成连续的模拟波形而需要用到FIFO缓冲。 生成的波形可将FIFO用作循环缓冲区,且无需从主机处接受任何更新数据,即可连续不断地重新生成一系列的模拟值。 通信总线的有无对此影响不大,因为并没有针对设备的频繁数据读写。 而如果波形需要修改,就必须重新启动输出任务并向FIFO写入新数据。 另一个办法是向硬件FIFO设备连续读写数据,而这又会导致输出任务出现时滞。借助智能DAQ,用户能够将波形输出结果存储于硬件,甚至能够通过硬件触发改变波形,进而创建任意波形发生器。

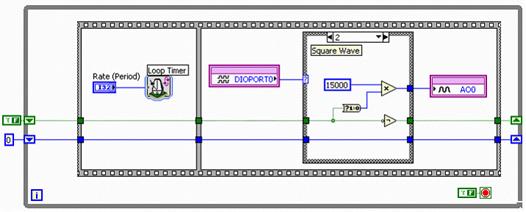

下方的函数发生器范例通过数字输入线,触发了输出波形中的改动。 通过组合数字I/O线0与1,我们取得了应用于模拟输出的4种不同状态或称条件。

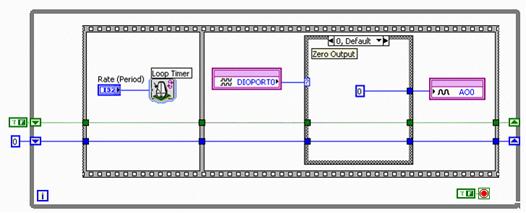

图11a. 配有智能DAQ条件0的函数发生器 – 零输出

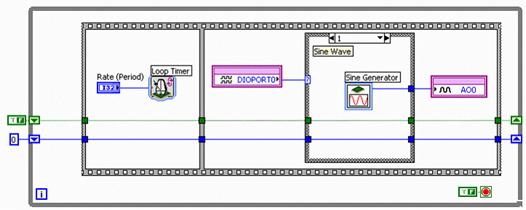

图11b. 配有智能DAQ条件1的函数发生器 – 正弦波

当两线皆呈现低电平时,执行条件0;如图11a所示,输出值为0 V常量。而当DIO线0呈现高电平而DIO线1呈现低电平时,条件1将在模拟输出0上执行并生成一个正弦波。用户可通过该正弦生成结构(图11b)中的正弦发生器Express VI,配置NI LabVIEW FPGA必需的参数,交互地配置正弦波。

条件2(图11c)能够在While循环的每轮迭代中,轻松切换布尔值。 数值较低时,整数15000便被写入模拟输出AO0,以对应16位DAC内由输出寄存器存放的数值:15000。 16位有符号整数可以包含-32768到32767之间的数值。当输出电压范围介于-10 V和10 V时,向模拟输出AO0写入-32768会生成-10 V电压,而写入32767则生成10 V电压。该例中,因我们的写入值为15000,则生成的电压将低于5 V。(数学公式为: 15000/32767 * 10 V = 4.5778 V) 通常,条件2会输出一个在0 V和4.578 V之间变换的方波。

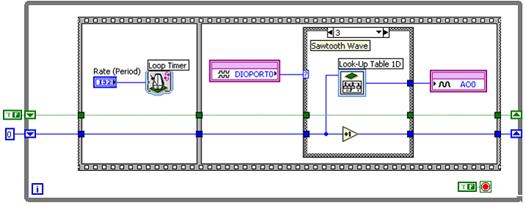

当DIO 0和DIO 1均呈现高电平时,便执行最后一个条件(图11d);其间,须借助查找表(LUT)连续生成一个锯齿波。 作为另一类Express VI的查表VI,既能存储任意波形值,也能通过编程建立波形值的索引。 该例中,接受配置的锯齿波可在模拟输出通道0上生成。

通过将所有的值都存储在FPGA上,用户在降低总线依赖性的同时,也确保了波形更新时硬件定时的速度和可靠性。 之前各部分中所描述的模拟输入的触发和同步灵活性同样适用于模拟输出;借助智能DAQ,用户能够以不同速率,完全独立地更新各路模拟输出通道。 这意味着:用户可在不影响其他通道输出结果的前提下,修改单个周期性波形的频率。 请注意:大多数数据采集硬件均不具备此项功能。

计数器/定时器的操作

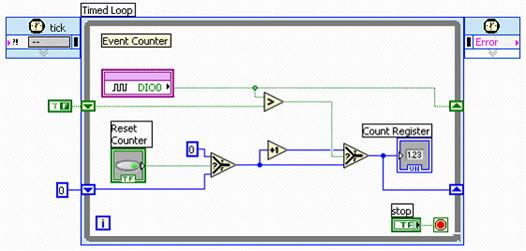

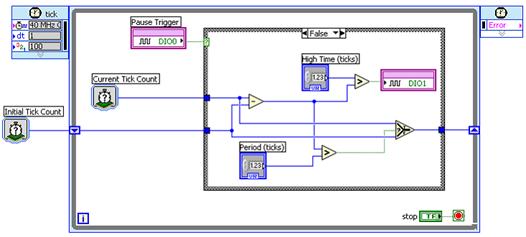

如前所述,典型的多功能DAQ设备只有2个板载计数器,而智能DAQ则能在各条数字线上运行计数器功能。 数字I/O节点能够在NI LabVIEW FPGA中利用名为单周期定时循环的专业结构,帮助用户在2.5 MHz至200 MHz的特定频率范围内执行代码。 例如,借助40 MHz的时钟,用户可使用单周期定时循环,在各条数字线上创建40 MHz计数器。 图12(下图)展现了程序框图的样式。

由于计算值基于U32(32位整数)的数据类型被发送至显示控件,该代码便在FPGA芯片上生成了1个40 MHz的32位计数器。 用户可对其进行数次复制与粘贴,令不同数字线上的多个计数器都能够彼此完全并行地运行。 通过对智能DAQ中参数的设置可以实现定时器操作的自定义。 通过选择,用户能够每隔2个上升沿便进行1次计数器递增,甚至能基于计数寄存器的值触发模拟采集。 许多复杂的计数器操作(如:有限脉冲序列生成和级联式事件计数)均需要使用2个计数器,这意味着使用典型多功能设备中的所有板载计数器。 在总共160条数字线的帮助下,智能DAQ硬件上定时器的最大数量很少受到I/O可用性的影响,而往往取决于FPGA芯片的大小。 由于NI LabVIEW代码运行于硅芯片中,因而用户无需“装备”或“重新装备”通用计数器,即能全面控制计数器的运行。

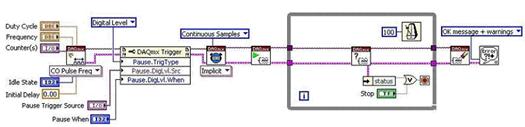

图13(下图)中的范例使用计数器,生成了一个连续脉冲序列并将暂停触发器置于NI-DAQmx中。

图13. 连续脉冲序列的生成和配有NI-DAQmx的暂停触发器

在NI LabVIEW FPGA中,暂停触发器无需接受配置,因为只需简单的条件结构便能在硅芯片中实现相同的功能。 此处是通过智能DAQ运行时所展现的相同功能(图14)。

在这种情况下,数字I/O线DIO0用作暂停触发,而脉冲将在数字I/O线DIO1上生成并输出。使用单周期定时循环可令各个脉冲获得25 ns的分辨率,因为这将成为单个计时在使用40 MHz定时源时的值。

数字I/O应用

智能DAQ硬件提供多达160条硬件定时数字线,令诸多数字应用成为可能。 我们已经学习了如何使用数字I/O实现触发、同步及计数器/定时器的运行,而智能DAQ还可用于误码率测试、数字模式匹配、脉冲宽度调制、正交编码器和数字通信协议。 自定义或标准形式的串行接口均能直接通过数字定时框图编程来实现。 举例说明,SPI便是一款与硬件组件(如:微控制器或ADC)进行通信时最常用的串口协议。 图15(下图)展现了在进行16位SPI通信时,3条必要数字线所对应的定时框图。

图15. SPI通信输入定时框图

如定时框图所示,所有16位数据均在每个时钟周期上顺次传递,而片选控制线(chip select line)则呈现低电平。 现在,我们来看看在NI LabVIEW FPGA中,如何通过智能DAQ硬件上的3条数字线进行此类编程。

图16中,外部While循环确保了所有代码均能连续执行,而写入布尔输入控件则通过条件结构启动着数据传递。 顺序结构中的第一框架将片选控制线(chip select line)设置为低电平,之后由中间框架写入数据位并将时钟线切换16次。 最终,第三顺序框将片选控制线(chip select line)设置回TRUE状态,并将数据线重置为默认的FALSE状态。 这一简单范例只是借助智能DAQ进行数字通信时的一项内容。 用户若想应用数字握手,便需为ACK(备用)和REQ(暂停)线准备2路通道,其中一路通道面向并行运作的时钟信号和数据线。

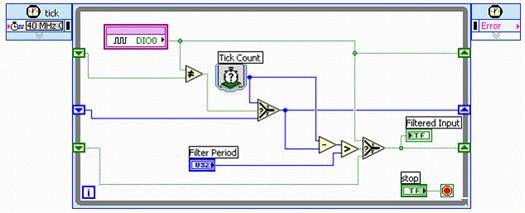

数字线会时常抖动,在使用机电接触时更是如此,然而用户可通过NI LabVIEW FPGA,选择不同方式,在数字输入线上添加去抖动滤波器。 在消除状态的错误改动时,数字去抖动滤波器确保数值的变化能够保持一段最短的时间,因而规避了因抖动引发的错误读取。 图17展现了如何通过智能DAQ实现此项功能的内容。

图17. 智能DAQ硬件上的数字滤波器程序框图

数据传输方式

配备NI-DAQmx驱动程序的传统多功能DAQ和智能DAQ之间的最大差异在于:数据传输的执行方式。 NI-DAQmx驱动程序将承担由设备至主机的各项传输任务,此项操作中NI LabVIWE FPGA会对基于FPGA的所有板载硬件进行编程。 用户可通过多种途径缓冲设备上的板载数据,并使用不同方式(如:DMA通道或中断请求)传输数据。

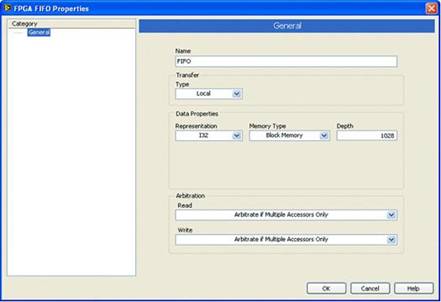

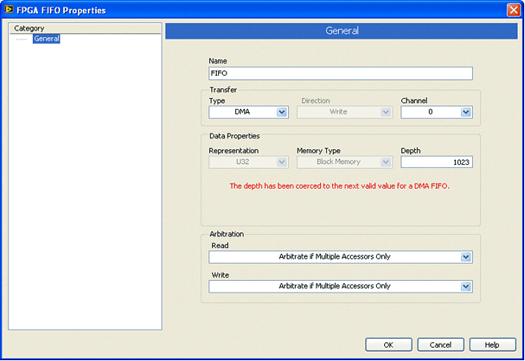

NI LabVIEW FPGA中的FIFO缓冲区在LabVIEW项目浏览器中接受配置,并能借助板载内存或硬件逻辑获得运行。 图18显示了如何经由项目浏览器,在板载块存储器中配置整数的FIFO缓冲区。

图18. NI LabVIEW FPGA中的FIFO配置

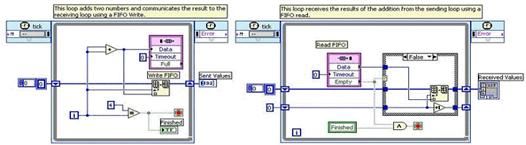

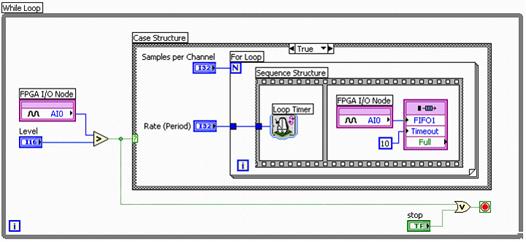

FIFO一经创建,便能用于NI LabVIEW FPGA程序框图上多个循环之间的数据传递。 图19中的范例显示:数据先被写入左侧循环中的FIFO,并随即从右侧循环中的FIFO被读出。

图19. 通过FIFO和多循环实现的NI LabVIEW FPGA程序框图

同样通过LabVIEW FPGA FIFO获得应用的直接存储器访问(DMA)通道,在项目浏览器中接受了类似的配置。

图20. NI LabVIEW FPGA中的DMA FIFO配置

图21. 通过DMA FIFO和位组装实现的NI LabVIEW FPGA程序框图

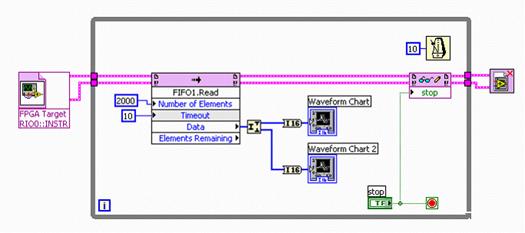

所有的DMA FIFO数据传输宽度均为32位;因此,当其传递源自16位模拟输入通道的数据时,往往能够合并2路通道或2个样本上的数据再进行传输,从而提高带宽使用率。 这即是图21所展现的位组装。当数据被直接传递到主控计算机的内存后,便可通过在Windows环境下运行的NI LabVIEW主接口函数接受读取(图22)。

图22. 通过DMA FIFO读取和位拆装实现的主接口代码

如图22所示,主接口程序框图引用FPGA终端VI,然后使用While循环连续读取DMA FIFO。 32位的数据被分解为2路16位通道,在波形图表上接受采样和绘制。 主接口VI还能对FPGA VI前面板上的各类显示控件和输入控件进行读写操作;在这种情况下,“停止按钮”输入控件也被写入。

结论

尽管DAQ-STC2等固定ASIC能够满足数据采集的大多数需求,然而,唯有借助智能DAQ中基于可重新配置FPGA的I/O定时和控制,方能实现高度灵活性和完全定制。 借助NI LabVIEW FPGA,触发和同步任务获得了简化,因为通过绘制图形化程序框图即可充分满足用户需求;借助独立的模拟和数字I/O线,智能DAQ可利用FPGA提供的实际并行。 R系列智能DAQ设备已经针对多速率采样、自定义计数器操作和频率高达40 MHz的板载决策,为多功能数据采集进行了各项可能的修缮。