基于FPGA的PCI总线接口硬件调试策略

西安电子科技大学 陈重

摘要:Signal TapⅡ逻辑分析器集成到QuartusⅡ设计软件中,能够捕获和显示可编程单芯片系统(SOPC)设计中的实时信号状态,这样,开发者就可以在整个设计过程中以系统级速度观察硬件和软件的交互。Signal TapⅡ可支持多达1024个通道,采样深度高达128KB,每个分析器均有1O级触发输入/输出,从而增加了采样的精度。

Abstract:

Key words :

在FPGA的设计流程中,完成设计输入以及成功综合、布局布线,只能说明设计符合一定的语法规范,而并不能保证其满足设计人员对功能的要求,因而需要通过仿真对设计进行验证。仿真验证的目的是为了发现设计的问题,而一旦发现,就需要千方百计地通过调试找到问题所在,这其实也是设计中比较困难的。

随着FPGA可编程器件容量的不断增大和设计复杂度的日益提高,功能调试已经成为一个很繁重的任务。为了使设计的产品尽快投入市场,设计人员需要一种简易有效的测试工具,以尽可能缩短测试时间,提高测试效率。传统的逻辑分析仪在测试复杂的FPGA设计时,会面临以下几点问题:

(1) I/O引脚有限。设计中器件的选择依据设计规模而定,通常所选器件的I/O引脚数目和设计的需求是恰好匹配的;

(2) I/O引脚难以引出。设计者为减小电路板的面积,大都采用细间距工艺技术,这在不改变PCB板布线的情况下引出I/O引脚非常困难;

(3)外接逻辑分析器有可能改变FPGA设计中信号的原来状态,因此,很难保证待测信号的正确性;

(4)传统的逻辑分析器价格昂贵,会增加设计成本。

1Signal Tap硬件调试原理

为了尽快使设计的产品投入市场,就要尽可能地缩短设计验证所耗费的时间。为此,

Altera公司推出了一种新的调试工具。这种型号的Sig-nal TapⅡ的逻辑分析器具有无干扰、便于升级、使用简单、价格低廉等优点,可满足FPGA开发中硬件调试的要求。

Signal TapⅡ逻辑分析器集成到QuartusⅡ设计软件中,能够捕获和显示可编程单芯片系统(

SOPC)设计中的实时信号状态,这样,开发者就可以在整个设计过程中以系统级速度观察硬件和软件的交互。Signal TapⅡ可支持多达1024个通道,采样深度高达128KB,每个分析器均有1O级触发输入/输出,从而增加了采样的精度。可以说,Signal TapⅡ为设计者提供了业界领先的SOPC设计的实时可视性,它能够大大减少验证过程中所花费的时间。目前,SignalTapⅡ逻辑分析器可以支持的器件系列包括:APEXT II,APEX20KE,APEX20KC,APEX20K,Cyclone,Ex-calibur,Mercury,Stratix GX,Stratix等。Signal TapⅡ将逻辑分析模块嵌入到FPGA中,图1所示是Signal TapⅡ的嵌入式逻辑分析器结构框图。图中,逻辑分析模块可对待测节点数据进行捕获。并将数据通过JTAG接口从FPGA传送到QuartusⅡ中显示。使用Signal TapⅡ无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件,Signal TapⅡ在对FPGA的引脚和内部的连线信号进行捕获后,便可将数据存储在FPGA的RAM块中。因此,需要为采样信号、触发信号和待测信号预留一定数目的RAM块。

2 使用Signal Tap的一般流程

图2所示是Signal TapⅡ的调试流程示意图。使用Signal TapⅡ的一般流程,是在完成设计并编译工程后,建立Signal TapⅡ(.stp)文件并加入工程,然后再配置STP文件,并将其编译并下载设计到FPGA中,接着在QuartusⅡ软件中显示被测信号的波形,并在测试完毕后将该逻辑分析器从项目中删除。

其Signal TapⅡ文件设置和采集信号数据的基本流程如下:

(1)建立新的Signal TapⅡ文件;

(2)设置采样时钟。采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则将无法正确反映被测信号波形的变化。Signal TapⅡ通常在时钟上升沿将被测信号存储到缓存。

(3)设置被测信号。可以使用Node Finder中的SignalI TapⅡ滤波器查找所有预综合和布局布线后的Signal TapⅡ节点,添加要观察的信号。逻辑分析器不可测试的信号包括:逻辑单元的进位信号、PLL的时钟输出、JTAG引脚信号、LVDS(低压差分)信号等。

(4)配置采样深度,确定RAM的大小。Signal TapⅡ所能显示的被测信号波形的时间长度为TX,其计算公式如下:

TX=NTS

式中,N为缓存中存储的采样点数,TS为采样时钟的周期;

(5)设置buffer acquisition mode。buffer ac-quisition mode包括循环采样存储和连续存储两种模式。循环采样存储也就是分段存储,即将整个缓存分成多个片段(segment),每当触发条件满足时就捕获一段数据。该功能可以去掉无关的数据,使采样缓存的使用更加灵活;

(6)触发级别。Signal TapⅡ支持多触发级的触发方式,最多可支持1O级触发,设计人员可以只查看最重要的数据。

(7)触发条件。Signal TapⅡ逻辑分析器可支持多个触发位置以及外部触发事件,可以使用Signal TapⅡ逻辑分析器窗口中的Signal Configu-ration面板来设置触发器选项,也可以设定复杂的触发条件来捕获相应的数据,以协助调试设计。当触发条件满足时,可在Signal Tap时钟的上升沿采样被测信号。

3 使用Signal Tap调试PCI主设备控制器

Signal TapⅡ逻辑分析器的使用大大加快了PCI主设备控制器的调试进程,例如在调试DMA传输后的中断产生时,由于软件检测不到中断而导致DMA传输结束后,可能会使计算机死机而不能正常结束(完整的流程是:DMA传输结束,产生中断,并在软件检测到中断后进人中断服务程序来处理中断,然后清除)。

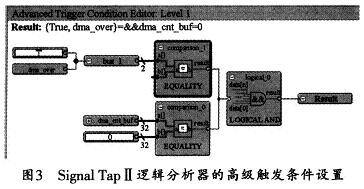

对中断产生的条件进行检查时,32位的DMA计数器必须为0,而且DMA传输结束标志信号必须有效,针对这一条件,使用普通的示波器和逻辑分析器根本无法跟踪到,但是使用SignalTapⅡ逻辑分析器的高级设置,就可将这两个条件作为触发条件,从而检测到中断是否产生,其高级设置如图3所示。

4 结束语

与传统逻辑分析器相比,使用Signal TapⅡ逻辑分析器有以下优势:

(1)不占用额外的I/O资源。若使用传统的逻辑分析仪观察信号波形,则必须将待观察信号引到空闲管脚,这样,在器件管脚紧张的时候,Signal TapⅡ逻辑分析器的优点就可以得到充分地体现。

(2)不占用PCB空间。若使用传统逻辑分析仪,则需要从FPGA器件上引出测试管脚到PCB上,这样会增加PCB走线难度;

(3)不破坏信号的完整性;

(4)传统逻辑分析仪价格昂贵,而将Signal TapⅡ逻辑分析器集成在QuartusⅡ软件中,无需另外付费;

因此,可以预见,Signal TapⅡ逻辑分析器将受到越来越多的设计工程师的青睐。

来源:电子元器件应用

此内容为AET网站原创,未经授权禁止转载。