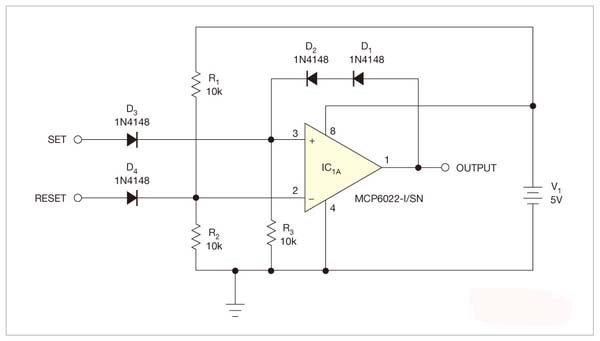

用两个NAND或NOR门,可以做出一个置位/复位触发器,或者也可以使用现成的置位/复位触发IC,如74HC279四置位/复位锁存器。这些方法的缺点是,它们需要占用大量的空间来组成触发器。即使你只需要一只触发器,也必须在方案中使用一只大IC封装。不过,如果你有一只空闲的轨至轨运放,也能完成所需要的锁存功能(图1)。

这种方案对空间的需求低,因为轨至轨输入/输出的MCP6022是双运放封装,这意味着可以用少量空间做出两个置位/复位锁存电路。如有必要,通过选择适当的运放,还可以在非标准电源电压下运行该电路。

图1,当为置位或复位输入端施加一个正向脉冲时,正反馈与二极管控制着运放输出高或低的锁存。

用R1/R2分压器将运放的反相输入设为2.5V。由于D4被反偏,该输入端不能拉到低于2.5V。但可以将输入端驱动至逻辑高。串联二极管D1和D2为运放的非反相输入端加正反馈, 如果输出和置位输入均为低,则R3拉低。

输出为低时,置位输入加一个5V脉冲,正偏D3;D1和D2保持反偏。运放非反相输入端获得的4.4V将输出驱动为高,正偏D1和D2 ,将非反相输入端锁存在3.8V,此电压远高于反相输入端的电压,即使置位输入端返回了低。接下来,如果将复位输入端驱动为高,则反相输入(为4.4V)就高于非反相输入端的3.8V,使输出为低。当复位输入回到低时,D4反偏,反相输入端的2.5V使输出保持为低。注意,输入脉冲必须有足够的持续时间,以适应运放的延迟与转换速率。

与真正的置位/复位锁存不同的是,两个输入端同时为高电平会得到未知的结果。这种情况下,可以在置位输入或复位输入处串联一只电阻,引入少许的电压差,从而确保需要的逻辑状态。CMOS逻辑是轨至轨驱动,可以直接与本电路接口。而用TTL作驱动则需要在TTL输出端加上拉电阻,以确保有足够的输入电压。可能需要增加10kΩ电阻的值,以避免上拉电阻作负载。

所选运放必须有轨至轨的输出能力。使用无此功能的运放也可以,但要根据需要增加电源电压,针对所需逻辑电平补偿输出电压。通过调节R1和R2以及采用低压降二极管(如锗管或肖特基管)可以改变触发器的电平。

本电路有相对较低的输入阻抗,但一般不会有问题,因为大多数逻辑输出信号都可以驱动此负载。根据需要调节电阻值,就可以改变输入阻抗。