长时间以来,多芯片封装(MCP)满足了在越来越小的空间里加入更多性能和特性的需求。很自然地就会希望存储器的MCP能够扩展到包含如基带或多媒体处理器等ASIC。但这实现起来会遇到困难,即高昂的开发成本以及拥有/减小成本。如何解决这些问题呢?层叠封装(PoP)的概念逐渐被业界广泛接受。

从MCP到PoP的发展道路

在单个封装内整合了多个Flash NOR、NAND和RAM的Combo(Flash+RAM)存储器产品被广泛用于移动电话应用。这些单封装解决方案包括多芯片封装(MCP)、系统级封装(SiP)和多芯片模块(MCM)。

刚开始时移动电话中的MCP整合的芯片,比如8Mb的Flash和2Mb的SRAM,以现在的眼光来看密度较低。随着移动电话对存储器要求的提高,闪存的密度也随着NOR Flash的增多和NAND Flash的引入而增加,SRAM也被PSRAM所取代。

在体积越来越小的移动电话中提供更多功能的需求是MCP发展的主要驱动力。然而,开发既能增强性能又要保持小型尺寸的解决方案面临着艰巨的挑战。不仅尺寸是个问题,性能也存在问题,如当要与移动电话中的基带芯片组或多媒体协处理器配合工作时,要使用具有SDRAM接口和DDR接口的MCP存储器。

SoC SoC的基本概念是在同一片裸片上集成更多的器件,以达到减少体积、增强性能和降低成本的目的。但在项目生命周期非常短、成本要求非常苛刻的移动电话市场,SoC解决方案有很大的局限性。从存储器配置的角度看,不同类型的存储器需要大量逻辑,掌握不同的设计规则和技术是非常大的挑战,会影响开发时间和应用所要求的灵活性。

SiP 从裸片角度看,保持基本组件的独立并用不同技术进行制造可以解决上述问题。存储器和ASIC可以组装在同一封装中。但有两个主要问题需要考虑。

1. SiP生产成本与良品率的关系

在开发任何配置的MCP时,最终封装和制造的良品率等于MCP中所有单元的良品率的乘积。为了举例说明这一原则,我们假设每个元件的良品率是90%,当MCP由4片裸片组成时,总的良品率就是90%x90%x90%x90%=65%。很明显这么低的良品率无法实施大批量生产,特别是服务于对成本有连续压力的很大批量的消费市场时。在采用MCP配置时已知良好芯片(KGD)是一种常用的做法,可以将良品率保持在一个可接受的水平。

根据功能和规格要求,存储器和基带器件约占移动电话25%的BOM。整合了存储器和基带器件或协处理器的SiP成本较高,如果SiP内部任一器件不能满足规格要求,那么整个SiP都会被拒收和舍弃。

2. SiP的灵活性不够

SiP的推出还受限于当时组件的可用情况。为了获得有竞争力的解决方案,所有组件必须从一开始就用最具成本效益的技术进行生产。

对ASIC和存储器来说,开发资源和所需的时间有很大的区别,因此情况变得更加复杂。在许多情况下,这些器件是由不同公司生产的,也就意味着同时获得它们相当困难。只有产品种类丰富的开云棋牌官网在线客服供应商才能从公司内部提供大多数器件,满足时间上的要求。

一旦SiP开发出来并开始向移动电话制造商正式供货后,如果因为有新技术可使成本降低而想修改SiP中任何一个组件时,将要求对整个SiP进行重新认证。这是一个漫长而昂贵的过程。

PoP概念介绍

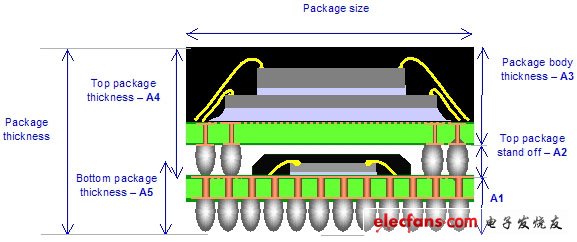

PoP概念将ASIC与存储器分离开来,从而可以采用不同的途径对ASIC和存储器分别进行开发和推出。这个解决方案是通过在一个封装顶部组装另一个封装实现的。顶层封装的焊球直接绑定在底层封装上表面的连接焊盘上(如图所示)。

底层(下层)封装一般包含ASIC形式的基带器件或多媒体处理器(如有需要时,底层封装也可以使用存储器模块,以实现存储器的多重堆叠)。顶层(上层)封装一般包含多个存储器件(Flash和RAM)。

与双封装解决方案相比,PoP解决方案可以显著节省PCB的面积。同样重要的是,两个器件的相邻意味着性能可以得到优化。在使用100MHz以上的存储器接口时,对封装设计中的信号和电源线需要使用专门的指导和技术才能确保信号完整性。封装特性在系统的总体性能中起着重要的作用。设计验证和并发仿真技术曾经是系统设计中的一部分,现在也可用于PoP开发。

PoP开发所面临的关键问题

1. 标准化

PoP解决方案允许制造商分别从不同的供应商那里获得底层和顶层封装。随着许多新技术的发展,可能会出现各种提案,比如各个封装的物理尺寸和引出球。

在JDEC标准中,针对封装有物理尺寸和电气球引出等多种可变选项。选择采用何种标准取决于顶层和底层封装的可用性。JDEC标准JC63涵盖了引出球和总线组合,而JDEC标准JC11涵盖了机械尺寸。

2. 物理尺寸

封装尺寸决定了PCB上占用的面积,封装厚度由A1+A2+A3组成的外形轮廓构成,如图所示。

需要保持整个封装的高度,同时要考虑顶层封装的绝缘A2,从而确定底层裸片和模帽的可用空间。封装球以双排形式安排在四周。

如图2所示,尺寸D和E提供了封装体的大小,e和b定义了球间距和球直径。减少球尺寸和球间距可以在给定的参数条件下引出更多的信号,从而允许提供更多的功能。更精细的球尺寸和球间距封装正在开发中,并将被收录进JDEC标准。

3. 可制造性

在表贴技术(SMT)生产线中的普通球栅阵列(BGA)封装上使用PoP时需要考虑两个主要因素:预回流和后回流的球高度,最终将由它确定图1所示的绝缘A2;在设备温度范围和回流温度曲线内顶层和底层的翘曲特性。

本文小结

PoP可以满足小体积和高性能的应用要求,其内部元件可以采用独立的开发路径。另外由于两个器件可以分离,因此比SiP或SoC解决方案有更大的灵活性。