功率放大器是射频发射机中的必不可少组成部分,它的主要功能是提供整个通信系统在发射信号与接收信号时的运作功率。通信系统中消耗能量最多的就是功率放大器,人们希望功率放大器的效率尽可能高,这样就减少电池的消耗,从而延长电池的使用寿命。

多年来,人们对于功率放大器的效率提高技术做了很多有价值的研究,如自适应偏置技术、EER技术、Doherty技术以及LINC技术等等,这些方案虽然巧妙,但大多结构复杂,并不适合用于便携式通信终端的开发,本文中采用共源共栅电感对电路进行改进,从而提高功率放大器的效率。

1 共源共栅电感的工作机理

本次功率放大器设计中使用到共源共栅(Cascode)结构,这种共源共栅管的源极存在着较大的寄生电容,这在本次5.25GHz功率放大器的设计中是不得不考虑的。由模拟电路知识可知:如果电路中有电容,那么电路上的信号就要对电容进行充放电。所以共源共栅管源极的寄生电容就要从电源汲取电流进行充放电,这样势必增加了额外的功耗,从而降低了功率放大器的效率。

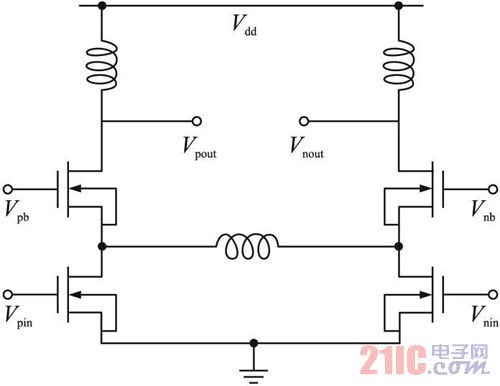

如果给这些寄生电容提供一种能量交换渠道,使其尽可能少地从电源处汲取电流,那么就会降低这些寄生电容对功率放大器效率的影响。根据对模拟电路的基本认识,不难想到可以引入电感,电感和寄生电容之间可以进行能量的交换,从而减少了寄生电容对电源处电流的依赖,也就减少了额外功耗,会在一定程度上提高功率放大器的效率。图1是上述思想的具体实现,中间的共源共栅电感是一个对称型电感,可以拆成两个电感量相同的电感,他们的电感量是该对称型电感的一半。加入输入信号后,电感与共源共栅管的源极寄生电容会发生谐振,进行能量的交换,这就降低了寄生电容充电时对电源处电流的依赖程度。

本次A类两级功率放大器设计,原理图中第一级加入了共源共栅电感,第二级并未添加,主要是从版图面积的角度考虑的,因为电感在芯片中所占用的面积比其他元件都要大很多。此外,在进行版图设计时,有意将原理图中一个共源共栅电感拆分成两个电感,这是为了提高电路结构的对称性,从而有利于功率放大器的整体性能,关于这一点,将在后面的版图设计中进行分析。

图1共源共栅电感的应用

2 功率放大器设计

放大电路如图2所示,电路结构为差分形式,采取两级放大,分别为驱动级和输出级。驱动级采用差分的共源共栅(Cascode)结构,可以提供适当的电压增益;输出级也是差分的共源共栅结构,在提供一定的电压增益的同时,还提供输出功率,这种结构可以提高功放输出电压的摆幅,从而降低对MOS管最大电流能力的要求,提高功放的效率。两级之间采用的耦合电容Cp和Cn在提高隔离度的同时起到级间阻抗匹配的作用。电感Lp1、Lp2、Ln1、Ln2用作负载,电感Lnp用来抵消源极寄生电容对功放效率的影响,其中Lp1、Ln1和Lnp采用工艺库里的片上螺旋电感来实现,而Lp2和Ln2可以采用高Q值的键合线电感实现,这样可以有效提高功放的增益,当然只要工艺条件允许,在对增益要求不是很高的情况下,也可以采用工艺库里的片上螺旋电感来实现。单路输入信号经输入匹配网络由巴伦转换成两路信号Vpin和Vnin,放大后的两路信号Vpout和Vnout经输出匹配网络由巴伦转换成一路信号送至天线。其中,输入匹配采用共轭匹配以达到最大增益,输出匹配采用功率匹配以输出最大功率,都是以简单的LC匹配网络为实现形式,通过高频辅助设计软件ADS中的Smithchart来设计。

图2 两级A类放大电路结构示意图

3 仿真结果

图3为输出功率与功率增益的仿真结果,可以看出,输入1dB压缩点(IP1dB)-9dBm对应的输出1dB压缩点(OP1dB)为19.7dBm;功率增益接近30dB,一般来说,功率增益达到25dB,就算是较高的增益了,所以本方案的A类功率放大器的增益还是比较理想的。

图3 输出功率与功率增益

功率附加效率是功率放大器设计中一个很重要的指标,用来表征功率放大器的效率,关系到电池的使用寿命。本次所设计的是A类功率放大器,为线性功率放大器,所以功率附加效率不会高,但是通过对电路的改进,还是可以将功率附加效率提高一点。图4是对功率附加效率的仿真结果,将电路不加共源共栅电感与加共源共栅电感对功率附加效率的影响进行了对照,可以看出,电路改进后,功率附加效率为17.985%,比电路改进前的15.975%提高了2个百分点,虽然不是很高,但至少说明了共源共栅电感的作用,以后对于线性功率放大器效率的提高来说,添加共源共栅电感就是一个很好的思路,不过,共源共栅电感用得不好的话,就很容易浪费芯片的面积,得不偿失。

图4 电路改进前后功率附加效率的对照

4 版图设计

本次功率放大器版图设计使用台积电0.18umCMOS工艺来实现,实现平台为Cadence公司的Virtuoso版图设计软件,运行环境为linux操作系统。

设计中采用了差分对,差分对的元件数量是同等情况下单端电路的两倍,所以差分对的版图面积大约都是单端电路的两倍。人们希望输入差分信号能够被无失真的放大和传输,也就是说,输入是纯差分信号的话,输出也必须是纯差分信号,为此,在版图设计过程当中,要特别注意对称性的设计。

图5给出了A类功率放大器的版图,信号由左端输入右端输出,Vpin、Vnin为输入差分信号,Vpout、Vnout为输出差分信号,Vpb1、Vnb1为第一级放大器电路的偏置电压引出端,Vpb2、Vnb2为第二级放大器电路的偏置电压引出端,电源电压引出端Vdd分布于整个版图的上下两边,接地端gnd分布于整个版图的左图5A类功率放大器版图右两边。纵观整个版图,做到了对称性设计,面积约为1.3mm×1.3mm。