0 引言

在系统设计中,设计师们面临的重要挑战是既要支持高可靠性(HA,High Availability),又要使系统尽可能简单、有效。而PCI Express、基于PCI Express的高级交换架构(Advanced SwitchingArchitecture)、基于PCI Express的QOS(Quality-Of-Service)特性以及PCI-Express非透明桥的出现,共同为这样的系统设计提供了一个非常有发展潜力的解决方案。

1 PCI Express技术简介

PCI Express技术是一个比较新的互连标准。该技术适用于高性能的芯片到芯片、板子到板子、背板和机箱之间的互连。它是PCI标准的一个演进版本,因此,在软件结构上仍保持着对PCI的兼容性。

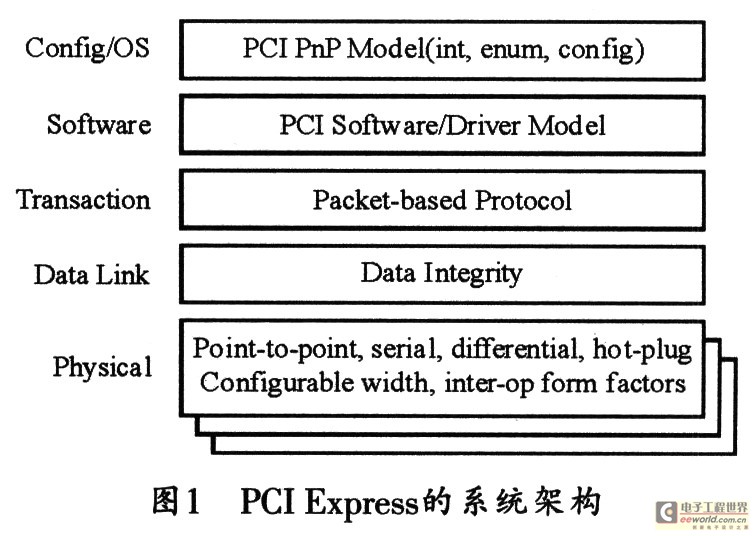

PCI Express是基于层次化的、高速的串行通信技术。其协议栈可分为物理层、数据链路层和传输层。

其中,物理层包括低电压差分信号的高速串行接口、8B/10B编码以及AC耦合差分信号。通常把一组LVDS双绞线称为一个通道(lane),而且PCI Express允许将多个通道合并成一个更大更宽的端口,如x1,x2…直到x32。物理层接口可支持热插拔(hot-plugging)。

数据链路层可支持与临近PCI Express实体交换数据包,同时支持数据完整性(data integrity)和顺序性检查,以及数据包的确认和流量控制的能力。

PCI Express技术系统中的传输层可在主机和终端设备间传送读/写请求,并可选择性的提供传输层的端到端(end-to-end)数据包的完整性检查(CRC-32)。

一直以来,PCI Express传输系统中的物理层的速度一直在不断的提高,但是,分层结构使物理层的变化不会影响到它的上层。如PCI Express1.x标准的时钟频率是1.25 GHz,2.0标准的则为2.5 GHz,3.0标准的是4 GHz。图l所示是PCI Ex-press协议栈结构。

PCI Express的QOS可通过定义8个运输等级(TC-Traffic Classes)、八个虚拟通道(VC-VirtualChannel)、TC到VC的映射以及VC的仲裁机制来实现。

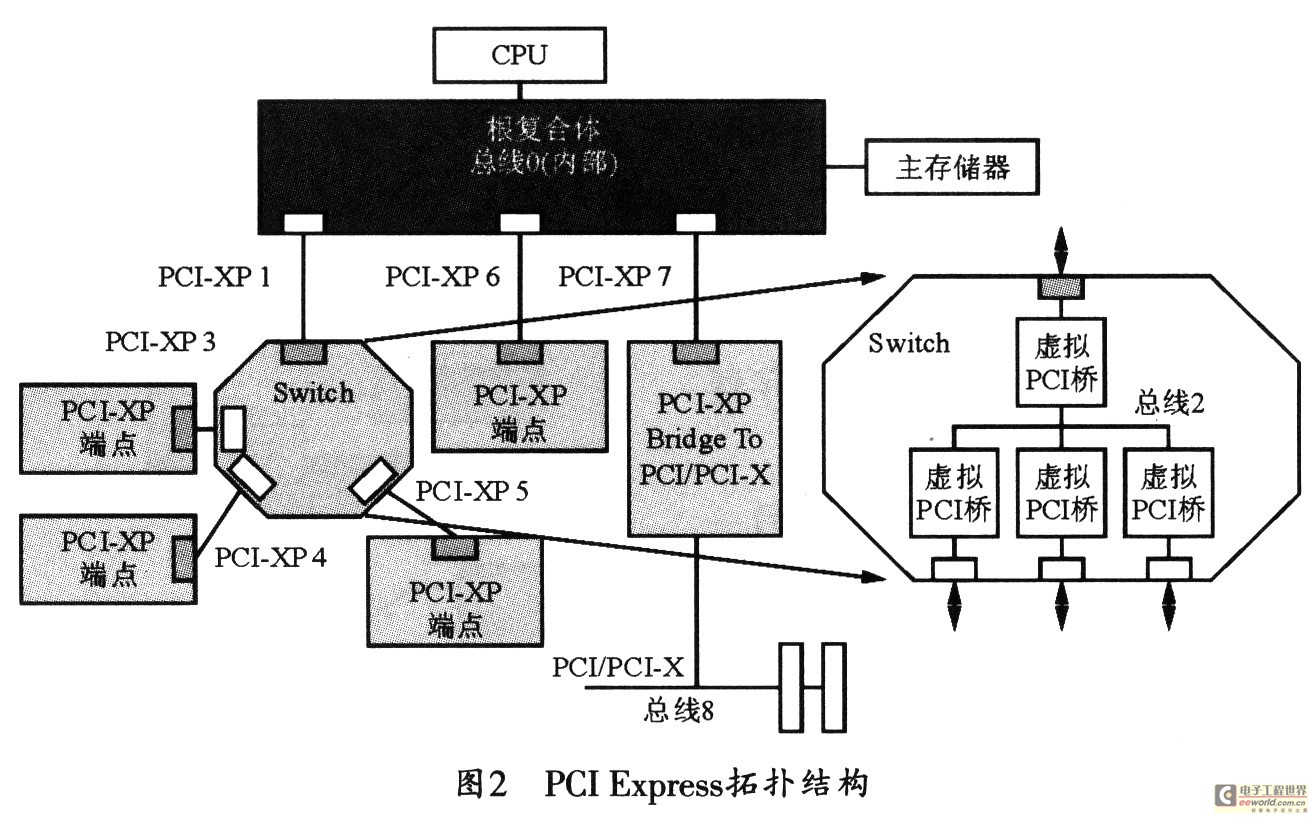

PCI-SIG组织则定义了从PCI Express串行接口到PCI/PCI-X的桥接规范。该规范可以使得当前使用PCI/PCI-X的应用系统能够平滑的转移到PCI Express。图2所示是一个典型的PCI Express系统,其中包含有根复合体(root complex)、PCIExpress交换开关(switch)、桥(bridge,PCI Expressto PCI-X,PCI Express to PCI)以及端点(end-point)等设备。

2 PCI Express非透明桥

与PCI/PCI-X一样,PCI Express本身也是开发维护一个以单一主机为中心的系统架构,但是人们一直使用非透明桥把他们用在多主机的环境中。

非透明桥的功能和透明桥很相似,其主要差别只有一点,即在非透明桥的两边都有智能设备或处理器,并且他们拥有独立的地址空间。而且,非透明桥一边的主机不能看到桥另一边的完整地址或I/O空间。每个处理器把非透明桥的另一边看做一个端点(endpoint),并把它映射到自己的地址空间。

2.1 地址翻译

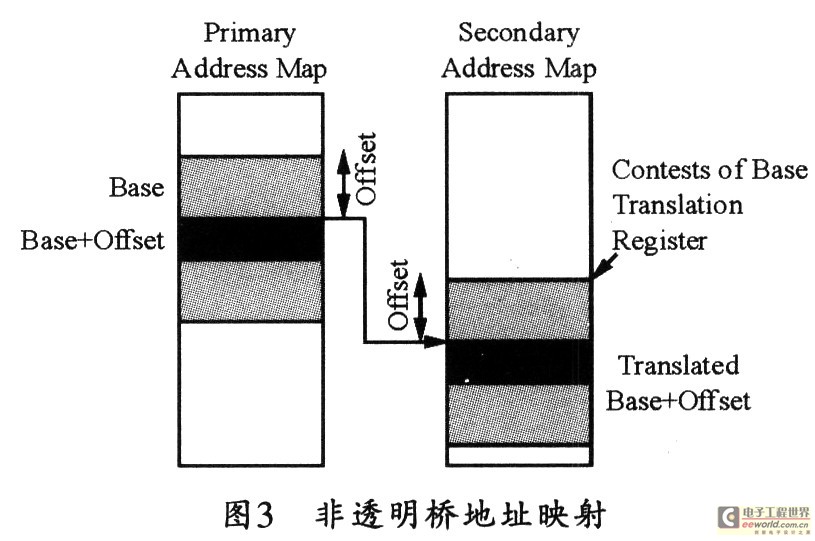

在非透明桥环境中,PCI Express系统需要在从一个内存地址空间穿越到另一个地址空间时进行地址翻译。每一个非透明桥(NTB)端口都有两套基地址寄存器(BAR),一套是给主设备端用的,另一套是给从设备端用的。基地址寄存器可用来定义在非透明桥另一端的内存地址空间的地址翻译窗口,并允许这个翻译被映射到本地的内存或I/O空间。每个BAR定义了一个设置寄存器(setup register),可用来定义窗口的大小、类型以及一个地址翻译寄存器。与透明桥基于总线号转发所有CSRs不同,非透明桥设备只接受针对本设备的CSR事务。其地址翻译技术有直接地址翻译和查表地址翻译两种。

在直接地址翻译模式下,地址翻译的过程是基于事务终结的BAR基址加上一个偏移量。BARs中的基址翻译寄存器可被用来设置这样的翻译。图3所示给出了从主设备端地址映射到从设备端地址的偏移过程。

BARs则用一种特别的查找表来为落在它窗口中的事务进行地址翻译。因为地址中的索引域可通过编程来调节窗口大小,因此,这种方法在本地地址到主机地址的映射中具有更高的灵活性。通常索引被用来提供新内存地址的高位比特(bits)。

2.2 处理器间的通信

非透明桥允许桥两边的主机通过便笺寄存器、门铃寄存器和心跳消息来交换一些状态信息。

便笺寄存器在非透明桥的两端都是可读写的,但是,便笺寄存器的数量在具体的实现中是可以不同的。他们可以被桥两边的设备用来传送一些状态信息,也可作为通用的可读可写寄存器使用。

门铃寄存器被用来从非透明桥的一边向另一边发送中断。非透明桥的两边一般都有软件可以控制的中断请求寄存器和相应的中断屏蔽寄存器。这些寄存器在非透明桥的两边都是可以被访问的。

心跳消息一般来自主设备端往从设备端的主机,可用来指示它还活着。从设备主机可监控主设备主机的状态,如果发现出错,它就可以采取一些必要的措施。通过门铃寄存器可以传送心跳消息。当从设备主机没有收到一定数量预先规定好的心跳消息时,就可以认为主设备的主机出错了。

3 基于PCI Express非透明桥的多主机系统

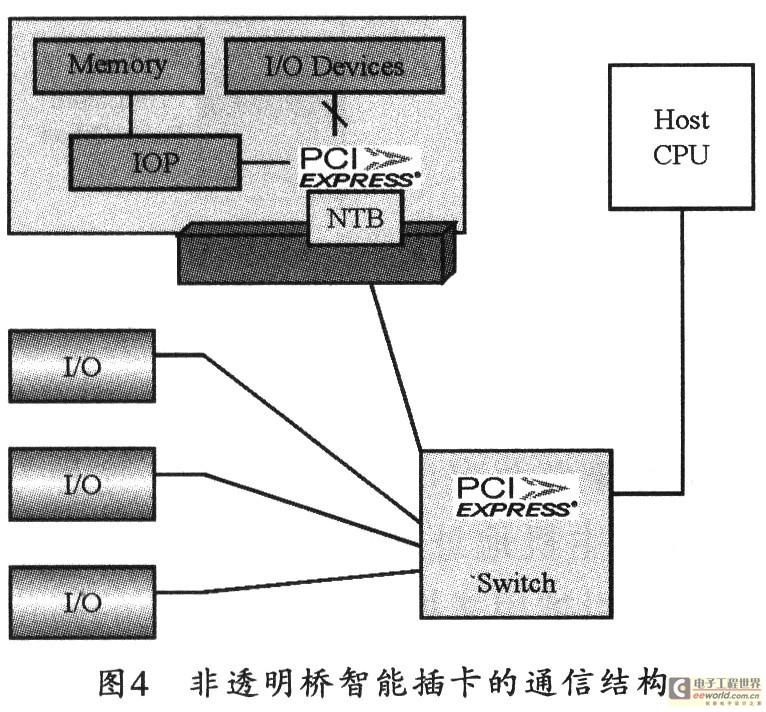

3.1 智能插卡

在智能卡模式下,智能插卡上的PCI Express非透明桥可以将IOP和Host CPU隔离开来,但仍允许这两个CPU通过一些特殊的寄存器进行通信。图4所示是智能插卡模式下的非透明桥的通信结构。

3.2 双主机模式

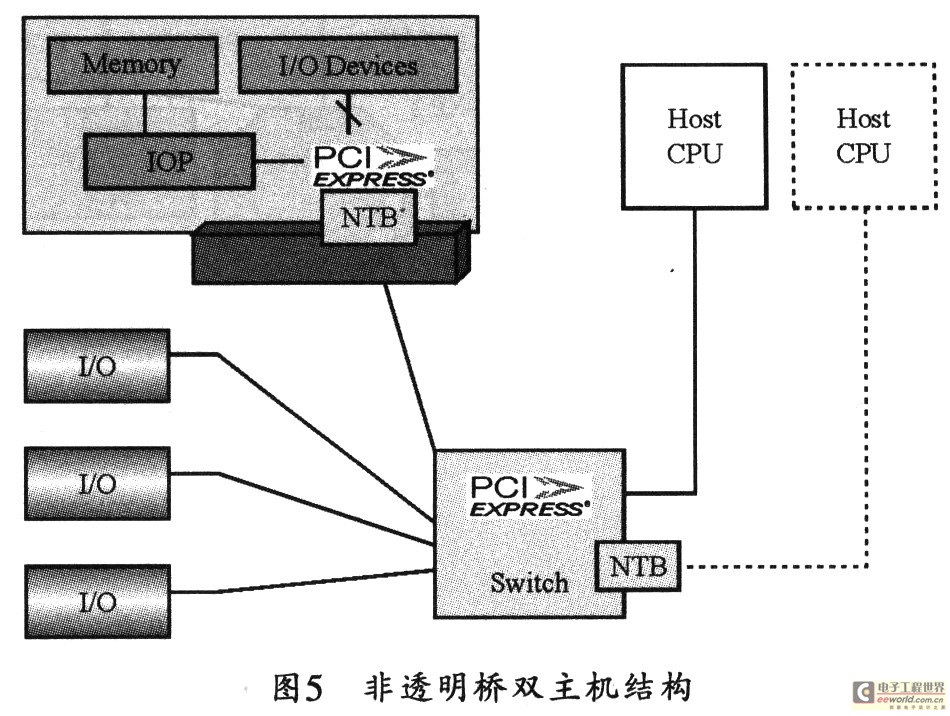

非透明桥也可用在双主机(Dual Host)、主机故障转移(Host Failover)和负载分担(Load-shar-ing)等应用中。图5所示是将两个Host CPU被非透明桥隔离开的结构示意图。

3.3 多主机模式

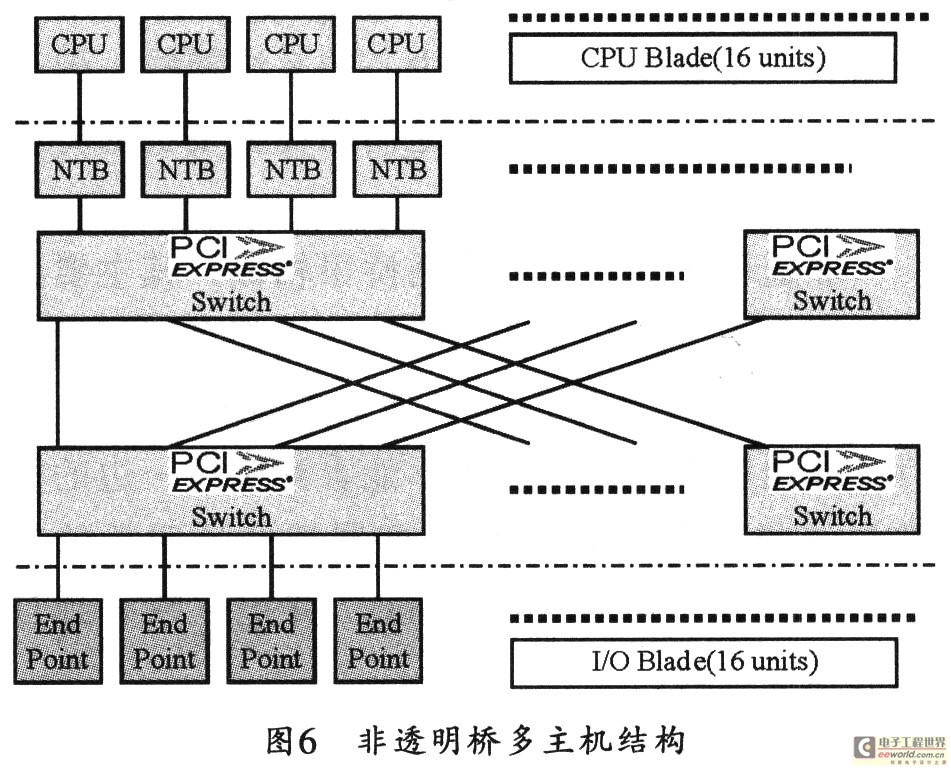

在多主机系统中,每一个主机都可以通过非透明桥接入到系统之中,并且可以访问所有的端点。在PCI的枚举过程中,每个端点都要和某个特定的CPU关联,但在正常的操作过程中,依赖于非透明桥的地址翻译能力。所有的CPU都可以访问所有的端点。图6所示是主机系统的非透明桥结构。

4 结束语

非透明桥技术在PCI时代就已被应用。现在,在PCI Express系统中也有类似的实现。相信在不远的将来,从简单的智能插卡到复杂的、带虚拟输入输出技术的多主机系统,人们都将看到PCIExpress非透明桥的广泛应用。