引言

VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。利用FPGA芯片和EDA 设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA 显示控制器,不仅能够大大降低成本,还可以满足生产实践中不断变化的用户需要,产品的升级换代方便迅速。

在本设计中采用了Altera 公司的EDA 软件工具Quartus II,并以ACEX系列FPGA 的器件为主实现硬件平台的设计。

1 基于FPGA 的VGA图形控制器系统框图

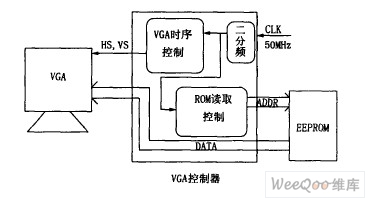

根据自顶向下的程序设计思想,采用模块化设计,我们对VGA 图形控制器进行功能分离并按层次设计。利用VHDL 硬件描述语言逐一对每个功能模块进行描述,并逐个通过编译仿真,最后下载到硬件平台调试。本设计的VGA 控制器主要由以下模块组成:VGA 时序控制模块、分频模块、汉字显示模块、图像控制模块、ROM读取模块等,如图1 所示。

图1 基于FPGA 的VGA 图形控制系统框图

2 主要功能模块设计

2. 1 VGA 时序控制模块

VGA 时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA 时序标准产生相应的脉冲信号。对于普通的VGA 显示器, 其引出线共含5 个信号: G,R ,B (3 基色信号) ,HS(行同步信号) ,VS(场同步信号) 。在5个信号时序驱动时,VGA 显示器要严格遵循“VGA工业标准”, 即640 Hz ×480 Hz ×60Hz 模式。

对于VGA 显示器,每个像素点的输出频率为25. 175MHz ,因此采用50MHz 的时钟信号,经过二分频模块,得到25MHz 的输入时钟脉冲。依据VGA 时序标准,行同步信号HS ,行周期为31. 78μs ,每显示行包括800 点,其中640 点为有效显示区,160 点为行消隐区,每行有一个脉冲,该脉冲的低电平宽度为3. 81μs (即96 个脉冲) ; 场同步信号VS ,场周期为16.683ms ,每场有525 行,其中480 行为有效显示行,45 行为场消隐区,每场有一个脉冲,该脉冲的低电平宽度为63μs (2 行)。

图2 VGA 行扫描、场扫描的时序图

依据这个标准,把输入的25MHz 时钟脉冲按照对应的像素点数和扫描行数进行分频处理,可以得到最后符合时序要求的行频率和刷新频率。

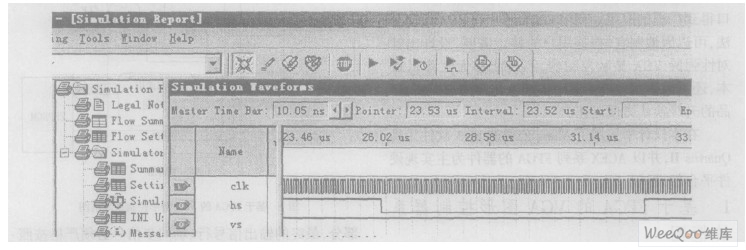

利用Altera 公司的QuartusII 软件对VHDL 语言描述的VGA 时序控制模块进行编译、仿真,可得到行同步信号HS , 场同步信号VS 的时序仿真波形,如图3 所示。

图3 时钟信号仿真图

由仿真结果波形可以看到,行同步信号的时钟周期约为31. 9μs ,场同步信号的时钟周期约为16。

6ms ,达到了VGA 标准时序的要求,可以为CRT 显示器提供准确的行场同步信号。

在硬件系统上,通过彩条图案的生成验证了时序生成的正确性,可产生竖彩条、横彩条、棋盘格等多种彩条模式。

2. 2 汉字显示模块

汉字生成模块可实现在显示器上显示汉字、字符等。字模信息可以利用字模提取软件来获得,得到了汉字的字模信息后,可以通过屏幕上的横坐标和纵坐标按照字模信息定义像素的颜色,这样就可以显示任何字体、任何点阵的汉字,并根据需要决定汉字在屏幕上的位置。至于英文以及其他任何符号的显示原理与汉字显示的原理一样。

显示器上显示的汉字精细度取决于显示屏所分网格的数目多少。设计者可以根据不同要求设定不同的网格数目。Altera 公司的FPGA 器件内均内置— 26 —了嵌入式阵列块EAB ,通过调用其中的LPM ROM模块,可任意设置参数,构成内置的ROM存储器,存放所必要的字模信息,能与汉字显示模块配合,显示出任意汉字。

2. 3 图形显示模块

2. 3. 1 ROM读取控制模块

当VGA 显示器要显示一帧图像,需要比较大的数据量,FPGA 芯片内置的ROM 存储器难以满足这么大的数据存储要求,必须把图像数据存入外部的存储器中。

外部存储器可以有多种选择, 如ROM,、双口RAM、甚至SDRAM 等,采用何种存储器将最终决定读取控制模块的数据读取方式。如ROM 可用直接产生地址信号的方式对芯片进行访问,而SDRAM常常利用DMA 控制方式配合CPU 进行读写操作。

这里采用型号为28C040 的4M EEPROM 外部存储器,可以在单片内存储整屏图像,同时考虑到存储空间的大小,本设计采用每个像素的颜色位深为3 位,共可显示8 种颜色。此模块最终仿真结果如图4所示。

图4 地址信号仿真图

由图中的仿真结果可以看到,地址信号每两个时钟脉冲加1 ,而每两个时钟脉冲代表扫描过一个像素点,由此可验证以上设计的正确性。

2. 3. 2 BMP 图像数据存入ROM

要把一幅图像的数据写入ROM,首先必须解决的就是写入文件的格式问题。一般的方法是通过编程器把Intel Hex ,或者二进制文件。 bin 逐字节写入ROM。而图像都具有固定的格式,如BMP , JPEG,GIF 等,其中的BMP 格式图像是一种很常见的图像格式,没有经过压缩处理,且文件结构相对简单,易于处理,在本设计中采用了BMP 图像作为研究对象。将BMP 文件直接转化为Intel Hex 文件比较困难,因此可先将BMP 格式文件转化为mif 格式文件,再由Quartus II 直接将mif 文件转化为Intel Hex 文件,最后再将图像数据烧写入ROM中。由于没有现成的转换程序,选择Visual C ++ 自行编写转换程序。

Memory Initialization File ( . mif) 格式是Quartus II中ROM的初始化数据文件格式,它记录方式比较简单,其中地址和数据都可为十进制或十六进制,冒号左边是地址值,右边是对应的数据,并以分号结尾。

相对mif 文件,BMP 格式的位图文件稍显复杂,它包括位图文件头结构、位图信息头结构、位图颜色表和位图像素数据四部分。位图文件的保存顺序如下:位图文件头→位图信息头→位图颜色表→位图像素数据。处理位图时要根据文件的这些结构得到位图文件大小、位图的宽、高、实现调色板、得到位图像素值等等。以目前应用较为广泛的24 位真彩色图像为例,其特点是:24 位真彩色图像存储文件中不带有图像颜色表;图像中每一像素由RGB 三个分量组成,每个分量各8 位,每个像素需24 位;颜色分量值f red , f green , f blue 的取值范围都为0 ~ 255。

对于用到颜色表的位图,图像数据就是该像素颜色在调色板中的索引值。对于真彩色图像,图像数据就是实际的R , G ,B 值,一个像素是由3 个字节24位组成, 前8 位表示B , 中间8 位表示G , 后8 位表示R 。

由于硬件存储资源的限制,取图像像素的位深为3 ,总共可显示8 种颜色。首先把BMP 图像数据的RGB 分量分别读出,并且各取1 位,即颜色分量值只能取值‘0’或‘1’。针对24 位真彩色图像的特点,可对颜色分量值进行粗略取样,当颜色分量值f red >127 ,取f red = 1 ;反之取f red = 0。同理,颜色分量值f green , f blue 可取得相应的0 ,1二值。

最后在利用Visual C ++ 编写转换程序时应注意,BMP 文件是从左至右,从下至上排列的,即读文件时,最先读到的是图像最下面一行的左边第一个像素,最后读到的是最上面一行的最右边一个像素,这与VGA 显示器的扫描顺序恰好相反。

3 结论

经过硬件平台的验证,基于FPGA 的VGA 图形显示器已达到设计要求,可实现彩条、汉字、小图像和大图像的显示,并可实现FPGA 器件对显示器的单片控制。

由于受到存储器件容量的限制,本设计中存储的图像数据所采用的像素位深为3 位,共可显示8种颜色。在实际应用中,可以使用更大的存储器,最终实现256 色图像,乃至真彩色图像的显示。在此设计基础上,通过使用SDRAM 等外部存储器,利用DMA 控制方式,并且配合Altera 的nios 嵌入式软核CPU ,可以在SOPC 开发平台上最终实现兼容SVGA ,TVGA 标准等的更复杂显示控制器。