随着开云棋牌官网在线客服工艺技术向着纳米尺度的发展,微电子技术进入SoC(系统芯片)时代,且沿着可靠性强、体积小、功耗低等方向继续发展。在下一代SoC设计流程中,系统级EDA工具的地位变得比以往更加重要,ESL(Electronic System Level)设计方法学将是设计下一代SoC的关键,因为逐渐缩短的上市时间需要硬件-软件并行设计。

本文以Tensilica Xtensa可配置、可扩展处理器为开发平台,探索了高性能低功耗ASIP(Application Specific Instruction-set Processor专用指令处理器)开发流程。

ASIP设计理论

面向特定应用的ASIP处理器,既有ASIC执行特定应用的高效性,又有GPP处理器可编程的灵活性,能够简化设计复杂度、缩短设计周期、加快上市步伐,在SoC设计中得到了广泛的应用。如何快速高效地定制ASIP,使其满足运算性能、芯片面积、上市时间和功耗等要求,是一个极具挑战性的问题。设计者需要在ASIP指令集设计过程中在广泛的设计空间进行指令集探索,寻找满足设计约束的处理器体系结构[1-8]。因此迫切需要可以支持快速ASIP设计的行为级设计方法和合适的EDA工具。

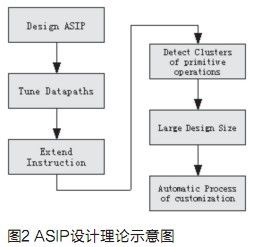

现在设计可编程处理器,很少是全新定制指令,普遍采用的方式是在已有的某RISC指令集基础上进行部分定制(或说扩展/自定义/优化指令)。理论上,为了研发一款ASIP式处理器,需要在已有GPP、ASIP、ASIC的基础上调整数据通路(Datapath),即增加功能单元,如图1所示的5级Pipeline处理器中添加自定义功能单元(Custom Unit),同时需要专用指令将操作数调入此自定义单元进行数据处理。为了实现指令扩展,首先需要分析应用目标数据处理算法的特性,从中找出那些经常出现且可以绑定的基本操作包;然后从众多实现方式(或大设计空间)如:(1)FLIX(VLIW或Multi-slot);(2)Vector(SIMD);(3)FUSED(Add-with-Shift-by-1)中选择最合适的途径[9-10]。因为设计者很难一次性找到最优途径,常常需要不同方式之间进行比较,因此一般需要某些EDA工具帮助快速实现指令自定义以及分析当前自定义指令对ASIP性能的影响。图2采用Top-down方式示意出ASIP设计的理论步骤。

Xtensa开发工具集

目前,可用于ASIP体系结构及指令系统开发的EDA工具,包括Tensilica的Xtensa开发工具集(Xplorer、XCC、XPRES、XTMS、XEnergy),CoWare的Processor Design,University of Campinas的ArchC等。但Tensilica 的Xtensa开发工具集因功能强大而得到广泛应用。

Tensilica针对SoC应用而设计的Xtensa系列可配置处理器及其开发工具,提供了一种自动化程度非常高的开发流程,该流程包括仿真C/SystemC级算法、调整处理器体系结构、向基本处理器添加专用指令、自动生成硬件RTL代码和与之相匹配的软件工具链(如编译器等),通过可配置处理器技术和TIE(Tensilica Instruction Extension)指令扩展技术替代了RTL开发。和ASIP相关的具体功能如下。

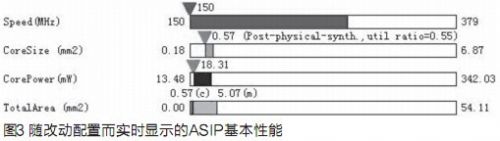

(1) 对处理器的体系结构进行配置的同时,设计者可以在Xplorer中实时看到每一次调整对ASIP性能产生的影响,如图3。

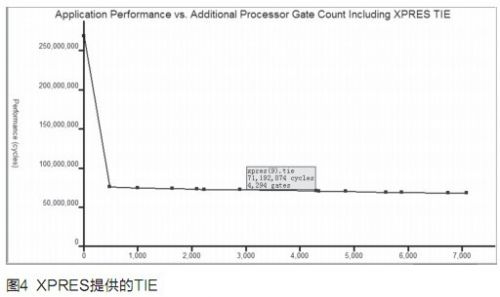

(2) XPRES工具可以完全自动地分析应用程序生成相应的指令扩展。设计人员只需输人利用标准ANSI C/C++设计的原始算法,XPRES便可以根据内置的配置选项完全自动化地产生多种TIE指令组合供设计者折中选择。

(3) 使用自定义的FLIX指令,它包括七种不同的64位指令字格式以及高达8个并行操作指令槽。FLIX提供VLIW风格的并行执行功能却没有VLIW处理器会发生的“代码膨胀”现象。

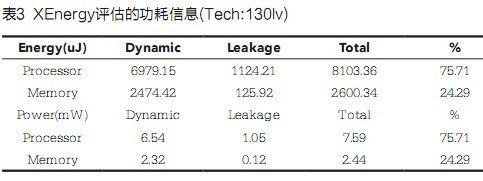

(4) XEnergy可以根据最终的体系结构配置和指令系统(包括设计者自定义的TIE扩展指令)评估ASIP功耗指标。

基于Xtensa开发工具的ASIP设计流程

本项目目标是设计一款实现低功耗无损压缩的嵌入式ASIP。首先,经过比较从众多压缩算法中选择了简单高效的FELICS算法[11];然后开发算法的C++代码进行实际图像压缩实验。试验结果:FELICS对12幅目标图像的平均无损压缩比为2.7:1,满足本项目要求。之后的工作就是根据图2流程实现针对FELICS算法的ASIP设计。

(1)将C++代码输入Tensilica Xplorer开发环境,选择系统自带的sample_config-params (RB-2006.0)配置信息作为ASIP开发的起点,即在此基础上进行体系结构的调整和指令的自定义开发。

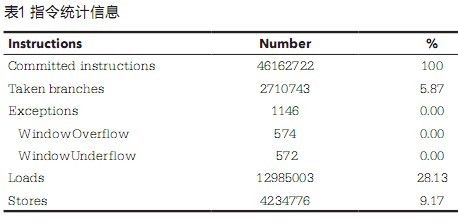

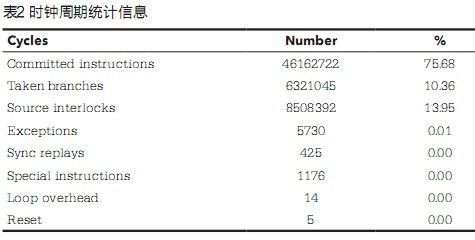

(2) 运行代码并进行特性分析(Profile),表1和表2是最基本的指令和时钟周期信息,此外还可以得到pipeline甘特图、Branch cycle和Interlock cycle对比图等信息。这些信息为后续的体系结构调整和指令优化提供了必要的数据依据。

(3) 调整处理器配置信息中的众多项目,如MUL16 / MUL32 / MAC、Zero-overhead loop instructions、Pipeline length、Number of coprocessors、Floating point coprocessor、Special register、Cache size等,设计者可以得到图3所示的速度、面积、功耗信息。然后回到(2)再次运行代码及特性分析,考察体系结构改动带来的影响。

(4)利用XPRES工具,设置FLIX的Issue Width、SIMD的Vector Length、Register的Depth / Width / Ports、Fusion的Area / Latency / Operands等,XPRES会自动生成若干种不同的自定义指令TIE供设计者选择使用。设计者参考每一个TIE的Cycles和Gates数折衷考虑,当然设计者还可以手动增加TIE指令。然后将TIE绑定到调整后的体系结构(配置信息)上,回到(2)运行代码及特性分析,考察TIE带来的性能提高效果。

(5) 运行XEnergy命令工具,对以上步骤生成的ASIP进行全面功耗评估,如表3所示。

(6)经过(2)到(5)多次反复调试,在Xtensa高效的开发工具下,用户很快会得到满意的ASIP体系结构及指令系统。然后,将配置信息和TIE指令信息提交给Tensilica的服务器,Xtensa Porcessor Generator(XPG)会生成相应的RTL或Netlist,供用户进行后端实现,同时XPG还会生成ASIP所需的软件开发工具,如编译器、汇编器,使设计人员省去了针对ASIP开发编译器(或编译器重定向)的繁重工作。

结语

Tensilica Xtensa体系结构可配置、指令集可自定义处理器和Xplorer、XPRES、XEnergy等工具集大大提高了ASIP处理器开发速度,加快了针对不同应用领域探索专用处理器设计空间的效率。本文重点叙述了借助Xtensa平台开发ASIP时前端设计的各个步骤,此设计流程具有较强的借鉴价值。