AVS(Audio Video CodingSTandard)是由我国数字音视频标准工作组制定的具有自主知识产权的第二代音视频压缩准。AVS实行1 元专利费用的原则,相比其它音视频编解码标准具有编码效率高、专利费用低、授权模式简单等优势。AVS解码器的结构复杂、运算量较大,要在嵌入式平台上实现实时解码具有较大难度。在对解码器性能优化的过程中可以依据使用平台对其进行汇编指令集的优化或者针对解码器的关键算法模块进行改良,以上方法对解码器性能的提高均有一定作用,本文提出一种利用嵌入式平台的L1P Cache高速缓冲功能实现处理器对程序代码的高效率访问的方法,从而达到提高AVS解码器性能的目的。

1 高速缓存Cache的应用

目前越来越多的编解码算法采用DSP的方式实现,随着DSP芯片主频的不断攀升,存储器的访问速度日益成为系统性能提升的瓶颈。在现有的制造工艺下,片上存储单元的增加将导致数据线负载电容的增加,影响到数据线上信号的开关时间,这意味着片上高速存储单元的增加将是十分有限的。为了解决存储器速度与CPU内核速度不匹配的问题,高性能的CPU普遍采用高速缓存(Cache)机制。

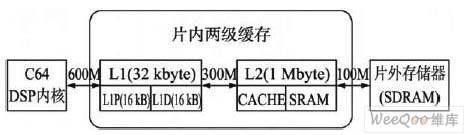

以TI的C64x DSP为例,存储器系统由片内存储器和片外存储器两部分组成。其中,片内存储器采用两级缓存结构,第1级L1距离DSP核最近,数据访问速度最快,可以达到每秒600Mbyte,只能作为不能寻址的Cache使用,由相互独立的L1P和L1D 组成。

L1P Cache是处理器访问程序代码的高速缓冲存储器,大小为16 kbyte,采用直接映射方式,每行大小32byte;L1D Cache是处理器访问数据的高速缓冲存储器,大小为16 kbyte,采用2路映射,每行大小为64byte。第2级L2是一个统一的程序/数据空间,可以整体作为SRAM映射到存储空间,也可以作为Cache和SRAM按比例的一种组合。L2与L1之间的数据交互速率为每秒300 Mbyte,L2与SDRAM之间的数据交换速率为每秒100 Mbyte。片外存储器是第3级,一般由SDRAM构成。L1、L2和片外SDRAM构成了整个存储器系统的层次结构。C64X的两级缓存结构若能运用恰当,将能极大地提高程序性能。

根据图1的三层次的存储器系统, C64X读取程序代码时,先查看1级缓存L1,若L1已缓存了所需代码,则直接从L1读取;若L1没有该代码的缓存,则访问2级缓存L2;若L2也没有,则通过EMIF接口访问外部SDRAM,把所需代码从外部SDRAM拷贝到L2缓存区,再从L2缓存区拷贝到L1,最后由DSP内核取得。

图1 三层次的存储器系统(图中B代表byte)

研究表明,采用这种多级缓存的架构可以达到采用完全片上存储器结构的系统约80%的执行效率。本文致力于更深入地研究Cache的机制,对算法的数据结构、处理流程以及程序结构等进行优化,以提高Cache的命中率,更有效地发挥Cache的作用,从而达到提高解码器运行效率的目的。

2 基于Cache的视频解码算法实现

为了克服上述不足,本文通过更改视频解码算法的实现架构,充分利用Cache中L1P,减少CPU读取程序代码的缺失次数,提高解码程序的执行效率。

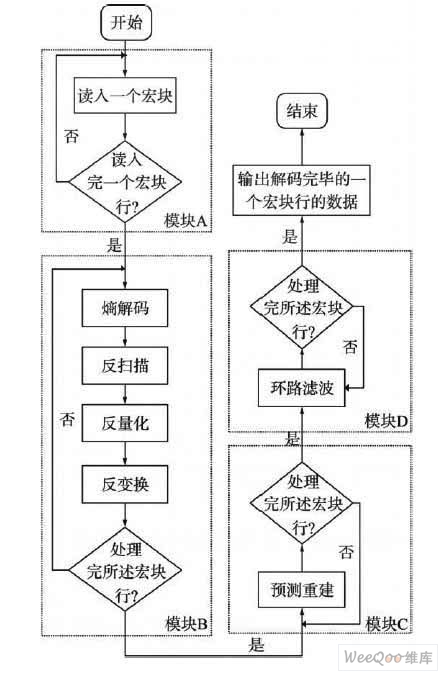

在具体实施过程中,本文根据L1P的容量和程序中各个功能单元代码的大小,将图2中的功能单元分为四个模块,每个模块代码大小均小于16 kbyte,各模块所包含的功能单元为:模块A,读入一个宏块;模块B,熵解码、反扫描、反量化、反变换;模块C,重建;模块D,环路滤波。

一个视频宏块只有遍历这四个模块之后才算最终完成解码,各个模块之间传递的中间数据如果放置在片外SDRAM中,势必影响下一个模块获取数据的速度,如果数据放置在片内SRAM中,由于片内RAM空间有限不能存储整帧数据。所以权衡考虑,每个模块完成一个宏块行(假设一幅图像包含有M个宏块行,每行有N个宏块)的解码后再交给下一个模块处理,这样既可以将中间数据放置在片内又可以充分利用L1P,减少各个模块之间的代码冲刷,直到M 个宏块行全部处理完毕,这样就得到一帧数据的解码图像。

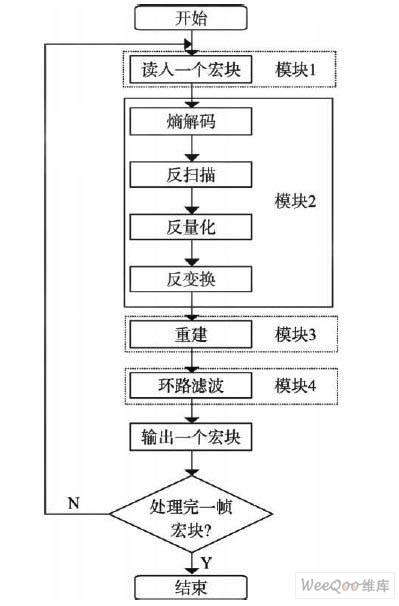

图2 解码算法流程

如图3所示,本文以一个宏块行为处理单位,在进行解码时,首先执行模块A将整个宏块行读入高图3 处理一个宏块行的新流程速缓存中,执行完毕模块A后,读入模块B的代码,该部分代码将会冲掉模块A 的代码。执行完毕模块B后,读入模块C的代码,该部分代码将会冲掉模块B 的代码。依此类推,当执行完毕模块D后,再重复执行以对下一个宏块行进行解码。

图3 处理一个宏块行的新流程

每个模块在执行一个宏块行的解码过程中,会被反复执行N 次,在此期间程序代码保留在L1P中不被冲刷,直到第二个模块执行的时候第一个模块的代码才被冲刷。所以此方法解码一个宏块行才发生四次冲刷,完成一帧图像的解码共发生4 ×M 次代码冲刷,较改进之前减少冲刷次数4 ×M ×(N - 1)。

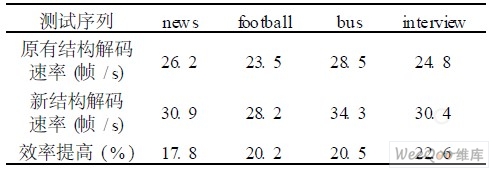

表1中的测试序列分辨率为720 ×576,调整结构后解码速率均有不同程度的提高,通过对统计结果的平均得知,效率提高20%左右。

表1 实验结果

3 结论

本文解码器优化充分利用了处理器的程序Cache功能,模块分配方式依据Cache大小而定,针对不同处理器的不同Cache, 可以有不同的模块划分方式,只需要保证每个模块代码量小于程序Cache容量即可。处理器对于数据的读取同样可以采用类似方法,以达到充分利用数据Cache的目的。此方法不仅可以应用于AVS解码器,也可应用于AVS编码器,还可以应用于与之拥有类似结构的H. 264、MPEG、VC1等编解码算法。