降低任何嵌入式设计的体积和成本的常用方法是使用具有较少I/O引脚的通信总线。虽然从并行总线发展到串行总线可明显减小体积和降低成本,但是从一种串行总线发展为另一种具有较少引脚的串行总线也很有用。用串行总线替代并行总线时,传输速度是一个关键参数。在小体积是最重要参数的设计中,使用具有较少引脚的串行总线很有优势。单片机集成超过12种不同的串行接口,本文将讨论各串行接口的优缺点。

个人计算机中的USB与FireWireTM

一种促使PC市场发生重大变化的流行总线就是通用串行总线(universal serial bus,USB)。它的高速度、低引脚数和多功能性促进了它的广泛使用,且USB逐渐取代了并行打印机和RS-232串口,成为PC的主要通信端口。USB2.0在节约系统成本方面也优于FireWireTM S400。此外,USB可利用PC资源依靠主处理器来管理低级别的USB协议,而FireWire将此任务委托给接口硬件。FireWire所需的额外硬件成本和初始许可费用使USB成为PC领域的首选接口。同样的原因也促使嵌入式应用纷纷迅速采用USB。

同步接口与异步接口

选择串行接口时,必须检查同步接口和异步接口。同步接口使用主时钟进行同步,而异步接口将时钟嵌入到数据流中。从器件时钟的频率变化不会影响同步接口的同步操作,因而可以使用低成本振荡器。在异步器件中,实现同步需要所有器件在传输速度、协议、重新同步频率和时钟稳定性方面达成一致。

同步接口可在同一印刷电路板(printed circuit board,PCB)上轻松实现器件间连接,而异步接口旨在通过电缆连接相隔数米至1000米的系统。应用范围从简单的点对点连接到具有数百个器件的复杂网络。也可以通过OSI模型描述每种总线类型的不同物理接口。

OSI七层模型

通常,同步接口在内部支持数据链路层(第2层)和物理层(第1层),而大部分异步接口在内部支持数据链路层在外部支持物理层。有时,异步接口也在内部支持这两层。对于某些应用,相同的数据链路层结合不同的物理层驱动程序来创建不同的接口标准。在单片机中,通常通过某些硬件支持在软件中实现第3至第7层。

从并行接口发展到串行接口

当系统软件需要大量存储器时,通常会选择具有外部地址和数据总线的单片机。并行闪存程序存储器和SRAM需要16个或更多I/O引脚,设计人员可选择使用具有内部存储器的单片机以节省I/O引脚、缩小体积和降低成本。虽然现在许多单片机程序存储器的容量都已有所提高,但如果内部存储容量还是不够的话,可采用使用SPI端口的外部闪存程序存储器或串行SRAM。

由于串行闪存程序存储器和串行SRAM器件只可通过SPI总线提供,所以选择此总线可获得最高效的系统设计。当某些元件只能通过某个特定总线连接时,这些元件决定了总线的选择,除非单线器件可提供更好的解决方案。

同步接口

• SPI

• MICROWIRE

• I2C™

• 通用串行异步收发器(universal serial asynchronous receiver transmitter,USART),同步和异步模式

总线选择所采用的标准:

1.元件只能通过一种总线提供

2. MCU上可用的总线:

a. SPI和I2C或同步串行端口(Synchronous Serial Port,SSP)

b.串行控制接口(SCI)

c. USART

d.具有软件驱动的GPI/O

e.其他网络总线

3.需要较快的总线速度

4.小尺寸的较低引脚数总线

5.推挽输出或漏极开路输出

6.系统总成本

7.提供的功能集

SPI总线支持的典型速度范围为5MHz至20MHz,但对于高速串行闪存程序存储器,还可支持高达75MHz的速度。Microwire总线在工作原理和连线数量上与SPI总线相似,但是总线规范将其通信速度限制为3MHz。

I2C总线具有时钟线和数据线,其可软件寻址且具有400kHz的典型工作速度,连接多个器件时速度可为1MHz。由于单片机I/O端口有限,故端口较少成为了该总线的最大优势。

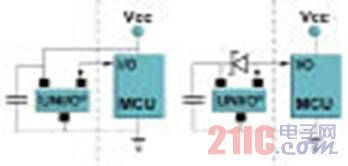

图1a 3引脚UNI/O总线连接 图1b 2引脚UNI/O总线连接

通常,SPI和Microwire总线使用4个I/O端口,而I2C总线使用2个I/O端口。小型化系统的下一步发展就是寻求更小的、使用单个I/O进行通信的总线。由于这种情况只能在将时钟嵌入到数据流中时实现,所以这些接口必须是异步接口。

异步接口

今天,有两种不同的异步总线竞争通常为同步总线预留的端口。这两种总线是1-Wire®总线(Maxim)和UNI/O®总线(Microchip Technology)。

1-Wire®总线上的器件采用2引脚封装,一个引脚用于接地,第二个引脚用于数据和电源连接。在1-Wire总线器件的设计中融入了电容,从而可从数据线获取寄生功率,采用漏极开路输出的电阻可获取高达16.3kbps的传输速度,而当该电阻值降至2.2kΩ时传输速度将增至142kbps。

UNI/O®总线是一种新的单线总线标准,采用3引脚封装,支持电源、地和数据连接。使用曼彻斯特编码进行通信,支持10kbps至100kbps的数据传输速度。虽然该总线旨在用于标准嵌入式设计,但通过添加一个外部肖特基二极管并调整旁路电容的值,可使其用于具有2引脚接口的应用中。图1a和1b中的框图充分说明了此解决方案如此简单。

UART为最早且占据主导地位的异步接口,而在需要同步和异步模式时还称为USART。再回到OSI模型,单片机的片内UART实现了数据链路层,而物理层受制于几个驱动标准。这些标准中最常用的是RS-232C、RS-422和RS-485接口。

还有一些具有异步接口的特殊单片机,旨在用于网络连接,如以太网、CAN、LIN和MIDI。表1汇总了各种串行接口及其特性。

表1:各种串行接口汇总

结论

在选择最佳的串行接口时,应检查系统设计以获得最低成本解决方案。许多情况下,最低成本的元件并不会提供最低成本的系统。随着系统规模的继续缩小,单线总线外部存储器可以在对单片机资源或外部连接器产生较小影响的情况下提供最低的系统总成本。