摘要:介绍一种基于SOPC的基本信号产生器的设计技术,以Altera公司EP1C6Q240C8为硬件核心,把软核CPU嵌入到FPGA之中构成片上系统(SOPC),并结合存储电路、高速DAC电路、LCD电路、键盘电路、JTAG配置电路以及电源电路等进行了硬件电路的设计,以此实现基本信号产生器。阐述了各主要模块设计方案,并给出软硬件测试图。通过示波器观察,满足了系统设计要求,达到预期目标。

关键词:FPGA;SOPC;Nios II;DDS;基本信号产生器

SOPC是以PLD取代ASIC,更加灵活、高效的SOC解决方案。SOPC的设计是通过以IP核为基础、以硬件描述语言为主的设计手段,并借助于以计算机为平台的EDA工具进行的。它代表一种新型的系统设计技术,也是一种软硬件协同设计技术。可以方便地将硬件系统与常规软件集成在单一可编程芯片中。它可编程的灵活性和IP设计的重用性保证了产品的差异性,并缩短面市时间,也无需库存和一次性投片费用,降低了投资风险。所以相对于ASIC具有独特的优势,与ASIC一起形成共存互补的局面。

1 系统设计方案

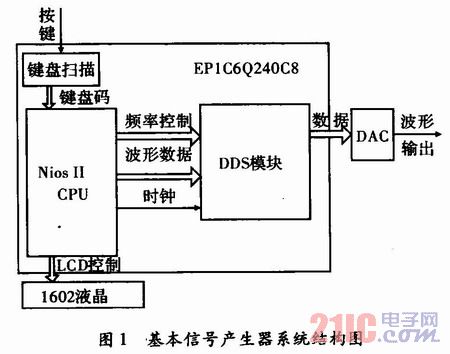

本系统采用以EP1C6Q240C8为核心的设计方案,如图1所示。

方案利用了FPGA优秀的集成特性,把Nios IICPU模块、DDS模块、4×4键盘扫描模块等集成在FPGA上实现,外部只接少量的电源模块、DAC模块以及其他输入输出设备。把传统的完全基于硬件的大部分工作转换成在PC机上通过软件设计编程来实现,减小了系统设计的复杂性。

工作原理如图1所示。外接4×4键盘根据1602液晶显示,通过FPGA的键盘扫描模块向NiosⅡCPU发送键盘扫描码,NiosII CPU根据接收到的扫描码产生相应的信号数据以及控制信号,并通过PIO传送给FPGA中的DDS模块,之后DAC器件将DDS产生的8位信号数据进行数模转换,从而产生任意频率的方波、三角波、正弦波。

2 系统实现

本系统实现主要分3个层次:电路板级设计、FPGA硬件设计以及Nios II软件程序设计。

2.1 电路板级

在电路板级设计中,采用Altera公司的EP1C6Q240C8作为设计核心,如图3所示。由于FPGA配置数据掉电后会丢失,所以需要另外搭配一个配置芯片。EPCS1是Altera的专用配置芯片,专门用于存贮对FPGA的配置数据,以保证在FPGA掉电后还能够保存配置信息,再次上电时FPGA芯片会自动从EPCS1中读取数据进行配置。

为了便于功能更新以及扩展,在FPGA外加上Flash、SRAM和SDRAM作为FPGA的程序和数据存储器的扩展,地址线通过EXT_ADDR引出,数据线通过EXT_DATA引出,增加电路的扩展性。

FPGA中DDS模块的双口RAM中输出的数据为8位数字信号,只有通过DAC转换电路才能将数据转换成相应的模拟信号。综合分辨力、转换速度以及接口方式等要求,本设计采用ADI公司的AD9708作为系统DAC器件。AD9708的数据线和时钟线与FPGA的I/O脚连接。AD9708的数字地和模拟地在片内是独立的,应通过外部引脚将其连接在一起。同样,模拟电源和数字电源在内部也是独立的,为了减少来自数字电源的噪声,可在模拟电源输入端串联一个磁珠再与数字电源连在一起。

2.2 FPGA硬件设计

FPGA硬件设计是建立在电路板设计基础上的对FPGA芯片功能的设计,将一些可以在电路板上实现的功能在FPGA内部通过采用硬件描述语言或搭建模块的方式来实现,减少了上层设计的工作量以及系统硬件的风险。通常本层设计是通过通用计算机平台上的可视化编程软件实现的,本设计采用Altera公司的Quartus II 8.1系列设计工具。

2.2.1 DDS模块设计

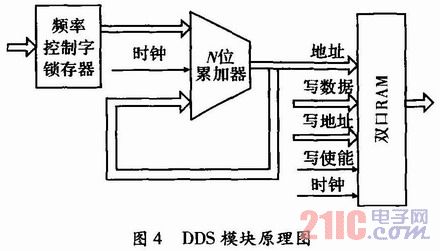

如图4所示,频率控制字锁存器保存频率设置字M。双口RAM的写地址、写数据以及写使能端口完成对RAM中1 024 Byte数据的更新,N位累加器输出结果的高10位作为双口RAM的读地址。在系统时钟fclk的作用下累加器根据频率控制字M输出连续变化或跳跃变化的地址,双口RAM循环输出相应地址单元中的8位数据,此8位数据接到DAC输入口。

假设双口RAM中存放一个周期的正弦信号数据,那么此时DAC输出的正弦信号的频率fout=fclk×M/2N,同理,当双口RAM中存放的是方波或者三角波数据时,DAC也会输出相应频率的信号。

模块中32位频率控制字锁存器,是用VerilogHDL语言实现的,并生成自定义模块以供上层原理图调用。N位累加器和双口RAM是利用Quar-tus II8.1中的MegaWizard Plug-IN manager定制实现。

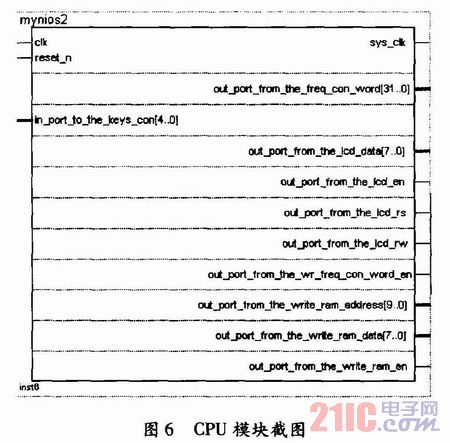

2.2.2 定制Nios II CPU

32位的Nios II软核是该基本信号发生器的核心模块,主要用于人机界面的控制、键盘值的读取以及控制DDS模块输出信号的频率和样式。

如图1所示,CPU与外围设备之间要添加相应的外围接口,通过Avalon总线与相关部件相连,通过Avalon的读写时序对各个设备进行操作。在SOPCBuilder中可以提供众多IP核,通过定制即可完成相应系统的设计。

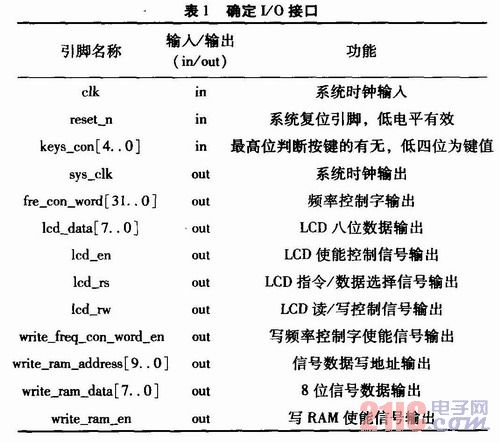

在软核定制过程中,I/O接口设计充分体现了软核设计的可裁减优势,根据系统设计的要求,任意改变IO口的个数和类型,使用方便。根据本设计功能的要求,确定IO口如表1所示。

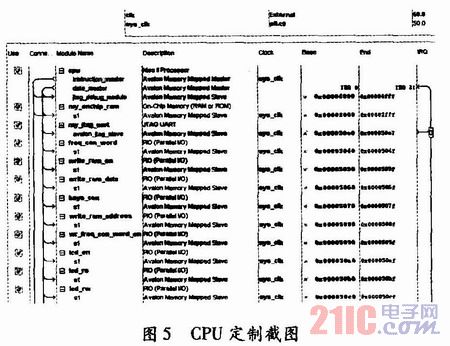

为了使该基本信号产生器系统更加简化,没有扩展Flash存储器以及SRAM存储器,而采用EPCS1和FPGA内的RAM来代替。EP1C6Q240C8的RAM容量为92 160 bit,在配置时分配空间的大小因程序的大小而定,做到资源的充分合理应用。根据以上分析需要加入的组件有:NiosII CPU Core(CPU核)、片上存储器以及PIO。配置完成后将会生成如图5所示定制的CPU配置表。点击Generate生成模块,其模块如图6所示。

2.3 Nios II软件程序设计

在系统软件设计阶段,采用的开发工具是Nios IIIDE,它是Nios II系列嵌入式处理器的基本软件开发工具。所有软件开发任务都可以在Nios II IDE下完成,包括编辑、编译、调试和下载。

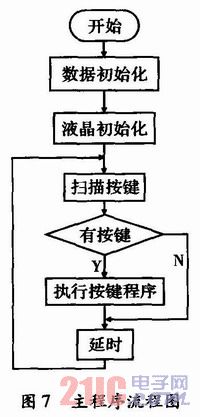

本程序实现的主要过程是:系统接收键盘扫描模块发来的5位扫描码,判断键盘是否按下以及按下的键,根据按键的不同进入不同的子程序以实现LCD显示、频率控制字的写入、信号数据的生成以及将其写入双口RAM。

主程序流程如图7所示。

3 软硬件测试

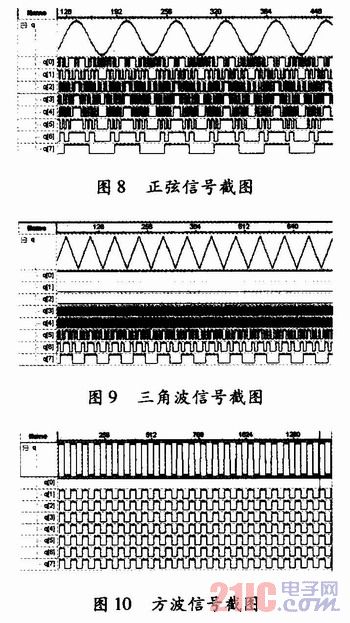

(1)在RAM中加入方波、三角波以及正弦波数据,并设定频率控制字为0x003fffff。采用Quartus II8.1的嵌入式逻辑分析仪。Signal-TapII Logic Analyzer观看双口RAM输出q[7..0],截图如图8所示。

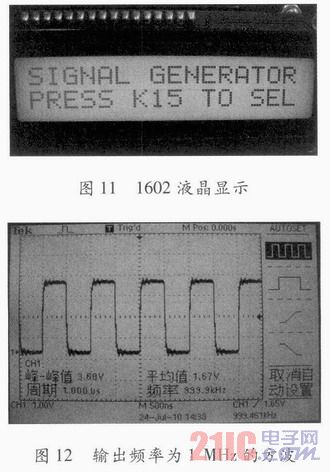

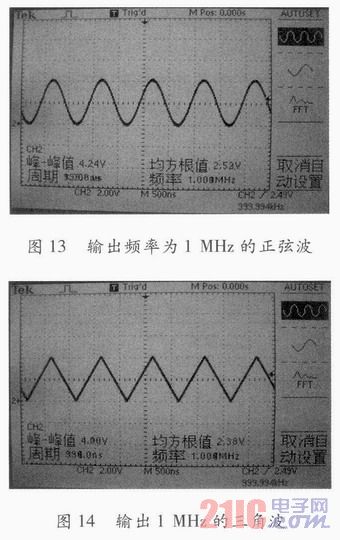

(2)通过AS下载接口将硬件编程文件下载到EPCS1中,采用NiosⅡIDE通过JTAG接口运行软件程序。通过键盘设置正弦波、方波以及三角波及其频率值输出,并且在1602液晶上显示相应的提示信息,如图11所示。

4 结束语

采用人机界面交互方式进行信号选择、频率设置等,Nios II CPU通过判断键盘输入在LCD上给出相应的显示,提示用户选择相应的按键,输入完毕后,CPU将产生的信号数据和频率控制字传送给双口RAM和频率控制字锁存器,最后在DAC输出端输出相应模拟信号。通过示波器观察所产生的正弦波、方波以及三角波,达到了预期的目标,满足了系统设计要求。