芯片设计的奥林匹克观感-ISSCC2016参会纪实(二)

3赞承蒙师姐和网站各位编辑的推荐,连载的第一部分被今天头条转载了,然后又被若干的大媒体公众号之类的转载。但是我发现一个问题就是转载的时候他们就只转了文章的主体,作者信息、版权声明什么的都没有。所以我后面的博文在开头都要先加版权声明了。

版权声明:

本文由电子技术应用博主“老莫”发布。欢迎转载,但是不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和作者单位简介。以下引用的图片版权归原作者,我在引用时已经说明了出处。请勿盗用。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

作者简介:黄乐天,电子科技大学集成系统实验室青年教师,网名“老莫",电子科技大学网络名师,《FPGA异构计算》一书作者。主要研究领域为计算机机系统结构与片上系统设计、混合信号集成电路设计与模拟计算技术,博客官方地址:http://blog.chinaaet.com/molf

作者单位简介:电子科技大学集成系统实验室是电子科技大学从事系统级芯片设计主要科研团队,在电子科技大学历史上创造了多个“首次”。实验室主要研究方向为:研究方向包括模拟与数模混合集成电路、射频IC、计算机系统结构与大规模集成电路设计等。首页:http://www.me.uestc.edu.cn/team/viewTeam?id=27

本次主要介绍ISSCC session 4:Digital Processors的一些情况。

首先说一下和2015的一个重大区别,Multi-Core is dying。在2015年ISSCC的时候,大家都还在拿多核说事。分别在秀自己的处理器上有10多个核,核间怎么通信的,怎么构成一个大的计算机系统。专门谈能效优化的就甲骨文的一篇:Fine Grained Adaptive Power Management of the SPARC M7 Processor,还是在前一篇:A 20nm 32-Core 64MB L3 Cache SPARC M7 Processor基础上谈的。AMD算有半篇,他们在ISSCC2015上发表的:A 28nm x86 APU Optimized for Low Power and Area Efficiency里面大概有一半在谈如何降低功耗。而今年,却连一篇以Multi-core为主要卖点的论文也找不见了。反而大家纷纷都出来谈如何降低能耗,提高能效的问题。

这个session开篇就是Intel的:14nm 6th Generation Core Processor SOC with Low-Power Consumption

and Improved Performance,由Intel公司在以色列海法的小组发表(该小组当年成功攻克多核技术,在AMD唯一一次差点逆袭Intel的战役中稳住了Intel的基本盘)。这不是一个简单的CPU或者处理器,而是包含了GPU、IPU(Image processing unit 图像处理器单元)的一颗SoC。接下来他们用了大概一半的时间在介绍电源和时钟管理两部分,这是整个文章的亮点。包括如何真正的实现Power Gating技术,如何设计一个数字化支持频率可调的PLL,如何分配时钟网络。总而言之就是真正的把计算机系统结构届吹嘘了很多年的Pre-Core DVFS去落到实处,真正让片上的多个核心能够独立的调频调压。接下来用了一个具体的视频播放的例子来验证能效优化的结果。与上一代同样用14nm的处理器相比,功耗节约了45%。其中21%属于硬件优化的效果,24%是面向视频播放应用的优化。

第二篇是AMD的文章: Increasing the Performance of a 28nm x86-64 Microprocessor Through System Power Management;从这题目就可以看出来,这是一个讲28nm下X86处理器(哎,Intel讲的是14nm哦……这AMD差距的差距啊!)如何通过功耗管理来改善性能的问题。这其实也是一个SoC,包含了双核CPU、GPU、南北桥、DDR控制器+PHY。这篇文章首先提出可以依靠AVFS(Adaptive Voltage and Frequency Scaling)来逼近时钟频率的极限。然后指出做电压和频率调节要考虑到可靠性的问题而不能瞎调。可靠性具体的限制就是如果温度高电压也高的话,芯片失效的概率就会大大增加。如果温度低一些,那么电压可以搞高一些失效概率也还好。我个人觉得这个地方其实有点纠结。对于一个已经完成的设计,如果外部散热的能力一定(风扇or散热片),那么温度实际上和电压是完全正相关的(另外还取决于布局和功率密度)。不过文章的结论很有趣,就是说在考虑到生命周期内(lifetime)芯片本身的容错能力,其实我们可以让电压搞高一点(这样频率也可以高一点了),只要我们确保老化速度不要太快导致芯片的生命周期提前结束。其后重点介绍了DVR(Dynamic Voltage Regulation)模块,包括了电压调节和处理器内部管理两部分。通过关闭/旁路处理器内部的某些功能(如分支预测之类的)可以让电压维持在比较低的状态。后续又讲了一个叫STAPM (Skin Temperature Aware Power Management) 的技术,其核心就是在一开始温度还没有达到温度限制之前,可以先“放肆”的用比较高的电压和频率疯跑一阵,等到温度限制到了就得限制电压和频率以防温度“过线”。其后还要靠 Boot Time Power Supply Calibration(BTC)来校准一下在一开始能达到的最佳电压和时钟频率。最终,这些技术都用上了以后,APU综合性能有10%-15%的改善。我个人觉得这篇文章最大的亮点不在于这些技术如何如何,有意思的是AMD提出一个观点是在生命周期内应该尽量的使用芯片,没有必要很保守的维持在低电压/低性能的状态。所以这果然是延续了AMD一贯的“超频”思路,反正现在消费类电子更新的频率那么高,合理的加压加频物尽其用,也不是不可以……这也给我们做容错设计的人一个新的思路:容错其实不但是延长寿命的,也可以用来提高性能,有了容错设计以后就更加“放肆”的提升性能了。

前面两篇论文讲的说起来有点生僻,不是人民群众喜闻乐见的内容。接下来我们就讲一篇比较通俗一点的,就是联发科发表的这篇:A 20nm 2.5GHz Ultra-Low-Power Tri-Cluster CPU Subsystem with Adaptive Power Allocation for Optimal Mobile SoC Performance。从名字里有Tri-Cluster CPU Subsystem就可以看出这是一个多核处理器,分了3个Cluster。其实这就是这么多年大家一直炒作的大小核。这三个Cluster分别是两个2.5GHzA72一组(HP)、四个低速2.0GHzA53一组(LP)、四个超低速1.4GHzA53一组(ULP)。除此之外包括GPU、多媒体系统(其实就是摄像头及其配套硬件)、802.11ac、GPS、Modem(支持LTE-A、HSPA+、TD-SCDMA……等若干制式)。

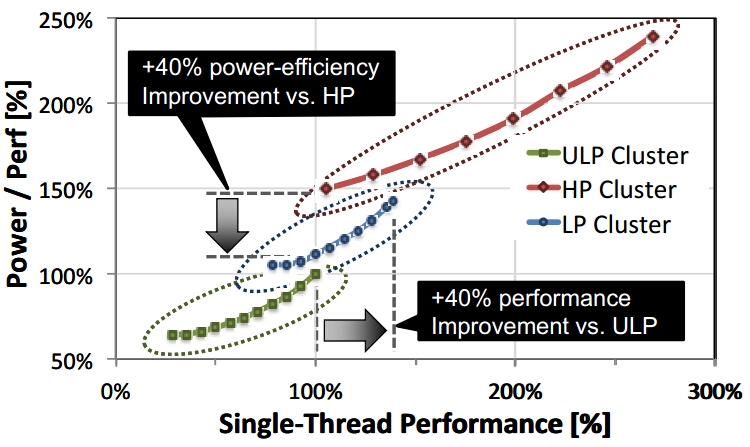

那么为什么需要分组呢?是不是大家闲得蛋疼了没事干啊?其实不是的,这时候我需要上一张图:

不知道各位看官看明白了没有。其实这三组CPU是针对不同目标来进行优化的。上图的横坐标是单线程性能,纵坐标是功耗除以性能。看以看出,这图上的有三个曲线,分别对应ULP、LP和HP。这三个曲线其实是不连续的。可以看出,ULP的性能和功耗比是最佳的,但是其上升空间有限,最高性能突破不了。而LP呢?功耗性能比要大那么一点点,但是性能的上线可以比ULP高40%。而相比于采用HP直接降频降压,LP可以最多节约40%的功耗(最少的部分看起来有10%几?)由于这种功耗和性能上的对应关系,使得三个组有明确的分工。

大概的分类是这样的:

看上去很有趣的样子吧?

但是只有这样的分类还是不够的,要如何确定CPu的功耗是在曲线的哪个位置呢?这个就需要利用

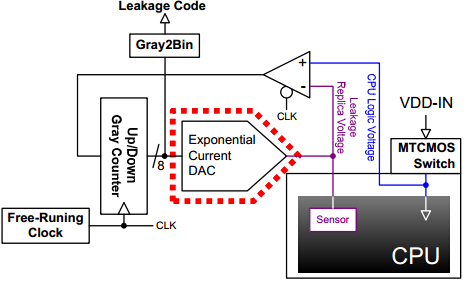

Adaptive Power Allocation (APA)这套技术了。实现这套技术的前提是做功耗估计。这里面用了一些篇幅来谈如何校准动态功耗估计使得其和实际的功耗相符合。而对于静态功耗估计,就要靠传感器来感知电流。其主要的问题是电路这玩意啊,和PVT(工艺、电压、温度)的变化关系太大了。按这篇论文来看,最小的漏电流和最大的比都快差出去2000多倍了(很吃惊吧,其实我也是。但论文里就是这么写的)。这电流传感器的作用就在于,如果我往里面注入恒定的电流,传感器等效出来的两端电压是否已经等于CPU的上的实际电压。具体的图是这样的:

通过DAC产生电流,灌入sensor上。然后比较限制sensor上的电压到了CPU的供电电压了没有。现在电流的大小,也就等于CPU上漏电流的大小。而DAC的输入,就是当前的漏电流的值。这是一个很有趣的设计,为了减少DAC的位数,图中的DAC采取的是非均匀量化。

最后为了检测电源供电网络实际的变化,这个论文还讨论一个叫SupplEyeScan的技术,其核心就是在芯片规模已经很大,封装、电路设计都比较复杂的时候,监控电源供电网络上电压的抖动和变化。核心是用了一个类似于SAR ADC的方法做的,控制逻辑也还有点复杂,这里就不细讲了。

好了,今天的内容大概就讲到这里,未来我大概准备一周一更的速度慢慢来和大家分享,每次分享的内容根据情况而定(看我的心情和状态而定),我们下期再见。

再次提醒大家转发时不得删除版权声明部分!