(转)FPGA从Xilinx 的7系列学起(5)

0赞

2. 最基本的BlockRAM

2.1 BlockRAM的初探

BlockRAM资源对FPGA来说也是非常重要的,我们的很多设计用到了BlockRAM以后,可以变得设计非常灵活,这样我们就可以设计出很多高效能的应用。了解BlockRAM的一些情况,对我们来说也是一个很重要的事情。

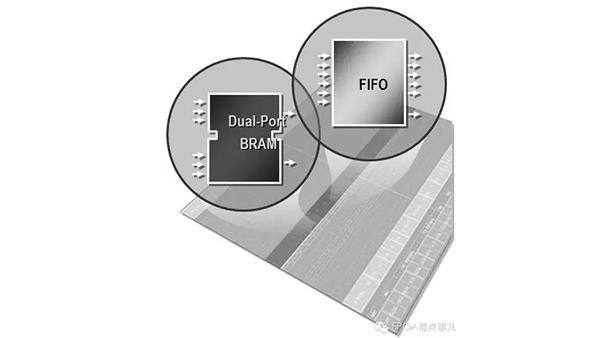

大家都知道,每个FPGA设计需要一定的内存资源。一般来说,相对于DDR来说小一点的空间,我们都是通过频繁调用的块RAM实现的。所有7系列的FPGA都具有相同架构的BlockRAM,每一块BlockRAM是36KB大小的真正的双端口存储器,经常被我们用来构建FIFO,大量的数据存储以及有限状态机,同时7系列有专用硬件,可以将BlockRAM转换成FIFO,供大家在设计的时候使用。

因为7系列器件具有相同的BlockRAM资源,这使得我们的设计能够快速的在7系列之间切换。他们和Virtex-6使用了相同的RAM资源,这样我们也可以方便的把Virtex-6中的设计升级到7系列中。

7系列的BlockRAM的时钟频率可以达到600MHz,这种结构包括输出寄存器,让更快的输出时钟速度,但是,对不起,它会增加延迟。每个RAM块具有独立的读和写端口、宽度,每个端口具有它自己的时钟和不同的读写位宽比例。 XILINX的Block RAM中包括一个可配置的端口位宽长宽比功能,这样做的好处,就是允许每个Block RAM端口有一个自定义的位宽。这有助于用户使用BlockRAM实现更多的应用,而不是需要我们在BRAM外作额外的逻辑来处理位宽差异,增强了用户的使用效率。举一个简单的例子,用户给端口A可以写数据,并且按照字节加上使用的奇偶校验位,那么用户可以从端口A读出的数据不带任何校验信息,但是从B端口,用户可以选择位宽16位,但是带2位的奇偶校验,也可用选择位宽32位,但是带4位的奇偶校验位。基本上,未来用户使用BlockRAM的时候会使用到有很多关于这方面的配置比例问题,以及如何配置用户的端口宽度的灵活性。每块XILINX的BlockRAM都可以用作真双端口存储器,简单双端口或单端口配置,这个在生成IP核的时候会遇到。

BlockRAM也可级联的,这意味着它们可以被连接在一起,形成更大的存储空间(包括BlockRAM,也包括FIFO)。和Virtex-6的BlockRAM类似,7系列的BlockRAM也有一个字节写使能信号,这对那些要使用MicroBlaze的用户来说,他们可以在比特流配置过程中初始化块存储器内容。那么,如果用户在运行复位时,仅仅只能复位就寄存器的内容,而不能复位BlockRAM的内容。当然,只要用户想要复位存储器的内容,只要重新写入新的数据即可。

和Virtex-6一样,7系列的BlockRAM有ECC功能能够修正错误的bit信息。这是专门的硬件电路来实现的,不需要用户进行相关逻辑代码来实现。另外,7系列的BlockRAM和Virtex-6的不同在于,7系列需要专门的电源来给BlockRAM提供电源。如果用户使用7系列的-1L速度等级,要注意正确的操作,-1L的核心电压有所降低,但是BlockRAM的供电需求没有降低。没有使用的BlockRAM通过配置比特流自动断电,这减小了FPGA总功率,这一点在追求低功耗的应用上,考虑使用。

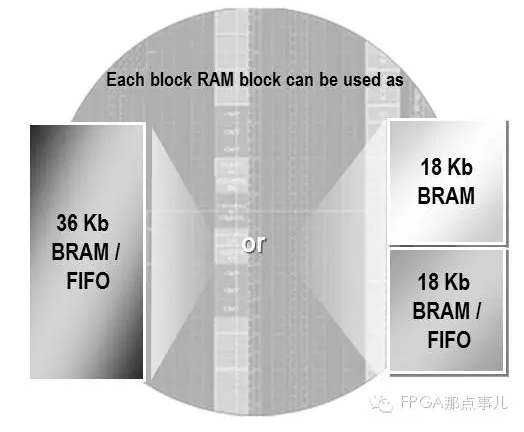

每块7系列的BlockRAM大小为36Kb的,但是允许每个BlockRAM块被分割成2个18Kb存储空间。但是18Kb的存储块不能被进一步分割。这样就保证了BlockRAM的有效使用,也增加了灵活性。这个功能非常有意思,因为它能够保证你不会浪费你的BlockRAM存储器,让你享受到仿佛更多的存储空间,用户可以用它来传递不同时钟域的数据,可以用来作为FIFO, 至于怎么用,用户可以根据需求雕琢一下即可。

用户只要想把FPGA功能发挥到极致,建议必须考好考虑XILINX给提供的这个功能。这一点与Spartan-6和Virtex-6不同,用户使用时要注意。

2.2 7系列BlockRAM资源的小结

对7系列的FPGA的BlockRAM做一个简单的总结:

7系列都具有相同的BlockRAM架构;可以实现完全同步操作,所有输出锁存;可选内部流水线寄存器,提高工作频率;两个独立的端口访问存储数据,包括独立的地址,时钟,写使能,时钟使能,独立的数据宽度;IP核配置时,有多个配置选项:真正的双端口,简单双端口,单端口;可以级联,生成更大的存储空间;按照字节使能;专用电路高效配置电路;具有ECC功能;独立Vbram供电,但是要注意-1L BlockRAM存储器供电电源的使用。