【转】iTop4412时钟配置

0赞

发表于 2016/11/5 10:38:25

阅读(1091)

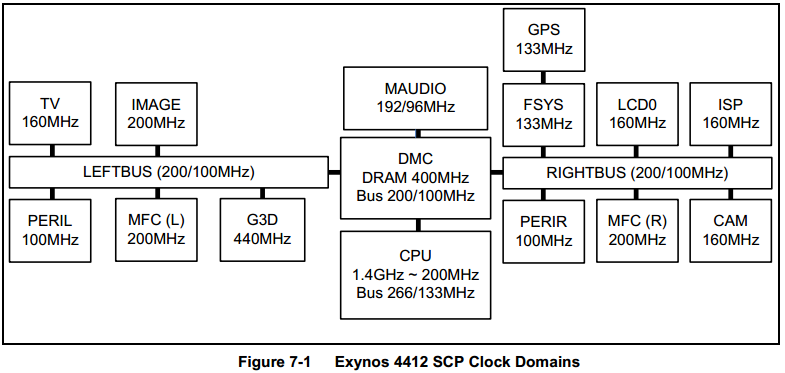

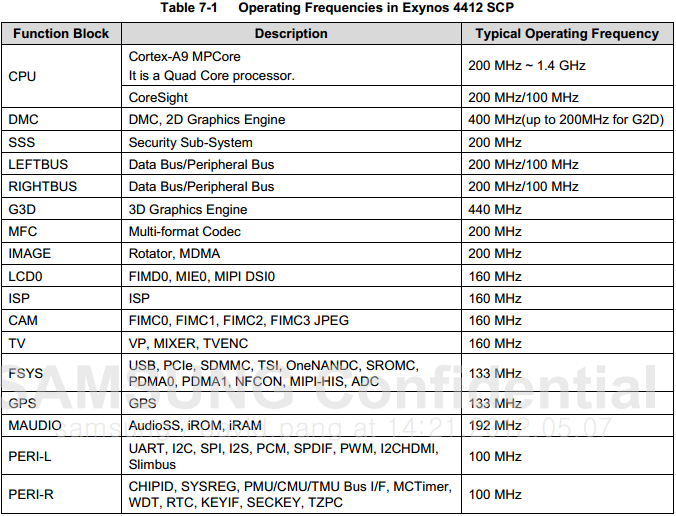

Exynos4412时钟域分类图1:

引用humaoxiao的博文:http://www.cnblogs.com/humaoxiao/p/4225320.html

本文解决的问题:

1、宏观上几个大模块的时钟配置顺序。

2、小模块的时钟选择、分频和一般的配置顺序。

3、对小模块来说,官方手册推荐的时钟源选择问题。

4、本文只以手册的“推荐配置”进行说明,“自由玩法”不保证稳定性。

多路选择器选择原则:

1、尽量保持默认配置不动。

2、尽量选择前端频率最高的源。

3、其它手册要求的特殊情况。

几个符号:

左边深色的:无抖动多路选择器,无抖动意味着在多路选择切换的瞬间,下游时钟就可以稳定下来。需要注意是在切换时要保证上游时钟已经存在并稳定,不然下游时钟状态不确定。

右边浅色的:有抖动多路选择器,意味着多路选择切换后,要经历一段时间的不稳定时间,但是有稳定后有相应寄存器标志位标示下游时钟已经稳定,这类指示寄存器器一般以CLK_MUX_STAT开头。

全局约束条件:

1、无抖动多路选择器的时钟源需要存在并且稳定。

2、当某个PLL被设置为关闭状态,是不可以使用它的输出信号的。

晶振说明:

由于一般USB IP核需要直接使用高精度时钟,所以在XUSBXTI引脚上接24M晶振,XXTI引脚就不需要接了。手册上说由于iROM代码是根据24M晶振频率设计的,所以24M的选择没什么好说的。