【转】ARM学习篇 SDRAM理解

0赞1.SDRAM单管存储单元

- SDRAM单管电路图

C记忆单元

T控制门管

Z字线

W位线

注:图示为N沟道耗尽型MOS管

- 写入:Z加高电平,MOS导通,W状态决定了电容C的状态

- 读出:Z加高电平,MOS导通,可以从W状态得知C的状态

- 保持:Z加低电平,MOS关闭,电容保持原状态

- 注意:单管读出是破坏性读出,因为读出时电容充电或者放电了,所以读出后还要重写

2. 刷新与重写

● 刷新是每隔一段时间,自动重写一次;重写是破坏性读出后立即还原

- 最大刷新间隔:所有的动态单元都被重新刷一遍的时间

- 刷新周期:刷新一行所用时间

- 刷新周期数:刷新一块芯片所用的刷新周期数

- 刷新周期的安排方式:

a). 集中刷新

b). 分散刷新

c). 异步刷新

2. SDRAM寻址机制

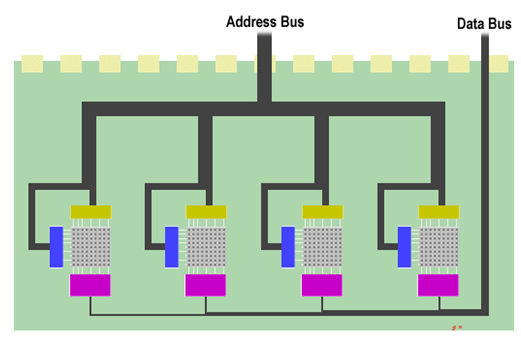

1. 地址分布逻辑图

图示大致说明了寻址方式,地址总线发出行列地址,选中相应的芯片,再读写。

2. K4S561632E功能模块图(SDRAM芯片)

● CLK系统时钟

● CKE时钟使能

● A0~A12地址线

● BA0~BA1块选择

● RAS'列信号使能

● CAS'行信号使能

● WE'写信号使能

● DQM控制数据输入输出

● Vdd/Vss供电电源/地

● Vddq/Vssq数据输出供电/地

3. SDRAM时序图

1.片选信号时序图

● Tacs:片选信号nGCSn起效前,地址信号建立时间

● Tcos:在nOE起效前,片选信号建立时间

● Tacc:访问周期

● Tcoh:nOE结束后(即电平升高),片选保持时间

● Tcah:nGCSn结束后(即电平升高),地址信号保持时间

● Tacp:Page模式的访问周期

● 前面介绍了图示一些术语,有了一定了解,下面我们来分析上图:

存储控制器使用HCLK作为其时钟

CPU要访问某个地址,先发出地址给MMU,MMU再控制地址线,分批次发送行列地址。

Page模式可以暂时忽略,因为我们还没用到离散存储管理(即物理内存分块,虚拟内存分页)。

● Trp:SDRAM RAS预充电时间

● Tsrc:SDRAM半行周期时间

● Tcas:SDRAM列地址建立时间

关闭上一次操作,对上一次读的行全部重写一遍,即预充电;

S3C2440A发出片选,块选(BANK)信号同时发出列地址;

选中行后,发出列地址,读出相应数据,延迟几个时钟周期,I/O端口上就会出现所读数据

4. 寄存器

总线/位宽等待寄存器BWSCON

总线控制寄存器BANKCON0~BANKCON5

总线控制寄存器BANKCON6/7

SDRAM刷新控制寄存器

BANKSIZE寄存器

SDRAM模式寄存器

5.寄存器配置(重点理解,我花了很长时间找资料、学习)

a. 操作参数

注意看参数,相信大家这点英文基础还是有的。

S3C2440A的存储控制器的nGCSn、地址信号、nOE信号几乎同时发出,所以这些参数都设置为0

访问周期,根据手册,几纳秒内就可以访问到数据,所以可以尽量调低。

RAS到CAS延时:3CLK(Col. address to col. address delay+Last data in to new col. address delay+行选通信号到列选通信号的延时=3clk)

列地址:9位

预充电时间:20ns左右

行周期:65ns左右

CAS潜伏期:2或者3CLK

6. 基于以上了解,我们终于可以写代码

AREA SDRAM,CODE,READONLY

CODE32

ENTRY

SDRAM_BASE EQU 0X30000000

WTCON EQU 0X53000000;看门狗控制寄存器

BWSCON EQU 0X48000000

BANKCON0 EQU 0X48000004

BANKCON1 EQU 0X48000008

BANKCON2 EQU 0X4800000C

BANKCON3 EQU 0X48000010

BANKCON4 EQU 0X48000014

BANKCON5 EQU 0X48000018

BANKCON6 EQU 0X4800001C

BANKCON7 EQU 0X48000020

REFRESH EQU 0X48000024

BANKSIZE EQU 0X48000028

MRSRB6 EQU 0X4800002C

MRSRB7 EQU 0X48000030

;定义SDRAM相关寄存器

GPFCON EQU 0x56000050

GPFDAT EQU 0x56000054

GPFUP EQU 0x56000058

;定义GPIO端口

_ENTRY

B RESET

B .

B .

B .

B .

B .

B .;0X18

B .

RESET

LDR R0,=WTCON

LDR R1,=0

STR R1,[R0]

LDR R0,=GPFCON

LDR R1,=0X5555

STR R1,[R0]

LDR R0,=GPFUP

LDR R1,=0XFF

STR R1,[R0]

LDR R0,=GPFDAT

LDR R1,=0X5F

STR R1,[R0]

LDR R0,=BWSCON

LDR R1,=0X22011110

STR R1,[R0]

LDR R0,=BANKCON0

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON1

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON2

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON3

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON4

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON5

LDR R1,=0X00000700

STR R1,[R0]

LDR R0,=BANKCON6

LDR R1,=0X00018005

STR R1,[R0]

LDR R0,=BANKCON7

LDR R1,=0X00018005

STR R1,[R0]

LDR R0,=REFRESH

LDR R1,=0X008C07A3

STR R1,[R0]

LDR R0,=BANKSIZE

LDR R1,=0X000000B1

STR R1,[R0]

LDR R0,=MRSRB6

LDR R1,=0X00000030

STR R1,[R0]

LDR R0,=MRSRB7

LDR R1,=0X00000030

STR R1,[R0]

;设置SDRAM相关寄存器

LDR R0,=0X0

LDR R1,=SDRAM_BASE

LDR R2,=4096

COPY_LOOP

LDR R3,[R0],#4

STR R3,[R1],#4

CMP R0,R2

BNE COPY_LOOP

;复制相关0~4kB的代码到0x30000000开始的空间

LDR R0,=0X30000000

LDR R1,=ON_SDRAM

ADD R2,R0,R1

MOV PC,R2

ON_SDRAM

LDR R0,=GPFDAT

LDR R1,=0X3F

STR R1,[R0]

;点灯

LDR R0,=0X30000000

LDR R1,=ON_SDRAM

ADD R2,R0,R1

MOV PC,R2

END