组合逻辑中的竞争与险象问题(一)

0赞针对单输出的组合逻辑进行简单分析,而多输出的组合逻辑可分解为多个单输出的组合逻辑。

单输入的组合逻辑

对于一个简单的非门电路,它的输出将永远跟随输入变化,即使考虑到门延迟、线延迟的影响,输出波形最多也就是比输入波形在时间上滞后一些罢了,并不会出现非预期的现象。

但对于单输入的组合逻辑,情况就不一样了。

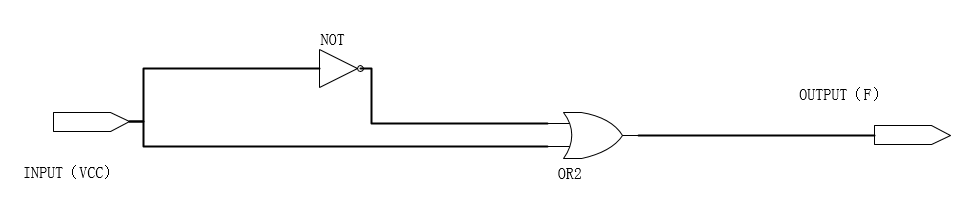

如下图:

输入为A先于not(A)A非到达或门,因此,如果初始令A为1,则NOT(A)为0,之后A变化为0,则由于A先到或门,导致有一小段零脉冲出现在输出中,这是非预期的。

当然,没人会无聊到设计这样的一个电路,但这个电路能说明一些大问题,后面我们会看到,但输入组合逻辑会产生竞争现象也被用来说明问题。

多输入组合逻辑

1 多个输入不同时变化

2 多个输入同时变化

3 仅有一个输入变化

1 多个输入不同时变化

若多个输入变化的间隔比较大,那么可以将其分解为若干个时刻,每个时刻有“多个输入同时变化”,“仅有一个输入变化”,然后再独立分析各个时刻即可;若这些输入变化间隔较小,那么可以将其等效转化为“多个输入同时变化”的问题,因为我们可以将这些输入变化的时间差等效折合到传输路径中的线延迟中去。

2多个输入同时变化

在多输入组合电路中,有两个及以上个输入变量同时发生了变化,虽然从输入决定输出的理论出发,组合逻辑的输出应该直接变化到新输入对应的输出值,但是由于延迟的存在,现实中情况往往并非如此。

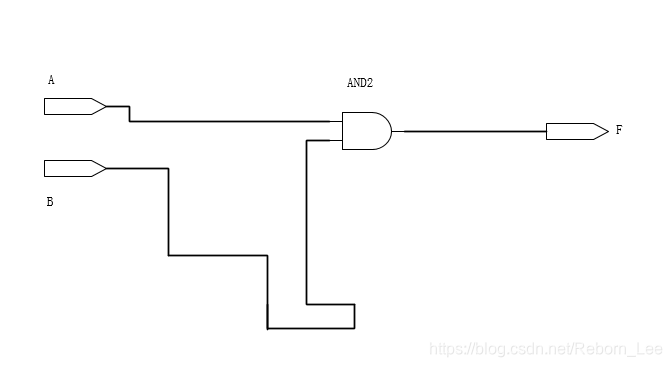

仅以下图为例:

由于路径延迟不一致,所以多个输入(A和B)同时变化时,到达与门的时刻也不一致,所以会导致有非预期的输出出现,那卡诺图来分析问题:

| F | A = 0 | A = 1 |

| B = 0 | 0 | 0 |

| B = 1 | 0 | 1 |

初始值A 为0,B为1,则F位于左下角,变化后A为1,B为0,F位于右上角,由于A的变化先于B到达与门,故有一小段时间F为1,也就是F从左下角右移了一格,之后上移一格到目的地。

从这个卡诺图中我们还可以看到,如果初始值A为1,B为0,那么A和B同时变化到A为0,B为1,会不会出现非预期的值呢?

不会,因为A的变化先到达与门,所以F先左移一格,仍然是0,再下移一格,还是0.

3 仅有一个输入变化

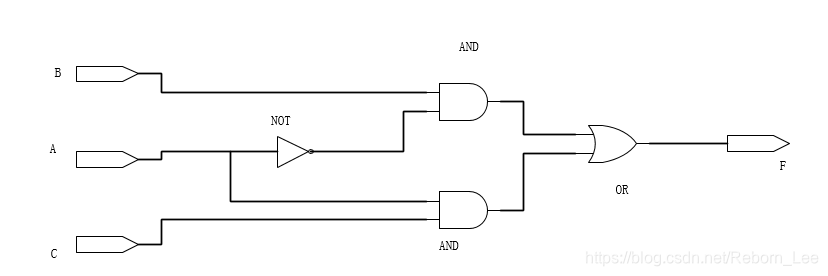

以这个电路为例:

B和C都是固定值,仅有A变化,属于仅有一个输入变化,但是请看到,A变化后紧接着两个与门的结果会变化,再到达或门,这又变成了有多个输入同时变化问题了。