门控时钟专题

0赞目录

门控时钟定义?

门控时钟,指的是由组合逻辑产生的时钟,其中,组合逻辑的输入可以全部是数据信号,也可以包含原始时钟信号。由于组合逻辑中的基本单元是与或非等门电路,而与门和非门又具有“开关性”,故该类时钟又称为门控时钟。

通常情况下,不建议使用门控时钟,因为门控时钟由组合逻辑产生,那么它本身就潜伏了组合逻辑的最大隐患——竞争和险象,所以门控时钟信号很容易产生毛刺,而寄存器等存储单元对时钟信号的边沿都非常敏感,因此具有毛刺的时钟会造成时序逻辑的不稳定。

到底要不要使用门控时钟?

上面建议尽量避免使用门控时钟,但是并不是一定不要使用门控时钟,对于某些功耗很大的系统而言,需要使用门控时钟来降低功耗。下面这段话来自于《FPGA深度解析》:

门控时钟可以有效地降低时钟网络的动态功耗,并且不会导致电路在工作时性能下降。在同步数字电路中,很多书籍不建议采用门控时钟进行电路设计。因为门控时钟会为电路设计带来不确定因素,造成工具在进行时序分析时无法分析门控时钟的行为。而言,即便如此,门控时钟能够动态地管理特定区域的时钟,并且同时影响该区域中的逻辑电路。因此,门控时钟被认为是降低芯片动态功耗的最佳方式之一,广泛应用于低功耗设计领域。

这段话说的,和上面说的尽量避免使用门控时钟并不矛盾,门控时钟应用的领域是低功耗设计领域。

门控时钟降低功耗的原理?

门控时钟也就是在使能信号有效的时候,把时钟打开,使能信号无效的时候,时钟关闭。时钟关闭之后,它所驱动的寄存器输出就会不变,因此也就降低了动态功耗。

所谓的动态功耗,是CMOS数字电路中功耗的一种,由于数字电路的基本元器件是基于CMOS工艺的,而CMOS电路的功耗主要有三种,静态功耗,动态功耗以及状态跳变时,源漏间瞬时短路的功耗。对于动态功耗,即电路节点电平翻转时对负载电容的充放电功耗是主要的功耗源,当电路处于静态即状态保持不变时功耗很小。

因此,降低功耗的一种重要的思想是减少电路中冗余的状态翻转,使更多的电路处于静态而降低功耗。

在这里门控时钟有着广泛的应用,关闭了时序部件的时钟即可使之保持静态,同时以这些时序部件输出为输入信号的组合逻辑也将处于静态,因此门控时钟可以很好地关闭子模块或者子电路的目的。

门控时钟设计原理?

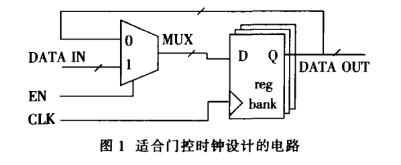

如下图1,是一个适合用门控时钟设计的电路,该电路在使能信号有效时,在时钟有效沿到来时,输出等于输入;当使能信号无效时,输出不变,这时随着时钟信号的翻转,电路中存在这冗余的开关动作,消耗额外的功率。

这种情况下可以在寄存器状态不需要改变时,关断它的时钟输入以达到降低功耗的目的,这就是门控时钟技术的设计思想。

既然如此,如何实现在寄存器状态不需要改变时,关断时钟输入呢?下面来探讨这个问题:

最容易想到的方法是:

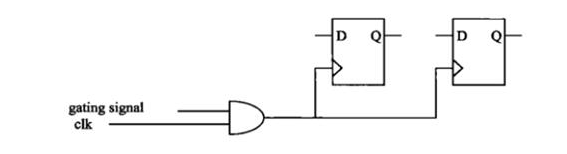

但似乎存在很多问题,时序方面的问题:

这里借图说话,来自于:数字设计中的时钟与约束

从波形图中可以看到,门控使能信号如果在时钟的高电平的时候开启或者关闭,就会导致产生的门控时钟高电平被截断,变成毛刺;门控使能信号对在时钟低电平时跳变对产生的门控时钟没有影响。因此我们的针对点就是高电平时的翻转。

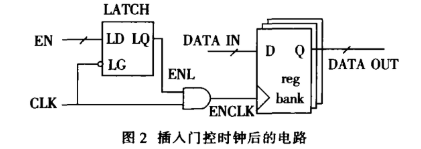

如下电路上述电路的改进,上述的分析很容易让我们想到使用锁存器可以解决这个毛刺的问题:(锁存器,低电平跟随,高电平保持)

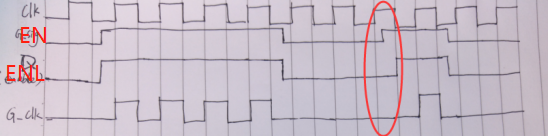

借图说话,时序如下:

时钟高电平时EN变化是关键,如上时序图中的红圈部分,由于加入了锁存器,时钟高电平锁存器保持EN之前的值,所以此时的EN变化无效,直到时钟低电平到来为止,这样就避免了生成的最终门控时钟高电平过窄(毛刺)问题。

有上述时序图可知,生成的门控时钟没有毛刺了。

最后有必要说明:一般情况,在进行芯片设计的时候,我们不必自己设计门控时钟,大多是ASIC/SoC生产商都有对应的门控时钟单元。

参考文献?

FPGA深度解析

FPGA之道

高性能FPGA系统——时序设计与分析