MP5652(A10)核心板用户手册及使用说明

0赞一、 开发板简介

1.1 产品简介

MP5652(A10)核心板采用Intel公司Arria-10 GX系列的10AX027H4F34I3SG作为主控制器,核心板采用4个0.5mm间距120Pin 镀金连接器与母板连接,核心板四个脚放置了4个3.5mm固定孔,此孔可以与底板通过螺丝紧固,确保了在强烈震动的环境下稳定运行。

这款MP5652核心板能够方便用户对核心板的二次开发利用。核心板使用Intel的Arria-10 GX芯片的解决方案,在FPGA 芯片的HP 端口上挂载了4片DDR4存储芯片,每片DDR4 容量高达4Gb(256Mb x 16) 字节,每片16bit组成64bit 位的数据位宽。1片1GB 的QSPI FLASH 芯片用来静态存储FPGA 芯片的配置文件或者其它用户数据。

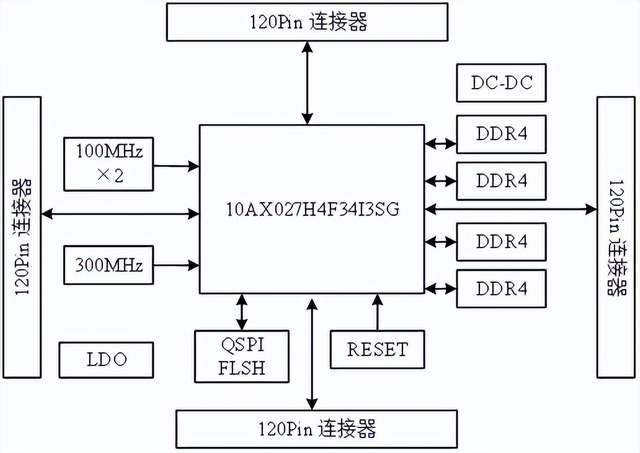

整个开发系统的结构示意图如下图所示:

通过以上示意图,我们可以看到,我们这个核心板开发平台所能含有的接口和功能。

这款核心板的4个板对板连接器扩展出了244个IO,其中BANK2A、BANK2K、BANK2J、BANK3D的全部IO的电平可以通过更换核心板上的磁珠来修改,满足用户对+1.8V、+1.2V电平接口的需求,默认+1.8V;BANK2J的全部IO的电平也可以通过更换核心板上的磁珠来修改,满足用户对+3.0V、+2.5V、+1.8、+1.2V电平接口的需求,默认+3.0V;另外核心板也扩展出了16对高速收发器17.4 Gbps Transceiver接口。对于需要大量IO的用户,此核心板将是不错的选择。而且IO连接部分,同一个BANK管脚到连接器接口之间走线做了等长和差分处理,对于二次开发来说,非常适合。

1.2 产品规格

MP5652核心板规格 |

|

FPGA主控制器 |

10AX027H4F34I3SG |

DDR4 |

162Gb |

QSPI FLASH |

1GB |

启动方式 |

JTAG/QSPI FLASH |

用户RESET |

高电平复位 |

IO数量 |

244个(全部BANK电平可调) |

GTX接口数量 |

4个BANK、TX/RX共16对 |

工作电压/最大电流 |

5—12V/5A |

核心板尺寸、工艺 |

85Í65mm、沉金工艺 |

与底板扣接高度 |

3mm |

工作温度 |

-40°C~+85°C |

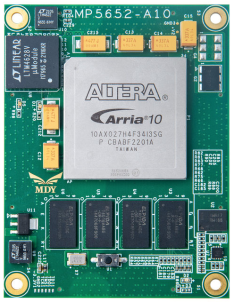

1.3产品外观

MP5652核心板正面照片

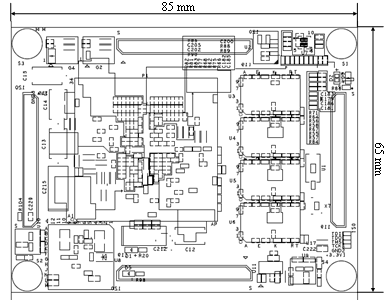

1.4产品结构尺寸图

核心板结构尺寸图:65(mm)x85(mm), PCB:14 层。

MP5650核心板尺寸图

二、 MP5652核心板使用手册详细介绍

2.1 FPGA芯片

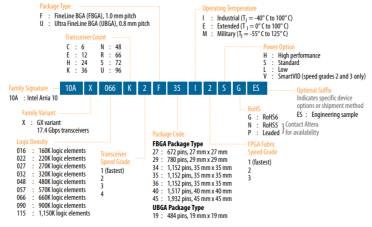

核心板使用的是Intel公司的Arria-10 GX芯片,芯片型号可选10AX027H4F34I3SG。速度等级为3,温度等级为工业级。此型号为FFG1152封装,1152个引脚,引脚间距为1.0mm。Intel Arria-10 GX FPGA的芯片命名规则如下图2-1所示:

图2-1 Arria-10 GX系列芯片命名规则

Arria-10 GX 10AX027H4F34I3SG的主要参数表

名称 |

详细参数 |

Pin(I/O) |

1152 |

Logic Elements (LE) (K) |

270 |

ALM |

101,620 |

Register |

406,480 |

Memory M20K (Kb) |

15,000 |

DSP Block |

830 |

18 x 19 Multiplier |

1660 |

Transceiver |

124个, 17.4 Gbps |

GPIO |

384 |

LVDS Pair |

168 |

速度等级(Speed Grade) |

-3 (Mid) |

温度等级(Temperature Grade) |

I (工业级) |

2.2 DDR4 SDRAM

MP5652开发板上配有四片Micron Technology 的4 Gb的DDR4芯片,型号为EDY4016AABG-DR-F-D。每片DDR4 SDRAM数据位宽为16 bit,共组成64 bit的数据总线宽度。因为4片DDR4芯片连接到FPGA的BANK3B、BANK3C、BANK3D的接口上,DDR43 SDRAM的最高运行速度可达1200 MHz(数据速率2400 Mbps)。DDR4的具体配置如下表2-2-1所示。

表2-2-1 DDR4配置

位号 |

芯片型号 |

容量 |

厂家 |

U3,U4,U5,U6 |

EDY4016AABG-DR-F-D |

256Mb Í 16bit |

Micron Technology |

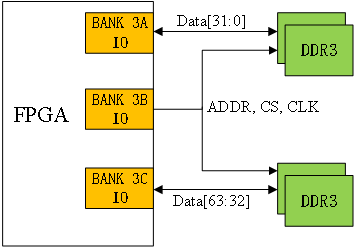

核心板的DDR4的接口的设计示意图如下图所示:

核心板采用高速布线,DDR4 的硬件设计需要严格考虑信号完整性,开发板的电路及PCB 设计已经充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,以确保DDR4 稳定工作。核心板的4片DDR4实物如下图所示:

4 片 DDR4 管脚分配配置如下 2-2-2 所示。

DDR3信号名称 |

FPGA 管脚名称 |

FPGA 管脚位号 |

DDR4_A0 |

IO_3B_43_AD4/LVDS3B_3N/DQ48 |

AD4 |

DDR4_A1 |

IO_3B_12_AH3/LVDS3B_18P/DQ53 |

AH3 |

DDR4_A10 |

IO_3B_39_AB5/LVDS3B_5N/DQ49 |

AB5 |

DDR4_A11 |

IO_3B_37_AC5/LVDS3B_6N/DQ49 |

AC5 |

DDR4_A12 |

IO_3B_19_AF3/PLL_3B_CLKOUT0N/LVDS3B_15N/DQ52 |

AF3 |

DDR4_A13 |

IO_3B_27_AE7/LVDS3B_11N/DQ51 |

AE7 |

DDR4_A14_WE_B |

IO_3B_47_AB11/LVDS3B_1N/DQ48 |

AB11 |

DDR4_A15_CAS_B |

IO_3B_28_AC8/PLL_3B_CLKOUT1P,PLL_3B_CLKOUT1,PLL_3B_FB1/LVDS3B_10P/DQS51 |

AC8 |

DDR4_A16_RAS_B |

IO_3B_38_AB6/LVDS3B_5P/DQ49 |

AB6 |

DDR4_A2 |

IO_3B_41_AB7/LVDS3B_4N/DQSN49 |

AB7 |

DDR4_A3 |

IO_3B_20_AG5/LVDS3B_14P/DQS52 |

AG5 |

DDR4_A4 |

IO_3B_17_AE1/LVDS3B_16N/DQSN53 |

AE1 |

DDR4_A5 |

IO_3B_7_AH4/LVDS3B_21N/DQ54 |

AH4 |

DDR4_A6 |

IO_3B_9_AH2/LVDS3B_20N/DQSN54 |

AH2 |

DDR4_A7 |

IO_3B_18_AF4/PLL_3B_CLKOUT0P,PLL_3B_CLKOUT0,PLL_3B_FB0/LVDS3B_15P/DQ52 |

AF4 |

DDR4_A8 |

IO_3B_40_AB8/LVDS3B_4P/DQS49 |

AB8 |

DDR4_A9 |

IO_3B_21_AF5/LVDS3B_14N/DQSN52 |

AF5 |

DDR4_ACT_B |

IO_3B_14_AG6/LVDS3B_17P/DQ53 |

AG6 |

DDR4_ALERT_B |

IO_3B_15_AF6/LVDS3B_17N/DQ53 |

AF6 |

DDR4_BA0 |

IO_3B_42_AE4/LVDS3B_3P/DQ48 |

AE4 |

DDR4_BA1 |

IO_3B_5_AK3/LVDS3B_22N/DQSN55 |

AK3 |

DDR4_BG0 |

IO_3B_29_AD9/PLL_3B_CLKOUT1N/LVDS3B_10N/DQSN51 |

AD9 |

DDR4_CK_C |

IO_3B_33_AD6/LVDS3B_8N/DQSN50 |

AD6 |

DDR4_CK_T |

IO_3B_32_AD5/LVDS3B_8P/DQS50 |

AD5 |

DDR4_CKE |

IO_3B_46_AB10/LVDS3B_1P/DQ48 |

AB10 |

DDR4_CS_B |

IO_3B_4_AK4/LVDS3B_22P/DQS55 |

AK4 |

DDR4_DM0 |

IO_3A_24_AJ9/CLK_3A_1P/LVDS3A_12P/DQ59 |

AJ9 |

DDR4_DM1 |

IO_3A_10_AP5/LVDS3A_19P/DQ62 |

AP5 |

DDR4_DM2 |

IO_3A_21_AK6/LVDS3A_14N/DQSN60 |

AK6 |

DDR4_DM3 |

IO_3A_37_AE11/LVDS3A_6N/DQ57 |

AE11 |

DDR4_DM4 |

IO_3C_24_W1/CLK_3C_1P/LVDS3C_12P/DQ43 |

W1 |

DDR4_DM5 |

IO_3C_12_AA5/LVDS3C_18P/DQ45 |

AA5 |

DDR4_DM6 |

IO_3C_21_Y9/LVDS3C_14N/DQSN44 |

Y9 |

DDR4_DM7 |

IO_3C_37_V4/LVDS3C_6N/DQ41 |

V4 |

DDR4_DQ0 |

IO_3A_2_AL9/LVDS3A_23P/DQ63 |

AL9 |

DDR4_DQ1 |

IO_3A_8_AP7/LVDS3A_20P/DQS62 |

AP7 |

DDR4_DQ10 |

IO_3A_14_AM6/LVDS3A_17P/DQ61 |

AM6 |

DDR4_DQ11 |

IO_3A_20_AL6/LVDS3A_14P/DQS60 |

AL6 |

DDR4_DQ12 |

IO_3A_12_AP4/LVDS3A_18P/DQ61 |

AP4 |

DDR4_DQ13 |

IO_3A_15_AM5/LVDS3A_17N/DQ61 |

AM5 |

DDR4_DQ14 |

IO_3A_13_AN4/LVDS3A_18N/DQ61 |

AN4 |

DDR4_DQ15 |

IO_3A_19_AL3/PLL_3A_CLKOUT0N/LVDS3A_15N/DQ60 |

AL3 |

DDR4_DQ16 |

IO_3A_27_AJ6/LVDS3A_11N/DQ59 |

AJ6 |

DDR4_DQ17 |

IO_3A_30_AK7/LVDS3A_9P/DQ58 |

AK7 |

DDR4_DQ18 |

IO_3A_29_AH5/PLL_3A_CLKOUT1N/LVDS3A_10N/DQSN59 |

AH5 |

DDR4_DQ19 |

IO_3A_34_AH8/LVDS3A_7P/DQ58 |

AH8 |

DDR4_DQ2 |

IO_3A_0_AN7/LVDS3A_24P/DQ63 |

AN7 |

DDR4_DQ20 |

IO_3A_28_AJ5/PLL_3A_CLKOUT1P,PLL_3A_CLKOUT1,PLL_3A_FB1/LVDS3A_10P/DQS59 |

AJ5 |

DDR4_DQ21 |

IO_3A_31_AK8/LVDS3A_9N/DQ58 |

AK8 |

DDR4_DQ22 |

IO_3A_35_AG8/LVDS3A_7N/DQ58 |

AG8 |

DDR4_DQ23 |

IO_3A_36_AE12/LVDS3A_6P/DQ57 |

AE12 |

DDR4_DQ24 |

IO_3A_38_AF11/LVDS3A_5P/DQ57 |

AF11 |

DDR4_DQ25 |

IO_3A_45_AE8/LVDS3A_2N/DQSN56 |

AE8 |

DDR4_DQ26 |

IO_3A_47_AE9/LVDS3A_1N/DQ56 |

AE9 |

DDR4_DQ27 |

IO_3A_43_AH9/LVDS3A_3N/DQ56 |

AH9 |

DDR4_DQ28 |

IO_3A_39_AG11/LVDS3A_5N/DQ57 |

AG11 |

DDR4_DQ29 |

IO_3A_44_AF8/LVDS3A_2P/DQS56 |

AF8 |

DDR4_DQ3 |

IO_3A_9_AP6/LVDS3A_20N/DQSN62 |

AP6 |

DDR4_DQ30 |

IO_3A_46_AF9/LVDS3A_1P/DQ56 |

AF9 |

DDR4_DQ31 |

IO_3A_42_AH10/LVDS3A_3P/DQ56 |

AH10 |

DDR4_DQ32 |

IO_3C_2_Y1/LVDS3C_23P/DQ47 |

Y1 |

DDR4_DQ33 |

IO_3C_11_Y4/LVDS3C_19N/DQ46 |

Y4 |

DDR4_DQ34 |

IO_3C_0_AB1/LVDS3C_24P/DQ47 |

AB1 |

DDR4_DQ35 |

IO_3C_6_AB2/LVDS3C_21P/DQ46 |

AB2 |

DDR4_DQ36 |

IO_3C_3_Y2/LVDS3C_23N/DQ47 |

Y2 |

DDR4_DQ37 |

IO_3C_7_AB3/LVDS3C_21N/DQ46 |

AB3 |

DDR4_DQ38 |

IO_3C_1_AA1/LVDS3C_24N/DQ47 |

AA1 |

DDR4_DQ39 |

IO_3C_10_Y3/LVDS3C_19P/DQ46 |

Y3 |

DDR4_DQ4 |

IO_3A_3_AL8/LVDS3A_23N/DQ63 |

AL8 |

DDR4_DQ40 |

IO_3C_15_AA9/LVDS3C_17N/DQ45 |

AA9 |

DDR4_DQ41 |

IO_3C_18_W4/PLL_3C_CLKOUT0P,PLL_3C_CLKOUT0,PLL_3C_FB0/LVDS3C_15P/DQ44 |

W4 |

DDR4_DQ42 |

IO_3C_14_AA8/LVDS3C_17P/DQ45 |

AA8 |

DDR4_DQ43 |

IO_3C_17_W7/LVDS3C_16N/DQSN45 |

W7 |

DDR4_DQ44 |

IO_3C_16_W6/LVDS3C_16P/DQS45 |

W6 |

DDR4_DQ45 |

IO_3C_19_W5/PLL_3C_CLKOUT0N/LVDS3C_15N/DQ44 |

W5 |

DDR4_DQ46 |

IO_3C_13_AA6/LVDS3C_18N/DQ45 |

AA6 |

DDR4_DQ47 |

IO_3C_20_Y8/LVDS3C_14P/DQS44 |

Y8 |

DDR4_DQ48 |

IO_3C_30_U3/LVDS3C_9P/DQ42 |

U3 |

DDR4_DQ49 |

IO_3C_33_P1/LVDS3C_8N/DQSN42 |

P1 |

DDR4_DQ5 |

IO_3A_7_AM8/LVDS3A_21N/DQ62 |

AM8 |

DDR4_DQ50 |

IO_3C_27_U2/LVDS3C_11N/DQ43 |

U2 |

DDR4_DQ51 |

IO_3C_35_R2/LVDS3C_7N/DQ42 |

R2 |

DDR4_DQ52 |

IO_3C_32_R1/LVDS3C_8P/DQS42 |

R1 |

DDR4_DQ53 |

IO_3C_34_P2/LVDS3C_7P/DQ42 |

P2 |

DDR4_DQ54 |

IO_3C_31_V3/LVDS3C_9N/DQ42 |

V3 |

DDR4_DQ55 |

IO_3C_36_V5/LVDS3C_6P/DQ41 |

V5 |

DDR4_DQ56 |

IO_3C_44_P4/LVDS3C_2P/DQS40 |

P4 |

DDR4_DQ57 |

IO_3C_39_U5/LVDS3C_5N/DQ41 |

U5 |

DDR4_DQ58 |

IO_3C_45_P5/LVDS3C_2N/DQSN40 |

P5 |

DDR4_DQ59 |

IO_3C_38_U6/LVDS3C_5P/DQ41 |

U6 |

DDR4_DQ6 |

IO_3A_1_AM7/LVDS3A_24N/DQ63 |

AM7 |

DDR4_DQ60 |

IO_3C_43_R3/LVDS3C_3N/DQ40 |

R3 |

DDR4_DQ61 |

IO_3C_47_R4/LVDS3C_1N/DQ40 |

R4 |

DDR4_DQ62 |

IO_3C_42_T3/LVDS3C_3P/DQ40 |

T3 |

DDR4_DQ63 |

IO_3C_46_T4/LVDS3C_1P/DQ40 |

T4 |

DDR4_DQ7 |

IO_3A_6_AN8/LVDS3A_21P/DQ62 |

AN8 |

DDR4_DQ8 |

IO_3A_11_AN5/LVDS3A_19N/DQ62 |

AN5 |

DDR4_DQ9 |

IO_3A_18_AM3/PLL_3A_CLKOUT0P,PLL_3A_CLKOUT0,PLL_3A_FB0/LVDS3A_15P/DQ60 |

AM3 |

DDR4_DQS0_C |

IO_3A_5_AN9/LVDS3A_22N/DQSN63 |

AN9 |

DDR4_DQS0_T |

IO_3A_4_AP9/LVDS3A_22P/DQS63 |

AP9 |

DDR4_DQS1_C |

IO_3A_17_AM2/LVDS3A_16N/DQSN61 |

AM2 |

DDR4_DQS1_T |

IO_3A_16_AM1/LVDS3A_16P/DQS61 |

AM1 |

DDR4_DQS2_C |

IO_3A_33_AG7/LVDS3A_8N/DQSN58 |

AG7 |

DDR4_DQS2_T |

IO_3A_32_AH7/LVDS3A_8P/DQS58 |

AH7 |

DDR4_DQS3_C |

IO_3A_41_AF10/LVDS3A_4N/DQSN57 |

AF10 |

DDR4_DQS3_T |

IO_3A_40_AG10/LVDS3A_4P/DQS57 |

AG10 |

DDR4_DQS4_C |

IO_3C_5_AC2/LVDS3C_22N/DQSN47 |

AC2 |

DDR4_DQS4_T |

IO_3C_4_AC3/LVDS3C_22P/DQS47 |

AC3 |

DDR4_DQS5_C |

IO_3C_9_AA4/LVDS3C_20N/DQSN46 |

AA4 |

DDR4_DQS5_T |

IO_3C_8_AA3/LVDS3C_20P/DQS46 |

AA3 |

DDR4_DQS6_C |

IO_3C_29_T1/PLL_3C_CLKOUT1N/LVDS3C_10N/DQSN43 |

T1 |

DDR4_DQS6_T |

IO_3C_28_U1/PLL_3C_CLKOUT1P,PLL_3C_CLKOUT1,PLL_3C_FB1/LVDS3C_10P/DQS43 |

U1 |

DDR4_DQS7_C |

IO_3C_41_T6/LVDS3C_4N/DQSN41 |

T6 |

DDR4_DQS7_T |

IO_3C_40_T5/LVDS3C_4P/DQS41 |

T5 |

DDR4_ODT |

IO_3B_10_AG1/LVDS3B_19P/DQ54 |

AG1 |

DDR4_PAR |

IO_3B_30_AC9/LVDS3B_9P/DQ50 |

AC9 |

DDR4_RESET_B |

IO_3B_8_AJ1/LVDS3B_20P/DQS54 |

AJ1 |

DDR4_TEN |

IO_3B_16_AF1/LVDS3B_16P/DQS53 |

AF1 |

2.3 FPGA BANK接口电平选择

核心板上对外的BANK分别为BANK2A/2J/2K/3D, 这些BANK的IO均支持1.8V/1.2V两种电平可调,默认电平为1.8V。BANK2L, 这些BANK的IO均支持3.0V/2.5V/1.8V/1.2V四种电平可调,默认电平为3.0V。如果需要更换电平,只需要更换对应位置磁珠即可实现调整,核心板BANK电平调节磁珠位置,如下表2-2-3所示。

表2-2-3 BANK电平调节磁珠位号

FPGA BANK |

+3.0V |

+2.5V |

+1.8V |

+1.2V |

BANK2A |

L10 |

L11 |

||

BANK2J |

L12 |

L9 |

||

BANK2K |

L13 |

L14 |

||

BANK3D |

L15 |

L16 |

||

BANK2L |

L5 |

L6 |

L7 |

L8 |

2.4 QSPI Flash

开发板配有一片1Gb大小的Quad-SPI Flash芯片,型号为MT25QU01GBBB8E12-0SIT,它使用1.8V CMOS电压标准。由于QSPI FLASH的非易失特性,在使用中,它可以存储FPGA的配置Bin文件以及其它的用户数据文件。

Part Number |

Org |

Temperature |

MaxClock (MHz) |

Package |

MT25QU01GBBB8E12-0SIT |

1Gbit |

-40℃to +85℃ |

108 |

TBGA24 |

开发板的QSPI的设计示意图如下图所示:

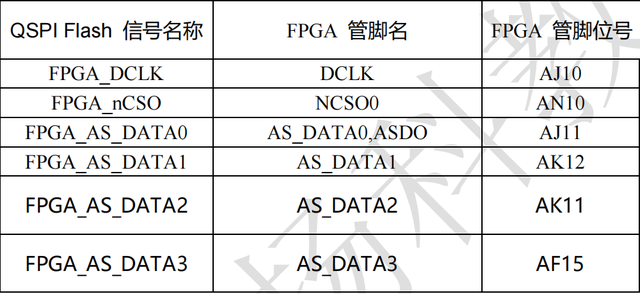

QSPI Flash 管脚分配配置表如表 2-2-4 所示。

表 2-2-4 QSPI Flash 管脚配置表

2.5 核心板时钟

MP5652核心板为了准确适配不同用途的时钟频率,板载多个时钟源。其中包括100MHz的系统时钟源510KBA100M000BAG CMOS晶振,125MHz的Transceiver差分时钟源SiT9102晶振, 300 MHz的DDR4的外部差分时钟源SiT9102晶振。SiT9102是一款高精度、超低相噪的晶振,非常适合作为高速信号处理系统的时钟源。最后,为了缩短大容量FPGA芯片的下载配置时间,板卡还配有100MHz的初始化时钟源510KBA100M000BAG CMOS晶振,连接CLKUSR 引脚,用户可以配置使用该时钟,配合QSPI×4模式,从而大大提高FPGA的配置效率。

2.5.1 FPGA 系统时钟源

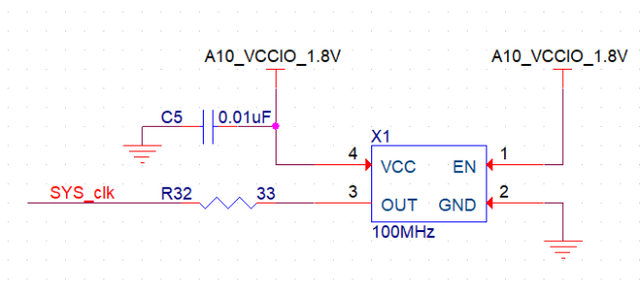

板上提供了一个单端100 MHz 的FPGA 系统时钟源,晶振输出连接到FPGA BANK3D 的全局时钟,这个全局时钟可以用来驱动FPGA 内的用户逻辑电路。该时钟源的原理图如下图所示。

系统时钟引脚分配:

信号名称 |

FPGA 管脚位号 |

SYS_clk |

K6 |

2.5.2 Transceiver时钟

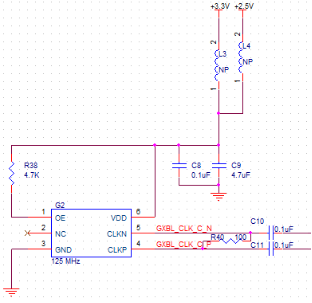

核心板上为Transceiver收发器提供了125MHz的参考时钟。参考时钟连接到BANKGXBL1E。该时钟源的原理图如下图所示。

BANKGXBL1E时钟源FPGA引脚配置

信号名称 |

FPGA管脚位号 |

REFCLK_GXBL1E_CHTP_1E_T28 |

T28 |

REFCLK_GXBL1E_CHTN_1E_T27 |

T27 |

2.5.3 DDR4外部时钟

板上提供了一个300 MHz的DDR4的外部差分时钟源,型号为SiT9102晶振。SiT9102是一款高精度、超低相噪的晶振,非常适合作为高速信号处理系统的时钟源。该时钟源的原理图如下图所示。

DDR4时钟源FPGA引脚配置

信号名称 |

FPGA管脚位号 |

IO_3B_22_AE2/CLK_3B_0P/LVDS3B_13P |

AE2 |

IO_3B_23_AE3/CLK_3B_0N/LVDS3B_13N |

AE3 |

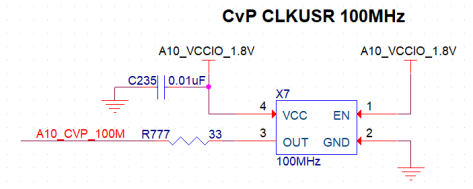

2.5.3 初始化时钟

核心板上还配有100MHz的初始化时钟源,型号为510KBA100M000BAG,输出电平为 CMOS,连接CLKUSR 引脚。该时钟源的原理图如下图所示。

初始化时钟源FPGA引脚配置

信号名称 |

FPGA 管脚位号 |

A10_CVP_100M |

AK16 |

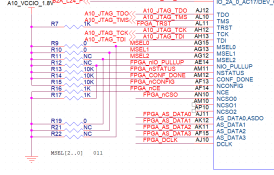

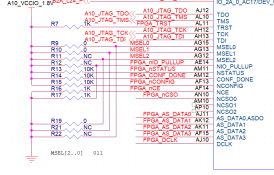

2.6 JTAG调试口

MP5652核心板板载了一个6PIN的贴片JTAG下载调试接口,方便用户单独调试FPGA。

核心板的JTAG接口连接示意如下图所示:

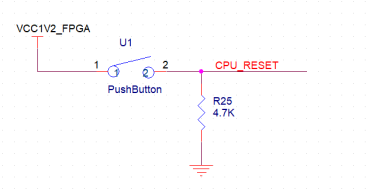

2.7 系统复位

MP5652核心板支持上电复位,复位整个芯片,同时配合按键也为系统提供全局复位信号。

通过按键U1实现全局复位,高电平复位。该管脚接在了BANK 3B的AJ4管脚上。

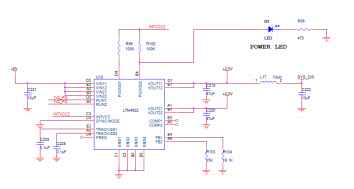

2.8 LED灯

核心板上有4个红色LED灯,其中1个是DDR4参考电源指示灯,当DDR4参考电源供电正常后,LED指示灯会亮起。1个是电源指示灯(POWER LED),上电成功电源指示灯会亮起。另外还有2个信号指示灯,与FPGA IO管脚直接相连,高电平灯亮。LED灯硬件连接的示意图如下图所示。

2.9 核心板电源

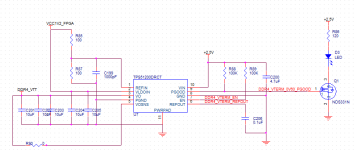

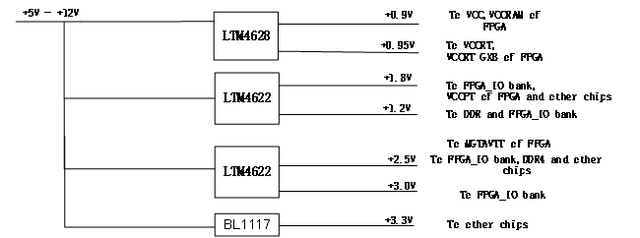

核心板集成电源管理,+5—+12V电源输入通过TI 电源芯片LTM4628 分别产生0.9V和0.95V的两路电源,其中一路为FPGA的核心提供稳定的电源,另一路为Transceiver GXB的VCCRT提供稳定的电源,LTM4628输出电流高达8A,满足FPGA电流需求。+5—+12V电源输入通过TI 电源芯片LTM4622分别产生+1.2V、+1.8V、+2.5V、+3.0V电压,单片LTM4622有两路电源输出,所以需要2片LTM4622。LTM4622为FPGA其他电源、DRR4、晶振、FLASH等供电。+5V电压经过BL1117转换为3.3V直流,为3.3V晶振提供电压。另外电源上电顺序按官方时序要求进行了控制。

核心板供电架构如下图所示:

电源分配如下表:

电源 |

供电区域 |

+0.9V |

FPGA INT内核电压、VCCRAM |

+0.95 |

VCCRT、VCCRT GXB |

ADJ_VCCIO |

FPGA BANK电压可调 |

+1.8V |

FPGA BANK电压、VCCPT、QSPI、晶振等 |

+1.2V |

DDR4、FPGA BANK电压 |

+2.5V |

DDR4、FPGA BANK电压 |

+3.0V |

FPGA BANK电压 |

+3.3V |

晶振 |

DDR_VTT |

0.6V |

2.11 核心板启动方式

核心板支持两种启动模式,分别是JTAG、QSPI Flash。默认为QSPI Flash启动。

2.12 连接器管脚定义

核心板一共扩展出4个高速扩展口,使用4个120Pin的板间连接器(J1~J4)和底板连接,连接器使用松下的AXK5A2137YG,对应底板的连接器型号为AXK6A2337YG。其中J1连接JTAG和BANK2A,BANK2J的IO, J2连接BANK2A,BANK2L、BANK3A、BANK3B、BANK3C、BANK3D的IO,J3连接BANK2K和BANK2L的IO和+5V电源,J4连接GXB的收发器信号。

J1连接器的引脚分配

J1管脚 |

信号名称 |

FPGA引脚号 |

J1管脚 |

信号名称 |

FPGA引脚号 |

1 |

B2A_L21_P |

AD19 |

61 |

B2J_L12_P |

AL27 |

2 |

B2A_L19_P |

AE16 |

62 |

B2J_L2_P |

AJ27 |

3 |

B2A_L21_N |

AE18 |

63 |

B2J_L12_N |

AL26 |

4 |

B2A_L19_N |

AE17 |

64 |

B2J_L2_N |

AH27 |

5 |

B2A_L10_P |

AL16 |

65 |

B2J_L21_P |

AJ24 |

6 |

B2A_L13_P |

AH18 |

66 |

B2J_L11_P |

AP25 |

7 |

B2A_L10_N |

AM16 |

67 |

B2J_L21_N |

AK24 |

8 |

B2A_L13_N |

AH19 |

68 |

B2J_L11_N |

AN25 |

9 |

GND |

69 |

GND |

||

10 |

GND |

70 |

GND |

||

11 |

B2A_L16_P |

AJ17 |

71 |

B2J_L7_P |

AN27 |

12 |

B2A_L15_P |

AG17 |

72 |

B2J_L14_P |

AL24 |

13 |

B2A_L16_N |

AK17 |

73 |

B2J_L7_N |

AM27 |

14 |

B2A_L15_N |

AH17 |

74 |

B2J_L14_N |

AL25 |

15 |

B2A_L8_P |

AM17 |

75 |

B2J_L18_P |

AN20 |

16 |

B2A_L20_P |

AG16 |

76 |

B2J_L8_P |

AP26 |

17 |

B2A_L8_N |

AN17 |

77 |

B2J_L18_N |

AP20 |

18 |

B2A_L20_N |

AF16 |

78 |

B2J_L8_N |

AP27 |

19 |

GND |

79 |

GND |

||

20 |

GND |

80 |

GND |

||

21 |

B2A_L2_P |

AP16 |

81 |

B2J_L17_P |

AM23 |

22 |

B2A_L7_P |

AM18 |

82 |

B2J_L9_P |

AK27 |

23 |

B2A_L2_N |

AP17 |

83 |

B2J_L17_N |

AN23 |

24 |

B2A_L7_N |

AN18 |

84 |

B2J_L9_N |

AK26 |

25 |

B2A_L3_P |

AN15 |

85 |

B2J_L23_P |

AL23 |

26 |

B2A_L12_P |

AM15 |

86 |

B2J_L16_P |

AM22 |

27 |

B2A_L3_N |

AP15 |

87 |

B2J_L23_N |

AK23 |

28 |

B2A_L12_N |

AL15 |

88 |

B2J_L16_N |

AN22 |

29 |

GND |

89 |

GND |

||

30 |

GND |

90 |

GND |

||

31 |

B2A_L4_P |

AN13 |

91 |

B2J_L13_P |

AN24 |

32 |

B2A_L14_P |

AJ14 |

92 |

B2J_L6_P |

AC24 |

33 |

B2A_L4_N |

AM13 |

93 |

B2J_L13_N |

AP24 |

34 |

B2A_L14_N |

AH14 |

94 |

B2J_L6_N |

AD24 |

35 |

B2A_L6_P |

AN14 |

95 |

B2J_L24_P |

AJ22 |

36 |

B2A_L9_P |

AL14 |

96 |

B2J_L10_P |

AM25 |

37 |

B2A_L6_N |

AP14 |

97 |

B2J_L24_N |

AK22 |

38 |

B2A_L9_N |

AK14 |

98 |

B2J_L10_N |

AM26 |

39 |

GND |

99 |

GND |

||

40 |

GND |

100 |

GND |

||

41 |

B2A_L1_P |

AL13 |

101 |

B2J_L3_P |

AJ26 |

42 |

B2A_L17_P |

AJ15 |

102 |

B2J_L1_P |

AE24 |

43 |

B2A_L1_N |

AK13 |

103 |

B2J_L3_N |

AH26 |

44 |

B2A_L17_N |

AH15 |

104 |

B2J_L1_N |

AD25 |

45 |

B2A_L5_P |

AN12 |

105 |

B2J_L22_P |

AH23 |

46 |

106 |

B2J_L20_P |

AF23 |

||

47 |

B2A_L5_N |

AP12 |

107 |

B2J_L22_N |

AH24 |

48 |

108 |

B2J_L20_N |

AG23 |

||

49 |

GND |

109 |

GND |

||

50 |

GND |

110 |

GND |

||

51 |

B2J_L4_P |

AG25 |

111 |

||

52 |

B2J_L5_P |

AJ25 |

112 |

A10_JTAG_TCK |

AH12 |

53 |

B2J_L4_N |

AF25 |

113 |

||

54 |

B2J_L5_N |

AH25 |

114 |

A10_JTAG_TMS |

AL10 |

55 |

B2J_L15_P |

AP21 |

115 |

||

56 |

B2J_L19_P |

AF24 |

116 |

A10_JTAG_TDO |

AJ12 |

57 |

B2J_L15_N |

AP22 |

117 |

||

58 |

B2J_L19_N |

AE23 |

118 |

A10_JTAG_TDI |

AH13 |

59 |

GND |

119 |

GND |

||

60 |

GND |

120 |

GND |

J2连接器的引脚分配

J2管脚 |

信号名称 |

FPGA引脚号 |

J2管脚 |

信号名称 |

FPGA引脚号 |

1 |

B2L_3 |

L18 |

61 |

||

2 |

62 |

||||

3 |

B2L_2 |

K18 |

63 |

||

4 |

64 |

||||

5 |

B2L_1 |

M18 |

65 |

||

6 |

B3D_L1_P |

T9 |

66 |

||

7 |

B2L_0 |

M17 |

67 |

||

8 |

B3D_L1_N |

R9 |

68 |

||

9 |

GND |

69 |

GND |

||

10 |

GND |

70 |

GND |

||

11 |

71 |

B3D_L3_P |

V7 |

||

12 |

B3D_L24_P |

M1 |

72 |

B3D_L23_P |

K1 |

13 |

73 |

B3D_L3_N |

U7 |

||

14 |

B3D_L24_N |

L1 |

74 |

B3D_L23_N |

K2 |

15 |

75 |

B3D_L21_P |

L3 |

||

16 |

76 |

B3D_L22_P |

J1 |

||

17 |

77 |

B3D_L21_N |

K3 |

||

18 |

78 |

B3D_L22_N |

J2 |

||

19 |

GND |

79 |

GND |

||

20 |

GND |

80 |

GND |

||

21 |

B3D_L2_P |

U8 |

81 |

B3D_L20_P |

N2 |

22 |

B3D_L6_P |

W10 |

82 |

B3D_L19_P |

M2 |

23 |

B3D_L2_N |

T8 |

83 |

B3D_L20_N |

N3 |

24 |

B3D_L6_N |

W9 |

84 |

B3D_L19_N |

M3 |

25 |

B3D_L10_P |

N8 |

85 |

B3D_L8_P |

N7 |

26 |

B3D_L5_P |

V9 |

86 |

B3D_L18_P |

L4 |

27 |

B3D_L10_N |

M8 |

87 |

B3D_L8_N |

P7 |

28 |

B3D_L5_N |

V8 |

88 |

B3D_L18_N |

K4 |

29 |

GND |

89 |

GND |

||

30 |

GND |

90 |

GND |

||

31 |

91 |

B3B_L2_P |

AD2 |

||

32 |

92 |

B3C_L13_P |

Y6 |

||

33 |

93 |

B3B_L2_N |

AD1 |

||

34 |

94 |

B3C_L13_N |

Y7 |

||

35 |

95 |

B3D_L12_P |

R6 |

||

36 |

96 |

||||

37 |

97 |

B3D_L12_N |

P6 |

||

38 |

98 |

||||

39 |

GND |

99 |

GND |

||

40 |

GND |

100 |

GND |

||

41 |

B3D_L16_P |

J4 |

101 |

B3B_L7_P |

AD7 |

42 |

B3D_L4_P |

U10 |

102 |

B3B_L24_P |

AL1 |

43 |

B3D_L16_N |

J5 |

103 |

B3B_L7_N |

AC7 |

44 |

B3D_L4_N |

T10 |

104 |

B3B_L24_N |

AK1 |

45 |

B3D_L14_P |

M6 |

105 |

B3B_L12_P |

AD10 |

46 |

B3D_L15_P |

M5 |

106 |

B3B_L23_P |

AK2 |

47 |

B3D_L14_N |

M7 |

107 |

B3B_L12_N |

AD11 |

48 |

B3D_L15_N |

L5 |

108 |

B3B_L23_N |

AJ2 |

49 |

GND |

109 |

GND |

||

50 |

GND |

110 |

GND |

||

51 |

B3D_L17_P |

N4 |

111 |

B2A_L23_P |

AF18 |

52 |

B3D_L9_P |

R8 |

112 |

B3A_L13_P |

AL5 |

53 |

B3D_L17_N |

N5 |

113 |

B2A_L23_N |

AG18 |

54 |

B3D_L9_N |

R7 |

114 |

B3A_L13_N |

AL4 |

55 |

B3D_L7_P |

N9 |

115 |

B2A_L22_P |

AF19 |

56 |

B3D_L11_P |

K7 |

116 |

B2A_L24_P |

AC17 |

57 |

B3D_L7_N |

P9 |

117 |

B2A_L22_N |

AE19 |

58 |

B3D_L11_N |

L8 |

118 |

B2A_L24_N |

AD17 |

59 |

GND |

119 |

GND |

||

60 |

GND |

120 |

GND |

J3连接器的引脚分配

J3管脚 |

信号名称 |

FPGA引脚号 |

J3管脚 |

信号名称 |

FPGA引脚号 |

1 |

B2K_L19_P |

K23 |

61 |

B2L_15 |

H17 |

2 |

B2K_L24_P |

M24 |

62 |

B2L_8 |

K19 |

3 |

B2K_L19_N |

K22 |

63 |

B2L_12 |

J20 |

4 |

B2K_L24_N |

L24 |

64 |

B2L_14 |

J17 |

5 |

B2K_L15_P |

H24 |

65 |

B2L_21 |

G17 |

6 |

B2K_L23_P |

K24 |

66 |

B2L_26 |

G20 |

7 |

B2K_L15_N |

H23 |

67 |

B2L_36 |

C18 |

8 |

B2K_L23_N |

J24 |

68 |

B2L_30 |

F19 |

9 |

GND |

69 |

GND |

||

10 |

GND |

70 |

GND |

||

11 |

B2K_L17_P |

G23 |

71 |

B2L_20 |

F18 |

12 |

B2K_L2_P |

B26 |

72 |

B2L_37 |

D17 |

13 |

B2K_L17_N |

G22 |

73 |

B2L_31 |

E19 |

14 |

B2K_L2_N |

A26 |

74 |

B2L_45 |

B20 |

15 |

B2K_L13_P |

G26 |

75 |

B2L_47 |

D19 |

16 |

B2K_L20_P |

L23 |

76 |

B2L_39 |

B18 |

17 |

B2K_L13_N |

F26 |

77 |

B2L_46 |

C19 |

18 |

B2K_L20_N |

M23 |

78 |

B2L_38 |

A18 |

19 |

GND |

79 |

GND |

||

20 |

GND |

80 |

GND |

||

21 |

B2K_L8_P |

E26 |

81 |

B2L_40 |

A19 |

22 |

B2K_L3_P |

C27 |

82 |

B2L_43 |

A21 |

23 |

B2K_L8_N |

D26 |

83 |

B2L_41 |

A20 |

24 |

B2K_L3_N |

B27 |

84 |

B2L_44 |

B21 |

25 |

B2K_L12_P |

E23 |

85 |

B2L_28_PLL_1P |

E21 |

26 |

B2K_L4_P |

C24 |

86 |

B2L_24_L1_P |

E17 |

27 |

B2K_L12_N |

E24 |

87 |

B2L_29_PLL_1N |

D21 |

28 |

B2K_L4_N |

D24 |

88 |

B2L_25_L1_N |

E18 |

29 |

GND |

89 |

GND |

||

30 |

GND |

90 |

GND |

||

31 |

B2K_L22_P |

K25 |

91 |

B2L_22_L0_P |

J19 |

32 |

B2K_L18_P |

H27 |

92 |

B2L_18_PLL_0P |

G18 |

33 |

B2K_L22_N |

J25 |

93 |

B2L_23_L0_N |

H19 |

34 |

B2K_L18_N |

G27 |

94 |

B2L_19_PLL_0N |

H18 |

35 |

B2K_L14_P |

H22 |

95 |

B2L_42 |

B22 |

36 |

B2K_L7_P |

D25 |

96 |

B2L_33 |

C22 |

37 |

B2K_L14_N |

J22 |

97 |

B2L_34 |

C20 |

38 |

B2K_L7_N |

C25 |

98 |

B2L_16 |

G21 |

39 |

GND |

99 |

GND |

||

40 |

GND |

100 |

GND |

||

41 |

B2K_L9_P |

E22 |

101 |

B2L_35 |

D20 |

42 |

B2K_L10_P |

E27 |

102 |

B2L_13 |

H20 |

43 |

B2K_L9_N |

F23 |

103 |

B2L_17 |

F21 |

44 |

B2K_L10_N |

D27 |

104 |

B2L_7 |

J21 |

45 |

B2K_L16_P |

H25 |

105 |

B2L_32 |

D22 |

46 |

B2K_L6_P |

A23 |

106 |

B2L_6 |

K21 |

47 |

B2K_L16_N |

G25 |

107 |

B2L_27 |

F20 |

48 |

B2K_L6_N |

A24 |

108 |

B2L_11 |

M20 |

49 |

GND |

109 |

GND |

||

50 |

GND |

110 |

GND |

||

51 |

B2K_L1_P |

B23 |

111 |

POWER |

|

52 |

B2K_L21_P |

J27 |

112 |

POWER |

|

53 |

B2K_L1_N |

C23 |

113 |

POWER |

|

54 |

B2K_L21_N |

J26 |

114 |

POWER |

|

55 |

B2K_L11_P |

F25 |

115 |

POWER |

|

56 |

B2K_L5_P |

B25 |

116 |

POWER |

|

57 |

B2K_L11_N |

F24 |

117 |

POWER |

|

58 |

B2K_L5_N |

A25 |

118 |

POWER |

|

59 |

GND |

119 |

POWER |

||

60 |

GND |

120 |

POWER |

J4连接器的引脚分配

J4管脚 |

信号名称 |

FPGA引脚号 |

J4管脚 |

信号名称 |

FPGA引脚号 |

1 |

B1F_CLK1_P |

M28 |

61 |

B1D_CLK1_P |

Y28 |

2 |

B1F_RX0_P |

L30 |

62 |

B1D_TX1_P |

AG34 |

3 |

B1F_CLK1_N |

M27 |

63 |

B1D_CLK1_N |

Y27 |

4 |

B1F_RX0_N |

L29 |

64 |

B1D_TX1_N |

AG33 |

5 |

GND |

65 |

GND |

||

6 |

GND |

66 |

GND |

||

7 |

B1F_RX5_P |

C30 |

67 |

B1D_RX0_P |

AC30 |

8 |

B1F_TX0_P |

E34 |

68 |

B1D_TX0_P |

AJ34 |

9 |

B1F_RX5_N |

C29 |

69 |

B1D_RX0_N |

AC29 |

10 |

B1F_TX0_N |

E33 |

70 |

B1D_TX0_N |

AJ33 |

11 |

GND |

71 |

GND |

||

12 |

GND |

72 |

GND |

||

13 |

B1F_TX4_P |

D32 |

73 |

B1D_CLK0_P |

AB28 |

14 |

B1F_RX4_P |

E30 |

74 |

B1D_RX4_P |

W30 |

15 |

B1F_TX4_N |

D31 |

75 |

B1D_CLK0_N |

AB27 |

16 |

B1F_RX4_N |

E29 |

76 |

B1D_RX4_N |

W29 |

17 |

GND |

77 |

GND |

||

18 |

GND |

78 |

GND |

||

19 |

B1F_TX5_P |

B32 |

79 |

B1D_RX1_P |

AB32 |

20 |

B1F_TX1_P |

C34 |

80 |

B1D_TX4_P |

AA34 |

21 |

B1F_TX5_N |

B31 |

81 |

B1D_RX1_N |

AB31 |

22 |

B1F_TX1_N |

C33 |

82 |

B1D_TX4_N |

AA33 |

23 |

GND |

83 |

GND |

||

24 |

GND |

84 |

GND |

||

25 |

B1F_CLK0_P |

P28 |

85 |

B1D_RX5_P |

V32 |

26 |

B1F_RX1_P |

K32 |

86 |

B1D_TX5_P |

W34 |

27 |

B1F_CLK0_N |

P27 |

87 |

B1D_RX5_N |

V31 |

28 |

B1F_RX1_N |

K31 |

88 |

B1D_TX5_N |

W33 |

29 |

GND |

89 |

GND |

||

30 |

GND |

90 |

GND |

||

31 |

B1E_RX0_P |

U30 |

91 |

B1C_TX4_P |

AN34 |

32 |

B1E_TX0_P |

U34 |

92 |

B1C_CLK1_P |

AD28 |

33 |

B1E_RX0_N |

U29 |

93 |

B1C_TX4_N |

AN33 |

34 |

B1E_TX0_N |

U33 |

94 |

B1C_CLK1_N |

AD27 |

35 |

GND |

95 |

GND |

||

36 |

GND |

96 |

GND |

||

37 |

B1E_RX1_P |

T32 |

97 |

B1C_TX5_P |

AL34 |

38 |

B1E_TX4_P |

J34 |

98 |

B1C_RX1_P |

AJ30 |

39 |

B1E_RX1_N |

T31 |

99 |

B1C_TX5_N |

AL33 |

40 |

B1E_TX4_N |

J33 |

100 |

B1C_RX1_N |

AJ29 |

41 |

GND |

101 |

GND |

||

42 |

GND |

102 |

GND |

||

43 |

B1E_RX4_P |

N30 |

103 |

B1C_TX0_P |

AP32 |

44 |

B1E_TX5_P |

G34 |

104 |

B1C_CLK0_P |

AF28 |

45 |

B1E_RX4_N |

N29 |

105 |

B1C_TX0_N |

AP31 |

46 |

B1E_TX5_N |

G33 |

106 |

B1C_CLK0_N |

AF27 |

47 |

GND |

107 |

GND |

||

48 |

GND |

108 |

GND |

||

49 |

B1E_TX1_P |

R34 |

109 |

B1C_TX1_P |

AM32 |

50 |

B1E_CLK0_P |

V28 |

110 |

B1C_RX4_P |

AE30 |

51 |

B1E_TX1_N |

R33 |

111 |

B1C_TX1_N |

AM31 |

52 |

B1E_CLK0_N |

V27 |

112 |

B1C_RX4_N |

AE29 |

53 |

GND |

113 |

GND |

||

54 |

GND |

114 |

GND |

||

55 |

B1E_RX5_P |

M32 |

115 |

B1C_RX0_P |

AL30 |

56 |

116 |

B1C_RX5_P |

AD32 |

||

57 |

B1E_RX5_N |

M31 |

117 |

B1C_RX0_N |

AL29 |

58 |

118 |

B1C_RX5_N |

AD31 |

||

59 |

GND |

119 |

GND |

||

60 |

GND |

120 |

GND |

一、 底板设计注意事项

3.1电源部分PCB设计

电源输入需要铺铜皮连接,打足够的过孔保证通电流能力,但电源电压较高,干扰较大,在保证通流的条件下不要让这个铜皮更大,以免干扰其他信号。GND管脚需要连接到地平面上,且一个地管脚需要打两个过孔,保证通流和充分连接。

3.2高速接口布局走线

3.2.1千兆以太网:

与RJ45端连接的信号需要保持等长,RGMII接口的TX部分与RX部分需要单独保持等长。

3.2.2 HDMI接口

HDMI接口信号需要走差分,且差分之间需保持等长控制。

3.2.3 其他高速接口

依据接口规范控制。

3.3 LVDS信号

模组的BANK电平可以在+1.8V、+1.2V电平之间选择,默认为+1.8V电平。底板的LVDS信号走线需做差分/阻抗控制处理,并且差分之间保持等长。

3.4 GXB信号走线

GXB走线需要考虑的问题比较多,对于有疑问的用户可以联系客服接入技术支持。

想了解核心板更多资料的,可以添加微信:MDYfpga003